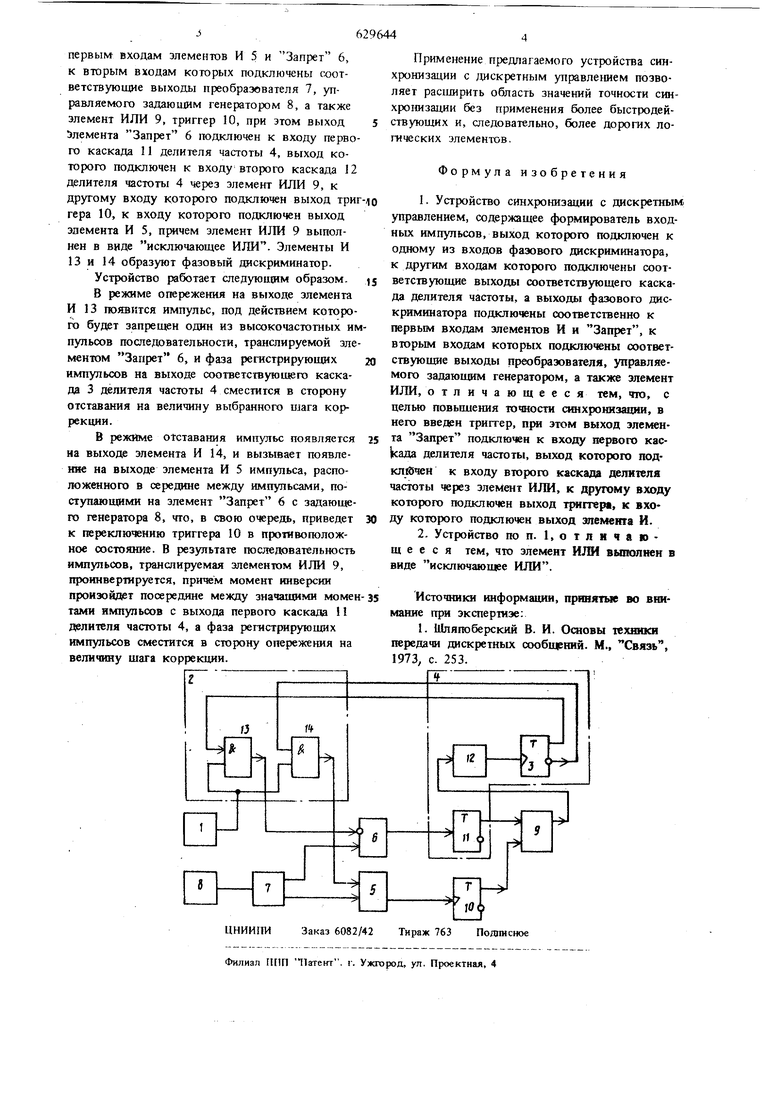

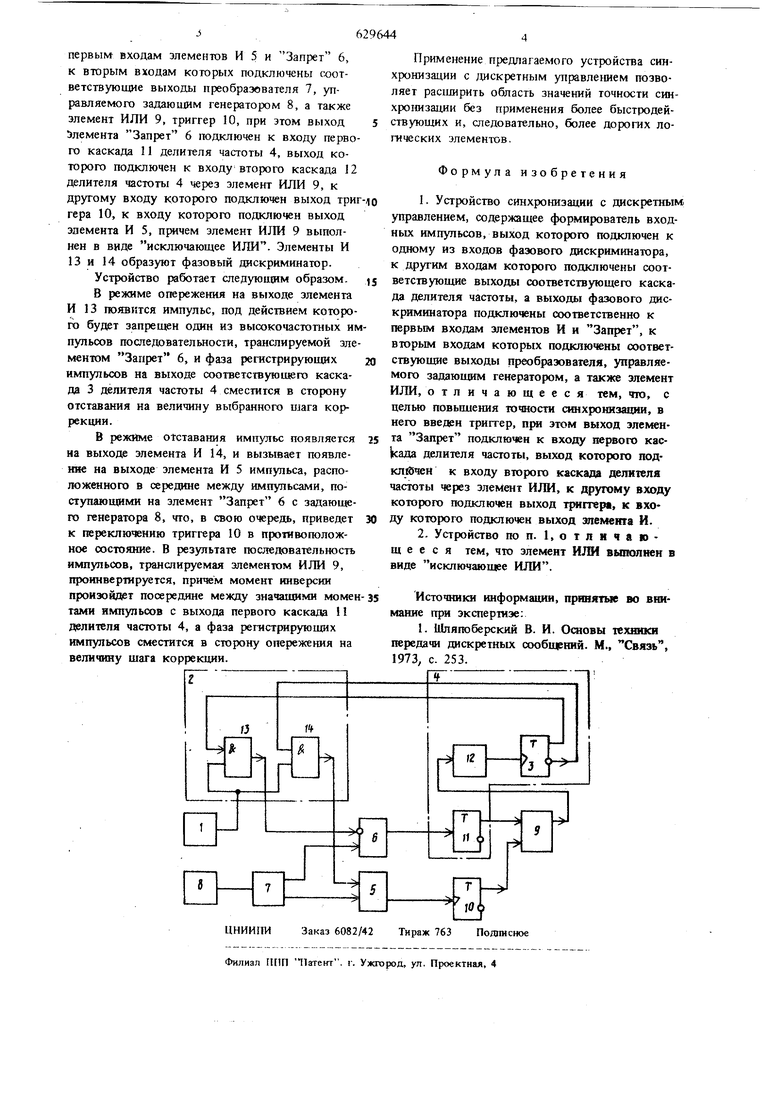

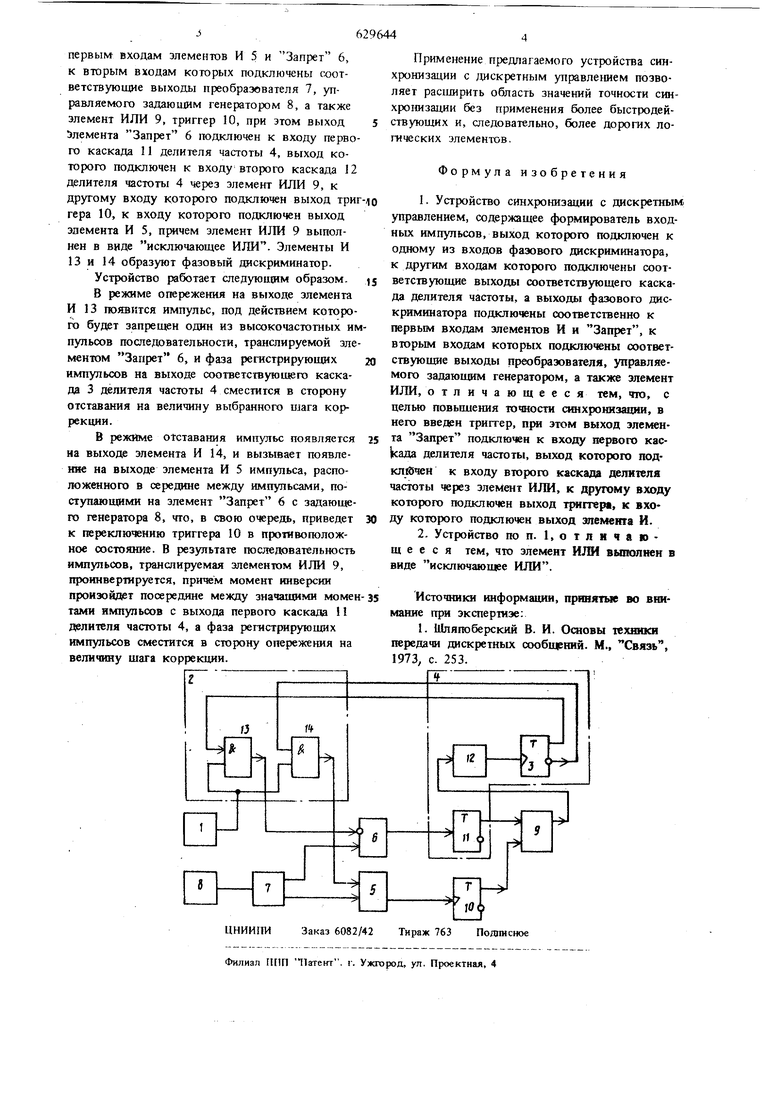

(54) УСТРОЙСТЮ СИНХГОНИЗАЦИИ С ДИСКРЕТНЫМ УПРАВЛЕНИЕМ первым входам элементов И 5 и Запрет 6, к вторым входам которых подключены одответствующие выходы преобразователя 7, управляемого задающим генератором 8, а также элемент ИЛИ 9, триггер 10, при этом выход Элемента Запрет 6 подключен к входу перво го каскада 11 делителя частоты 4, выход которого подключен к входу второго каскада 12 делителя частоты 4 через элемент ИЛИ 9, к другому входу которого подключен выход три гера 10, к входу которого подключен выход элемента И 5, причем элемент ИЛИ 9 выполнен в виде исключающее ИЛИ. Элементы И 13 и 14 образуют фазовый даскриминатор. Устройство работает следующим образом. В резкиме опережения на выходе элемента И 13 появится импульс, под действием которого будет запрещен один из высокочастотных им пульсов последовательности, транслируемой эле ментом Запрет 6, и фаза регистрирующих импульсов на выходе соответствующего каскада 3 делителя частоты 4 сместится в сторону отставания на величину выбранного шага коррекции. В режиме отставания импульс появляется на выходе элемента И 14, и вызывает появлеиие на выходе элемента И 5 импульса, расположенного в середане между импульсами, поступающими на элемент Запрет 6 с задающего генератора 8, что, в свою очередь, приведет к переключению триггера 10 в противоположное состояние. В результате последовательность импульсов, транслируемая элементом ИЛИ 9, проинвертаруется, причем момент инверсии произойдет посередине между значащими момен тами импульсов с выхода первого каскада 1 делителя частоты 4, а фаза регистрирующих импульсов сместится в сторону опережения на величину щага коррекщ1и. Применение предлагаемого устройства синхронизации с даскретным управлением позволяет распарить область значений точности синхронизации без применения более быстродействующих и, следовательно, более дорогих логических элементов. Формула изобретения 1. Устройство синхронизации с дискретным; управлением, содержащее формирователь входных импульсов, выход которого подключен к одному из входов фазового дискриминатора, к другим входам которого подключены соответствующие выходы соответствующего каскада делителя частоты, а выходы фазового дискриминатора подключены соответственно к первым входам элементов И и Запрет, к вторым входам которых подключены соответствующие выходы преобразователя, управляемого задающим генератором, а также элемент ИЛИ, отличающееся тем, по, с целью повьщ1ения точности синхронизации, в него введен триггер, при этом выход элемент Запрет подключен к входу первого кас|када делителя частоты, выход которого подклйчен к входу второго каскада делителя частоты через элемент ИЛИ, к другому входу которого подключен выход i rrepa, к вхоДУ которого подключен выход элемента И. 2. Устройство поп. 1,отлнчающ е е с я тем, что элемент ШШ выполнен в виде исключающее ИЛИ. Источники информации, принятые во внимание щт экспертизе; 1. Шля1юберский В. И. Основы техиики передачи дискретных сообщений. М., Связь, 1973, с. 253.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1981 |

|

SU970717A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1059689A1 |

| Способ синхронизации и устройстводля ЕгО ОСущЕСТВлЕНия | 1979 |

|

SU803113A1 |

| Устройство тактовой синхронизации | 1979 |

|

SU873444A1 |

| Устройство дискретной фазовой синхронизации | 1985 |

|

SU1338097A1 |

| Устройство синхронизации | 1981 |

|

SU1159173A1 |

| Фазовый дискриминатор | 1977 |

|

SU684712A1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ И РЕГЕНЕРАЦИИ ДЛЯ ТРАНСФОРМАТОРА СКОРОСТИ ДИСКРЕТНЫХ СИГНАЛОВ | 1971 |

|

SU321962A1 |

| Устройство дискретной автоподстройки фазы тактовых импульсов | 1983 |

|

SU1141581A1 |

| Цифровой управляемый генератор | 1989 |

|

SU1748247A1 |

Авторы

Даты

1978-10-25—Публикация

1977-04-28—Подача