(54) ФАЗОВЫЙ ДИСКРИМИНАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазовый дискриминатор | 1978 |

|

SU743163A1 |

| Устройство компенсации сдвига частот | 1985 |

|

SU1316097A2 |

| Устройство синхронизации | 1979 |

|

SU924890A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

| Устройство для тактовой синхронизации и регенерации дискретных сигналов | 1975 |

|

SU536610A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство автоподстройки фазы тактовых импульсов | 1983 |

|

SU1113893A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1059689A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство синхронизации с дискретным управлением | 1974 |

|

SU562935A1 |

Изобретение относится к электронной технике и предназначено для измерения сдвига фаз периодических сигналов при хаотическом пропадании одного из них и управления фазой синхронизируемого генератора в устройствах синхронизации.

Известен дискретный дискриминатор, предназначений для измерения сдвига фазы между периодическими сигналами и содержащий взаимосвязанные триггеры, схемы И и схемы ЗАПРЕТ 1J.

Однако этот дискриминатор может работать только при периодических сигналах.

Наиболее близким по технической сущности к предложенному является устройство, которое содержит взаимосвязанные триггеры, схему запрета, прецизионный формирователь длительности, выполненный на счетчике/ схемы И, И;Ш и ЗАПРЕТ (2).

Одчако это устройство громоздко, имеет большие габариты и в его состав входит прецизионный формировате длительности, выполненный, например на счетном устройстве.

Цель изобретения - уменьшение габаритов и веса прибора и повышение его точности.

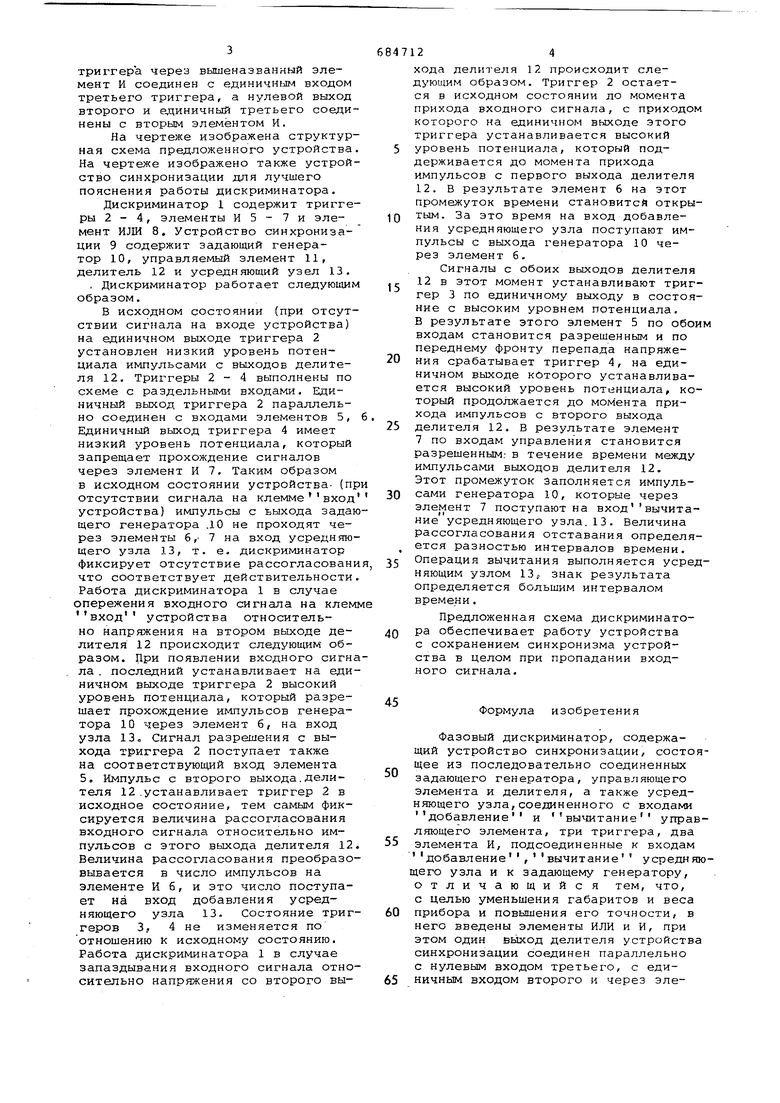

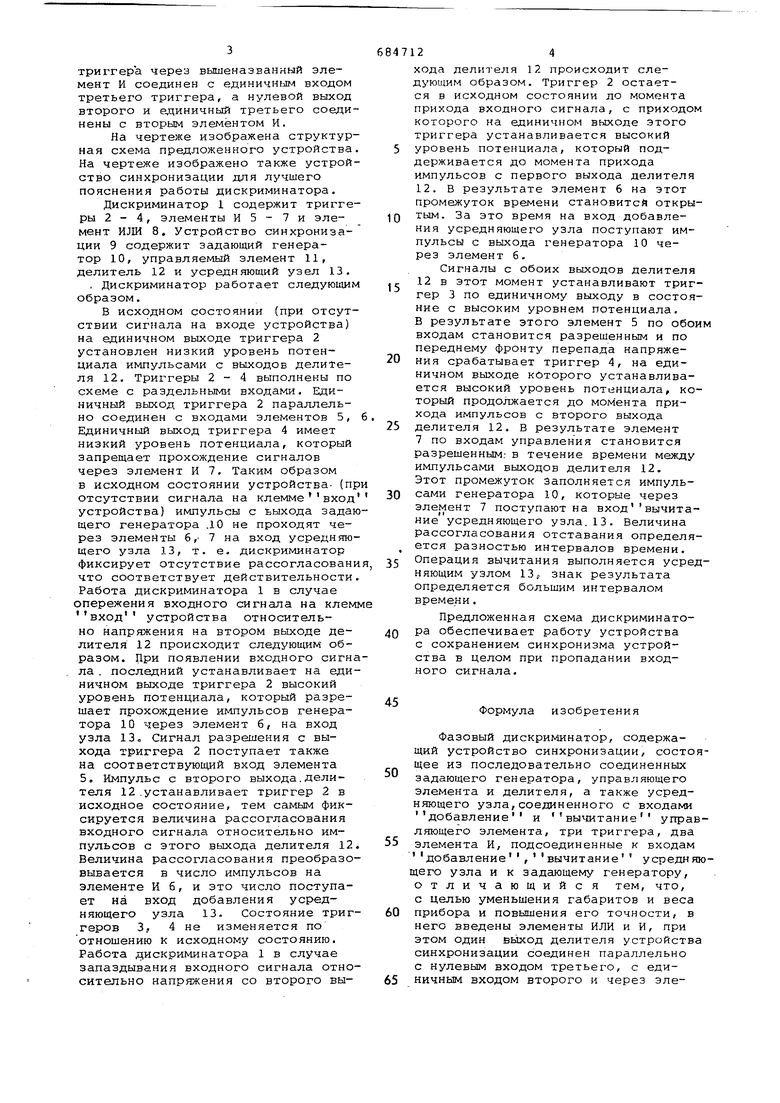

Для этого в фазовый дискриминатор содержащий устройство синхронизации, состоящее из последовательно соединенных задающего генератора, управляющего элемента и делителя, а также усредняющего узла, соединенного с входамидобавление и вычитани управляющего элемента, три триггера, два элемента И,подсоединенные к входа добавление,вычитание усредняющего узла и к задающему генератору, введены элементы ИЛИ и И. Один выход делителя устройства синхронизации соединен параллельно с нулевым входом третьего, с единичным входом второго и через элемент ИЛИ с нулевым входом первого триггера, а друго выход указанного делителя соединен параллельно с нулевым входом второго триггера и через элемент ИЛИ с нулевым входом первого триггера. Единичный выход первого триггера подключен к второму входу первого элемента И и через введенный элемент И - к единичному входу третьего тоиггера. Единичный выход второго триггера через вышеназванный элемент И соединен с единичИЕЛм входом третьего триггера, а нулевой выход второго и единичный третьего соеди нены с вторым элементом И. На чертеже изображена структур ная схема предложенного устройства На чертеже изображено также устрой ство синхронизации для лучшего пояснения работы дискриминатора. Дискриминатор 1 содержит тригге ры 2-4, элементы И 5 - 7 и элемент ИЛИ 8. Устройство синхронизации 9 содержит задающий генератор 10, управляемый элемент 11, делитель 12 и усредняющий узел 13. . Дискриминатор работает следующим образом. В исходном состоянии (при отсутствии сигнала на входе устройства) на единичном выходе триггера 2 установлен низкий уровень потенциала импульсами с выходов делителя 12. Триггеры 2-4 выполнены по схеме с раздельными входами. Единичный выход триггера 2 параллельно соединен с входами элементов 5, Единичный выход триггера 4 имеет низкий уровень потенциала, который запрещает прохождение сигналов через элемент И 7. Таким образом в исходном состоянии устройства- (п отсутствии сигнала на клемме вход устройства) импульсы с выхода зада щего генератора .10 не проходят через элементы 6,- 7 на вход усредняю щего узла 13, т. е. дискриминатор фиксирует отсутствие рассогласован что соответствует действительности Работа дискриминатора 1 в случае опережения входного сигнала на клем вход устройства относительно напряжения на втором выходе делителя 12 происходит следующим образом. При появлении входного сигн ла . последний устанавливает на еди ничном выходе триггера 2 высокий уровень потенциала, который разрешает прохождение импульсов генератора 10 через элемент 6, на вход узла 13, Сигнал разрешения с выхода триггера 2 поступает также на соответствующий вход элемента 5, Импульс с второго выхода,делителя 12 .устанавливает триггер 2 в исходное состояние, тем самым фиксируется величина рассогласования входного сигнала относительно импульсов с этого выхода делителя 12 Величина рассогласования преобразо вывается в число импульсов на элементе И 6, и это число поступает на вход добавления усредняющего узла 13. Состояние триг геров 3, 4 не изменяется по отношению к исходному состоянию. Работа д;искриминатора 1 в случае запаздывания входного сигнала отно сительно напряжения со второго вы24хода делителя 12 происходит следующим образом. Триггер 2 остается в исходном состоянии до момента прихода входного сигнала, с приходом которого на единичном выходе этого триггера устанавливается высокий уровень потенциала, который поддерживается до момента прихода импульсов с первого выхода делителя 12. В результате элемент 6 на этот промежуток времени становится открытым. За это время на вход добавления усредняющего узла поступают импульсы с выхода генератора 10 через элемент 6. Сигналы с обоих выходов делителя 12 в этот момент устанавливают триггер 3 по единичному выходу в состояние с высоким уровнем потенциала. В результате этого элемент 5 по обоим входам становится разрешенным и по переднему фронту перепада напряжения срабатывает триггер 4, на единичном выходе которого устанавливается высокий уровень потенциала, который продо.пжается до момента прихода импульсов с второго выхода делителя 12. В результате элемент 7 по входам управления становится разрешенным; в течение времени между импульсами выходов делителя 12. Этот промежуток Заполняется импульсами генератора 10, которые через элемент 7 поступают на входвычитание усредняющего узла.13. Величина рассогласования отставания определяется разностью интервалов времени. Операция вычитания выполняется усредняющим узлом 13, знак результата определяется большим интервалом времени. Предложенная схема дискриминатоРа обеспечивает работу устройства с сохранением синхронизма устройства в целом при пропадании входного сигнала. Формула изобретения Фазовый дискриминатор, содержащий устройство синхронизации, состоящее из последовательно соединенных задающего генератора, управляющего элемента и делителя, а также усредняющего узла,соединенного с входами добавление и вы штaниe управляющего элемента, три триггера, два элемента И, подсоединенные к входам добавление,вычитание усредняюего узла и к задающему генератору, отличающийся тем, что, с целью уменьшения габаритов и веса прибора и повышения его точности, в него введены элементы ИЛИ и И, при этом Один выход делителя устройства синхронизации соединен параллельно с нулевым входом третьего, с единичным входом второго и через элемент ИЛИ - с нулевым входом первого триггера,а другой выход указанного делителя соединен параллельно с нулевым входом второго триггера и через элемент ИЛИ - с нулевым входом первого триггера, единичный выход первого триггера подключен к второму входу первого элемента И и через введенный элемент И - к еди ничному входу третьего триггера, единичный выход второго триггера через вышеназванный элемент И сое84712

динен с единичным входом третьего триггера, а нулевой выход второго и единичный третьего соединены с вторым элементом И.

Источники информации, принятые во внимание при экспертизе 5 1с Авторское свидетельство СССР 450113, кл. G 01 R 25/08, 1973.

Авторы

Даты

1979-09-05—Публикация

1977-03-23—Подача