Изобретенпе относится к вычислительной те.хнике, а более конкретно к преобразователям двоичных чисел в двоично-десятичные, которые исиользуются в цифровы.х вычислительных машинах.

Известны преобразователи двоичных чисел в двоично-десятичные, работающие ио принцииу накопления десятичных эквивалентов разрядов преобразуемого двоичного числа и содержащие двоичные и десятичные счетчики и дешифраторы, сумматоры, усилитель-формирователь, схемы выделения, вычитання и запоминания десятков, ключи 1.

Одпако такой преобразователь отлпчается сложностью схемы и может применяться только для преобразования целых двоичных чисел.

Наиболее близким по технической сущности к предложенному является преобразователь двоичных чисел в двоично-десятичные, содержащий триггер, подключенный выходом к одному из входов элемента И, другой вход которого подсоединен к входной шине, а выход - ко входу двоичного сметчика, двоично-десятичный счетчик 2.

Работа данного преобразователя происходит следующим образом.

Десятичный счетчик устанавливается п нуль. Счетные импульсы (СИ) поступают

на Б.чоды двоичного и десятичного счетчиков до переиолнення двоичного счетчика. С этого момента прохождение импульсов на входы счетчиков прекращается, так как имиульс с выхода двоичного счетчика изменяет состояние трнггера, вследствие чего элемент И закрывается. Результат преобразования фиксируется в десятичном счетчике.

В преобразователях такого рода момент окончания счета импульсов может определяться другим способом, а именно с помощью схемы сравнения на равенство в.ходного двоичиого кода и кода двоичного счетчика. Тогда оба счетчика перед началом преобразовання должны устанавливаться в нуль. Такое рещение, не меняя принципа работы преобразователя, позволяет исиользовать счетчики, не имеющие входов для занесения параллельного кода, например в интегральном исполнении.

Недостаток подобных преобразователей состоит в невозможности их применения для преобразования дробных чисел.

Цель изобретения - расширение дианазона преобразуемых чисел.

Поставленная цель достигается тем, что в преобразователь введены схема сравнения, аналнзатор двоичного кода и второй элемент И. Ниформапионньте входы преобразователя подключены к первой группе входов схемы сравнения, а ее вторая группа входов - к разрядным выходам двоичного счетчика, семь младшпх разрядов которого соединены с входами анализатора двоичного кода. Управляющий вход анализатора соедииеи с шииой установки режима, а выход - с одним из входов 37C;)urrj

элемента И, связанного другим входом :; выходом соответственно с входа.и двокчиого и двоично-десятичного счетчиков. Выход схемы сравнения подключен к управляющему входу триггера. Анализатор двоичного кода содержит три элемента II. группы входов которых являются входа:,и анализатора двоичного кода, а выходы подключены к входам элемента ИЛИ, которого служит выходом анализатора двоичного кода.

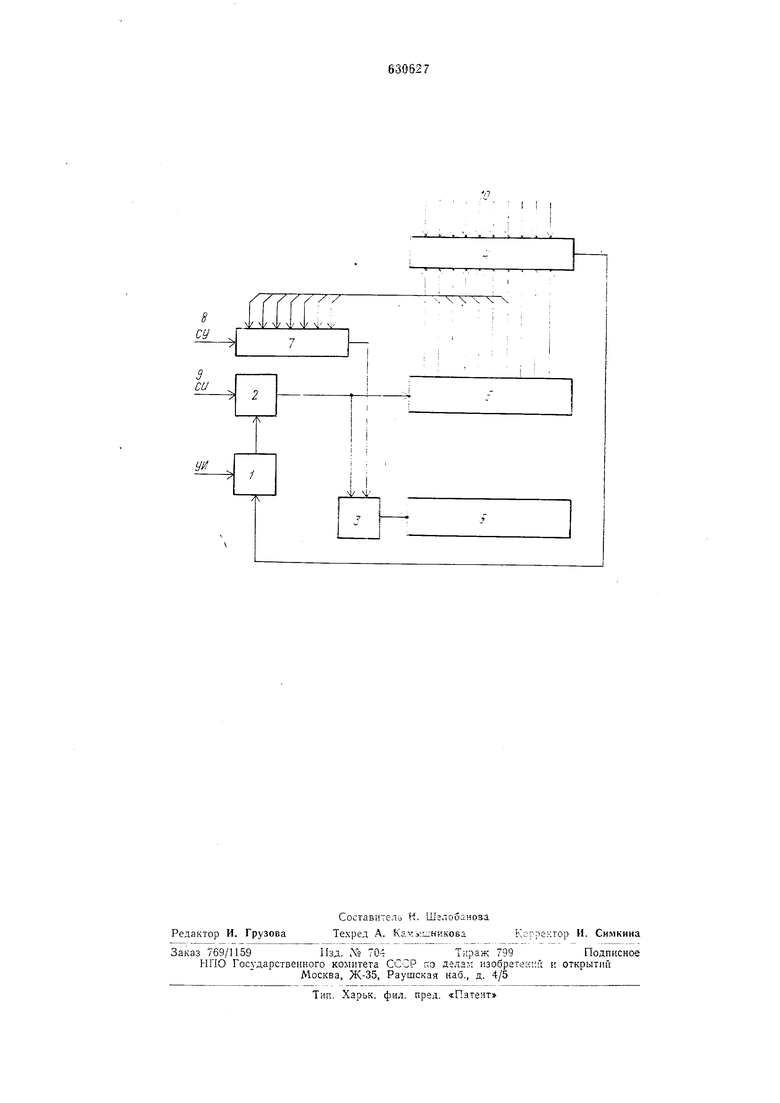

На чертеже представлена блок-схема преобразователя двоичных десятиразрядных чисел в двоично-десятичные.

Она содержит триггер /, элементы И 2, 3, схему 4 сравнения, двоичиын 5 и двоичнодесятичный 6 счетчики, анализатор 7 двоичиого кода, щииу 8 установки режима и входную шину 9, информаииокны.е входы 10 преобразователя.

В иачале цикла преобразования установочный импульс (УИ) обнуляет счетчкки и устанавливает триггер 1 в состояние, при котором элемент И 2 открыт. Через этот элемент счетные имиульсы (СИ) поступают на вход двоичного счетчика 5, пока его .код не станет равным входно у двоичному числу. В этот момент схека 4 сравненИЯ выдает сигнал, устанаЗЛ ИБающий триггер 1 в исходное состояние, после чего элемент И 2 закрывается и постуилсние импульсов на счетчики прекращается.

В режиме преобразования иелых чисел анализатор 7 двоичного кода выключен и элемент И 3 постоянно открыт. Поэтому оба счетчика к кониу цикла преобразования сосчитают одинаковое количество импульсов, и на выходах счетчика 6 установится целое число, соответствующее входному двоичиому числу.

В режиме иреобразования дробных чисел по сигиалу установки режима преобразования дробных чисел (СУ) включается анализатор 7 двоичного кода, который периодически закрывает элемент И 3, сбеопечИвая (бломвровку Одного и-Мпульса ка входе счетчика 6 при определенных кo fбинациях разрядов двоичного счетчика 5.

При преобразоваиии максимального двоичиого дробного числа 1- ,,,, меющего единицы во всех разрядах, количество за блокированпых им-пульсоз равно

24. В результате двоичный счетчик 5 сосчитает 1023 имиульса, а двоично-десятичный 999, что соответствует десятичному числу 0,999, так как заиятая фиксируется перед третьим старщим десятичным разрядом. Моменты блокировки импульсов равномерно расиределеиы по всему диапазону двоичных чисел таким образом, что из каждых 128 имиульсов, составляющих восьмую часть полного диапазона, исключаются 21, 64 и 107 имиульсы. Поэтому к анализатору 7 двоичного кода, содержащему, например три селектора (элементы И), выходы которых объединены по схеме ИЛИ, присоединены только семь младших разрядов двоичного счетчика 5. Предложенный иреобразователь позволяет ироизводить иреобразование двоичных десятнразрядных как иелых, так и дробных чисел в двоичио-десятичные.

Формула и 3 о б р е т е и и я

1.Преобразователь двоичных десятиразрядных чисел в двоично-десятичные, содержащий Tpairrep, толключенный выходом к одному из входов элемента И, другой вход которого подключен к входной щиие преобразователя, а выход - ко входу двоичного счетчика, двоично-десятичный счетчик, отличающийся тем, что, с целью расщ {рения диапазона преобразуемых чисел, в него введены схема сравнения, анализатор двоичного кода и второй элемент И, причем информациоиные входы иреобразователя подключены к первой груиие входов схемы сравнения, вторая группа входов которой соединена с разрядными выходами двоичного счетчика, семь младших разрядов которого соединены со в.ходами анализатора двоичного кода, уиравляющий вход которого соединен с шиной уста.но1вки режима, а 1выход - с одним из входов второго элемента И, связаииого другим входом и выходом соответственно с входами двоичного и двоичнодесятичного счетчиков, выход с.чемы сравнения подключен к уиравляющему входу триггера.

2.Преобразователь по п. 1, отличающийся тем, что анализатор двоичного кода 1С:ОдерЖ1ИТ три элемента И, группы входов которых являются входаМ|И анализатора двоичного кода, а выходы подключены к входам элемента ИЛИ, выход котоpoiro Я вляется -выходом анал1изатора двоичного кода.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР До 225551, кл. G 06 F 5/02, 1967.

2.Сухомлинов М. М. и Выхованец В, И. Преобразователи кодов чисел. Киев, изд. Техника, 1965, с. 68, рис. 14.

СУ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| Преобразователь двоично-десятичного кода в последовательный двоичный код | 1975 |

|

SU720424A1 |

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1977 |

|

SU739523A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1976 |

|

SU744545A1 |

| Устройство для записи кодовой информации на подвижный ноститель | 1975 |

|

SU558297A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1979 |

|

SU860054A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU888102A1 |

| Устройство для преобразования двоичного кода в двоично-десятичношестидесятиричный | 1977 |

|

SU734668A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1983 |

|

SU1124282A1 |

Авторы

Даты

1978-10-30—Публикация

1977-01-10—Подача