Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении двоично-десятичных преобразователей. Известен преобразователь двоичного кода в двоично-десятичный, содердащий двоичный, двоично-десятичный регистры, цепи коррекции, элементы И ПНедостаток этого устройства состоит в большой погрешности, невозможности преобразования в двоичнодесятично-шестидесятиричный код. Наиболее близким к предлагаемому по технической сущности и схемному решению является преобразователь дво ичного кода в двоично-десятично-шестидесятиричный код, содержащий регистр, состоящий из тетрад единиц се кунд, единиц минут, единиц градусов десятков градусов, триад десятков се кунд, десятков минут и диады сотен градусов, причем синхровходы регистр соединены с входом тактовых импульсо преобразователя, а установочные входы соединены с входом начальной установки преобразователя. Кроме того преобразователь включает дешифратор коррекции, корректор времени, реверси ный регистр сдвига и коммутатор vJ . Недостаток данного преобразователя состоит в относительно низкой точности и малом быстродействии. Цель изобретения - увеличение точности и повышение скорости преобразования. Поставленная цель достигается тем, что в преобразователь двоичного кода в двоично-десятично-шестидесятиричный код, содержащий регистр, состоящий из тетрад единиц секунд, единиц минут, единиц градусов, десятков градусов, триад десятков секунд, десятков минут и диады сотен градусов, причем синхровходы регидд.ра соединены с входом тактовых импульсов преобразователя, а установочные входы соединены с входом начальной установки преобразователя, введены двоичио-десятичный сумматор десятков градусов и сумматоры сотен градусов, сумматор единиц градусов, сумматор десятков минут, сумматор единиц минут, сумматор десятков секунд, сумматор елиниц секунд, выходы которых соединены с соответствукяцими входами тетрад, триад и диады, выходы второго, третьего и четвертого разрядов тетрад сое.аинвны соответственно с входами первого, второго и третьего, разрядов соответствуюцих сумматоров, выходы втордго и третьего разрядов триад соединены соответственно с входами первого и второго разрядов соответствующих сумматоров, выход второго разряда диады сотен градусов соединен со входом первого разряда сумматора сотен градусов, вход переноса которого соединен с выходом переноса двоичнодесятичного сумматора десятков граду сов, вход первого разряда которого соединен со входом первого разряда сумматора сотен градусов и является информационным входом преобразователя, выходы первых разрядов диады сотен градусов, тетрады десятков градусов, триады десятков секунд соединены со входами первого и третьего разрядов Двоично-десятичного сумматора десятков градусов, сумматора единиц, градусов, сумматора единиц минут и сумматора единиц секунд соответственно, выходы первых разрядов тетрады единиц градусов и тетрады единиц минут соединены со входами первого и второго разрядов сумматора десятков минут и сумматора десятков секунд соответственно.

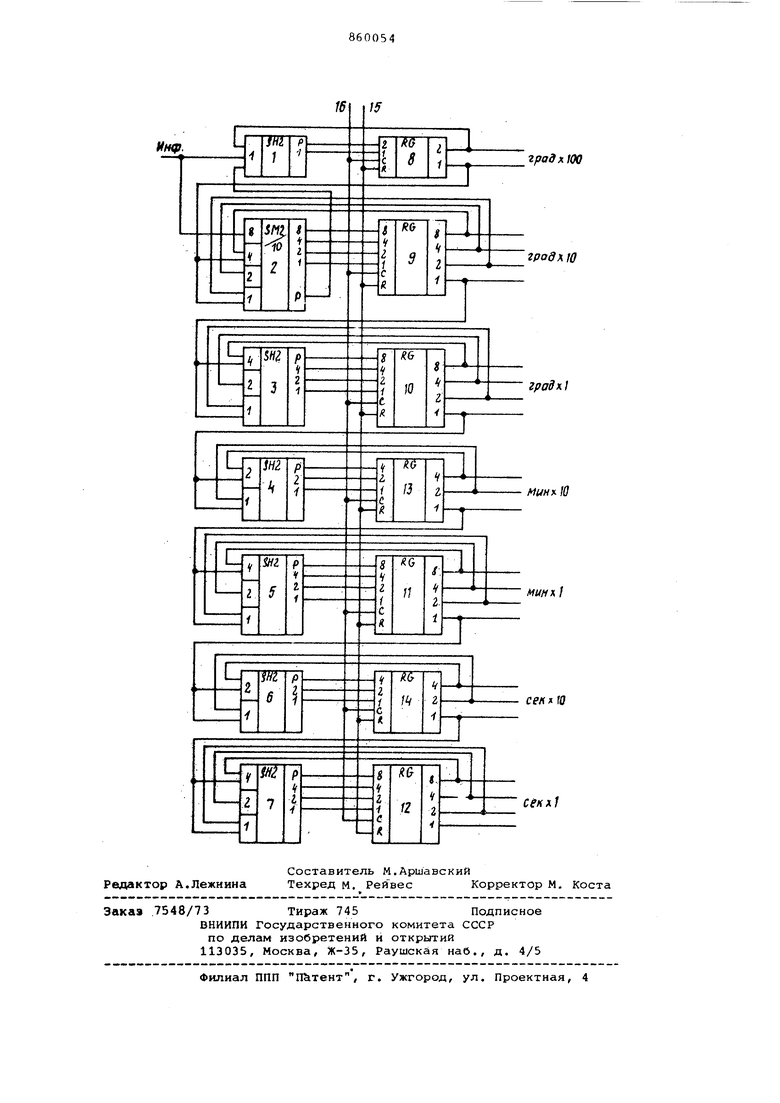

На.чертеже приведена блок-схема предлагаемого преобразователя.

Преобразователь содержит сумматор 1 сотен градусов, двоично-десятичный сумматор 2 десятков градусов, сумматор 3 единиц градусов, сумматор 4 десятков минут, сумматор 5 единиц минут, сумматор б десятков секунд, сумматор 7 единиц секунд, регистр, состояиий из диады 8 сотен градусов, тетрад 9-12 десятков градусов, единиц градусов, единиц минут, единиц секунд, триад 13-14 десятков минут и десятков секунд.

Установочные входы регистра соединены с входом 15 начальной установки преобразователя, а синхровходы - с входом 16 тактовых импульсов преобразователя. Выходы старших разрядов тетрад Стриад, Диады) 8-14 регистра подключены со сдвигом на один разряд вправо на входы двоичных сумматоров 1,3-7 и двоично-десятичного cyNiMaToра 2. Выходы младших разрядов тетрад (триад, диады 8-14 регистра угла подключены на входы сумматоров 1-7 следующих (младших) тетрад (триад) с весами 4, 1 (2, 1) соответственно. Выходы суммы и переносов двоичных сумматоров 1,3-7 и выходы суммы двоично-десятичного сумматора 2 ; подключены на информационные входы триггеров тетрад (триад, диады) 8-14 регистра угла.

Выход переноса двоично-десятичного сумматора 2 подключен ко второму входу сумматора 1, вход переноса которого, а также вход двоично-десятичного сумматора 2 с весом 8 соединены с информационным рходом преобразователя.

Преобразователь работает следующи образом.

По импульсу начальной установки регистр устанавливается в исходное положение. Преобразуемое двоичное число последовательным кодом, младшим разрядом вперед, тактируемое лгактовыми импульсами, поступает на |Вход двоичного сумматора 1 (с весом 1) и на вход двоично-десятичного сумматора 2 (с весом 8). Тактовые импульсы поступают на синхровходы тетрад ( триад, диады) 8-14 регистра.

В каждом такте производится сдвиг содержимого тетрад (триад, диады 8-14 регистра на один разряд вправо (в сторону младших разрядов) и суммирование со 180 при наличии единицы на информационном входе. При наличии нуля на информационном входе производится только сдвиг. Сдвиг осуществляется схемно, путем подключения выходов стариих разрядов тетрад (триад, диады) 8-14 регистра угла с весами 8, 4, 2 (4, 2) на входы сумматоров с весами 4, 2, 1 (2, 1) и выходов сумматоров на соответствующие входы регистра угла. о

При наличии единицы в млгщЬем разряде тетрады (триады, диады) производится коррекция. К содержимому следующей младшей тетрады (триады ) при сдвиге добавляется число 5 (3, то есть в каждом также производится деление на два содержимого регистра угла, а также - коррекция. Число тактов преобразования определяется максимальной разрядностью преобразуемых чисел.

Таким образом, процесс преобразования двоичных чисел в двоично-десятично-шестидесятиричные представляет собой последовательные операции деления на два содержимого двоично-десятичного регистра и суммирования с числами вида Ы. в каждом такте, где oL- значение i-ro разряда преобразуемого двоичного числа. В результате выполнения данных операций содержимое двоично-десятичного регистра представляет собой сумму эквиваленто разрядов двоичного кода преобразуемого числа, выраженных в двоично-десятично-шестидесятиричном коде.

По сравнению с известными устройствами, работающими по методу сдвига и коррекции и дающими большую погрешность преобразования, или устройствами, работающими по методу числоимпульсного пересчета с точностью не более единицы младшего разряда, что часто является недостаточным, особенно при использовании датчиков угла невысокой разрядности, предлагаемое устройство производит преобразование кодов с любой точностью, которая определяется разрядностью двоично-десятичного регистра, и имеет большее быстродействие, так как его работа длится один цикл, а у известных преобразователей - столько циклов, скол ко разрядов выходного кода. Кроме того, за счет введения двоичных и двоично-десятичного суьадаторов оно позволяет преобразовывать двоич«ый код, соответствующий различным максимальным значениям угла, наприме 360 или 180. При этом суммирование в каждом такте преобразования производится с числами или oti-go соответственно. Преимуществом предлагаемого преобразователя является также возможность преобразования двоичных кодов разрядности меньше максимальной, на которую устройство расчитано. Формула изобретения Преобразователь двоичного кода в двоично-десятично-шестидесятиричны код, содержащий регистр, состоящий и тетрад единиц секунд, единиц мийут, единиц градусов, десятков градусов, триад десятков секунд, десятков ину и диады сотен градусов, причем синхровходы регистра соединены с входом тактовых импульсов преобразователя, а установочные входы соединены с вхо дом .начальной установки преобразователя, отличающийся тем, что, с целью увеличения точности и повышения быстродействия, в него вве дены двоично-десятичный сумматор десятков гргшусов и сумматоры сотен градусов, сумматор единиц градусов, сумматор десятков минут, сумматор единиц минут, сумматор десятков секунд, сумматор единиц секунд, выходы которых соединены с соответствующими входами тетрад, триад и диады, выходы второго, третьего и четвертого разрядов тетрсщ соединены соответственно со входами первого, второго и третьего разрядов соответствуххдих сумматоров, выходы второго и третьего разрядов триад соединены соответственно со входами первого и второго разрядов соответствуяхцих сумматоров, выход второго разряда диады сотен градусов соединен со входом первого разряда сумматора сотен градусов, вход переноса которого соединен с выходом переноса двоично-десятичного сумматора десятков градусов, .вход первого разряда которого соединен с входом первого разряда сумматора сотен градусов и является информационным входом преобразователя, выходы первых разрядов диады сотен градусов, тетрады десятков градусов, триады десятков секунд соединены со входами первого и третьего разрядов двоичнодесятичного сумматора десятков градусов, сумматора единиц градусов, сумматора единиц минут, сумматора единиц секунд соответственно, выходы первых разрядов тетрады единиц градусов и тетрады единиц минут соединены со вхоДё1ми первого и второго разрядов сумматора десятков минут и сумматора десятков секунд соответственно. Источники информации, принятые во внимание .itpи зкспергизе 1.Авторское свидетельство СССР I 344437, кл. G06 F 5/02, 1970. 2.Авторское свидетельство СССР по заявке 2690979/18-24, кл. Q06 F 5/02, 04.12.78 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1988 |

|

SU1529457A2 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| Преобразователь кодов | 1989 |

|

SU1619402A1 |

| Преобразователь двоичного кода в двоично-десятично- шестидесятиричный код | 1982 |

|

SU1051529A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU771661A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943702A2 |

| Преобразователь двоичного кода в двоично-десятичный (двоичнодесятично-шестидесятичный) код | 1976 |

|

SU616627A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| Преобразователь двоичного кода в двоично-десятичный код градусов и минут | 1979 |

|

SU783787A1 |

Авторы

Даты

1981-08-30—Публикация

1979-10-10—Подача