Изобретение относится к цифровой вычислительной технике, может быть использовано в вычислительных машинах и специа.г изированных автоматических устройствах. Известен преобразователь двоичнодесятичного кода в двоичный, содержа щий регистр входного кода, формирователь эквивалентов, распределитель импульсов, суммирующую тетраду и выходной (Ij. Недостатком известного устройства является невозможность преобразования отрицательных чисел, относительно большой объем аппаратуры и низкое быстродействие, являющееся результатом последова1ельно1х анализа всех двоичных разрядов для каждого десятичного разряда. Наиболее близок к предлагаемому преобразователь двоично-десятичного кода в двоичный, содержащий регистр входного кода, распределитель импульсов, сумматор, регистр сумматора и формирователь поразрядных эквивалентов/ первая группа входов котр рого соединена с выходами регистра входного кода, вторая группа входов с выходом распределителя импульсов, а выходы формирователя соединены с первой группой входов сумматора, выходы которого соединены со входами регистра сумматора 2/, Недостатком этого устройства является невозможность преобразования отрицательных чисел и сравнительно большой объем аппаратуры, связанный с использованием полноразрядного сум матора. Цель изобретения - упрощение устройства и обеспечение возможности преобразования отрицательных чисел. Цель достигается тем, что в устройство введены дополнительный регистр, входы которого соединены с первой группой выходов регистра сумматора, а выходы - со второй группой входов сумматора, триггер знака, два элемента И и выходной элемент ИЛИ, входы которого соединены с выходами элементов И, первые входы которых соединены с выходами триггера знака, вторые входы элементов И соединены с выxoдa 5и мпа. первого и второго разрядов регистра сумматора соответственно, вход переноса сумматора соединен с единичны.м выходом триггера знака. Формирователь пора: рядчых эквивалентов содержит группу элементов I,

группу элементов ИЛИ и сумматор количества единиц, входы которого соедагнены с выходами элементов ИЛИ. вхды элементов ИЛИ соединены с выхода элементов И.

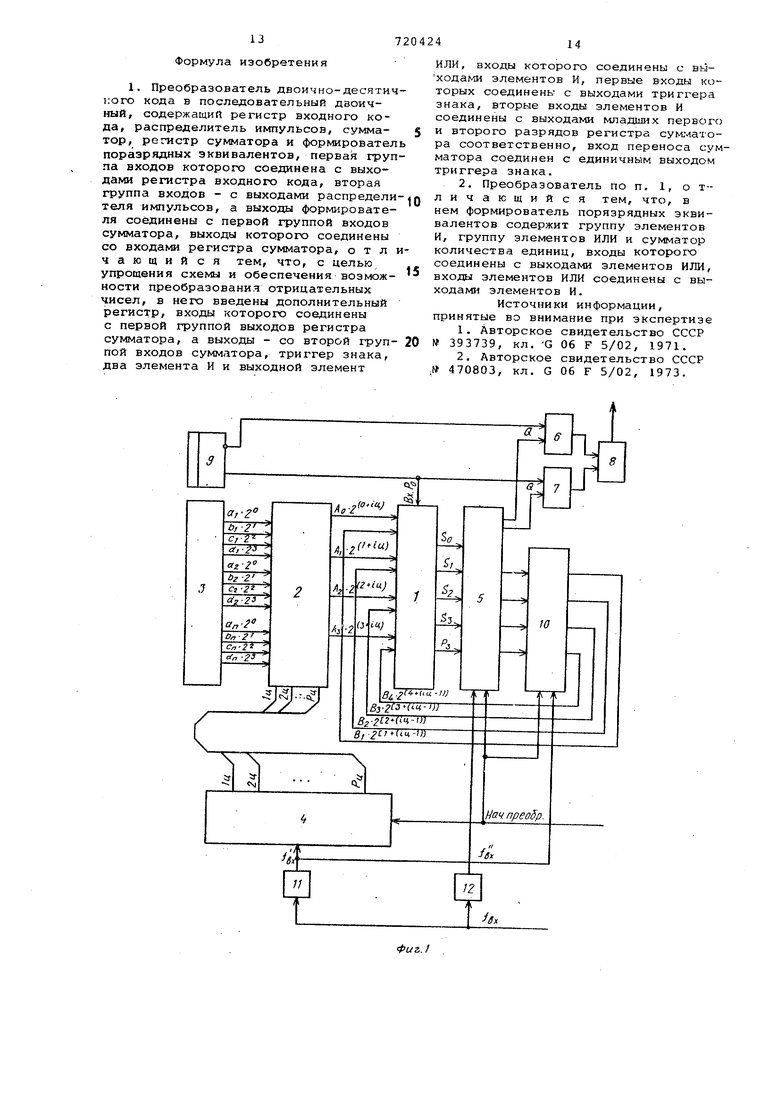

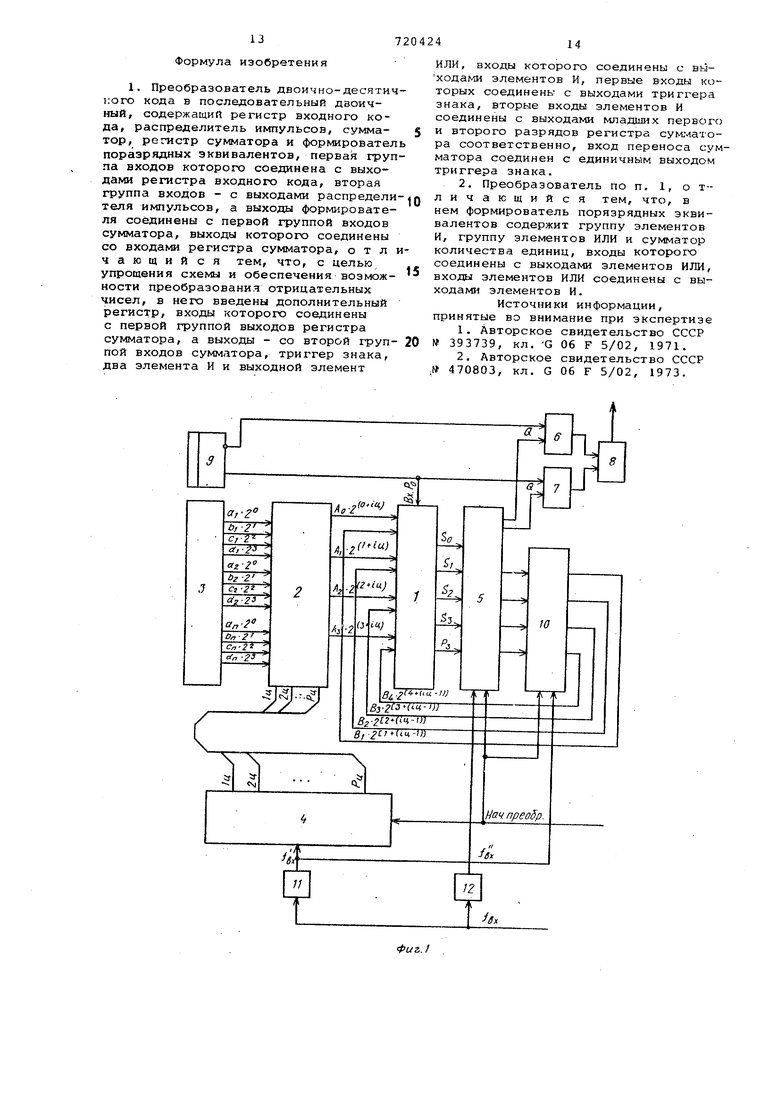

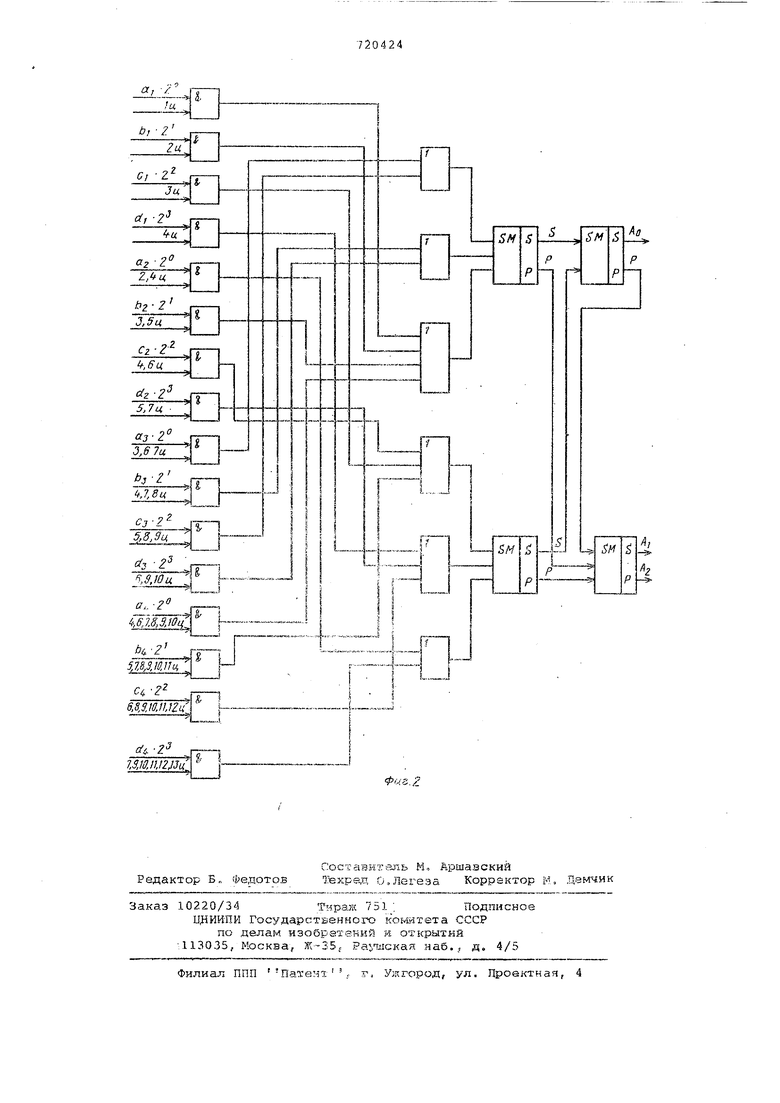

На фиг, 1 приведена структурная электрическая схема преобразователя

Преобразователь содержит cyMwiatop 1, формирователь поряэрядных эквивалентов 2, регистрвходного кода 3, распределитель импульсов 4, регистр сумматора 5, элементы И 6, 7, выходной элемент 8, триггер знака 9, регистр 10, блок выделения; переднего фронта импульса 11, блок выделения .заднего фронта импульса 1

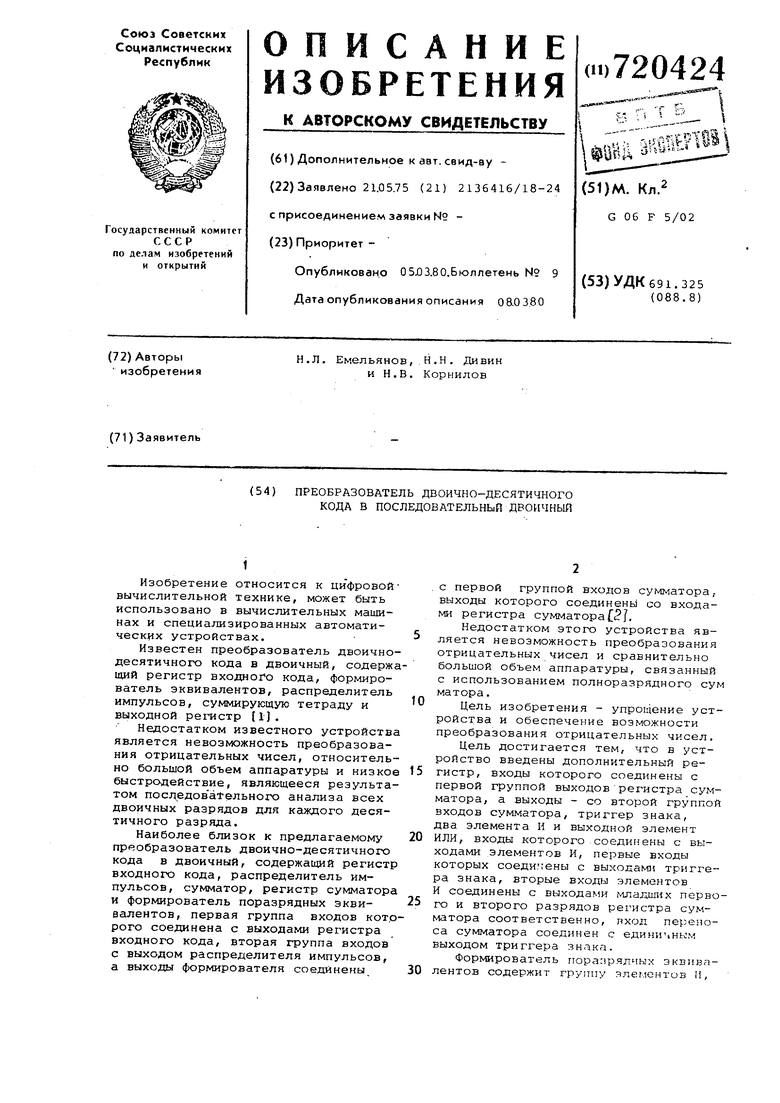

На фиг, 2 приведена структурная электрическая-схема юрмирователя поразрядных эквивалентов для четырехразрядного двоично-десятичного чи ела.

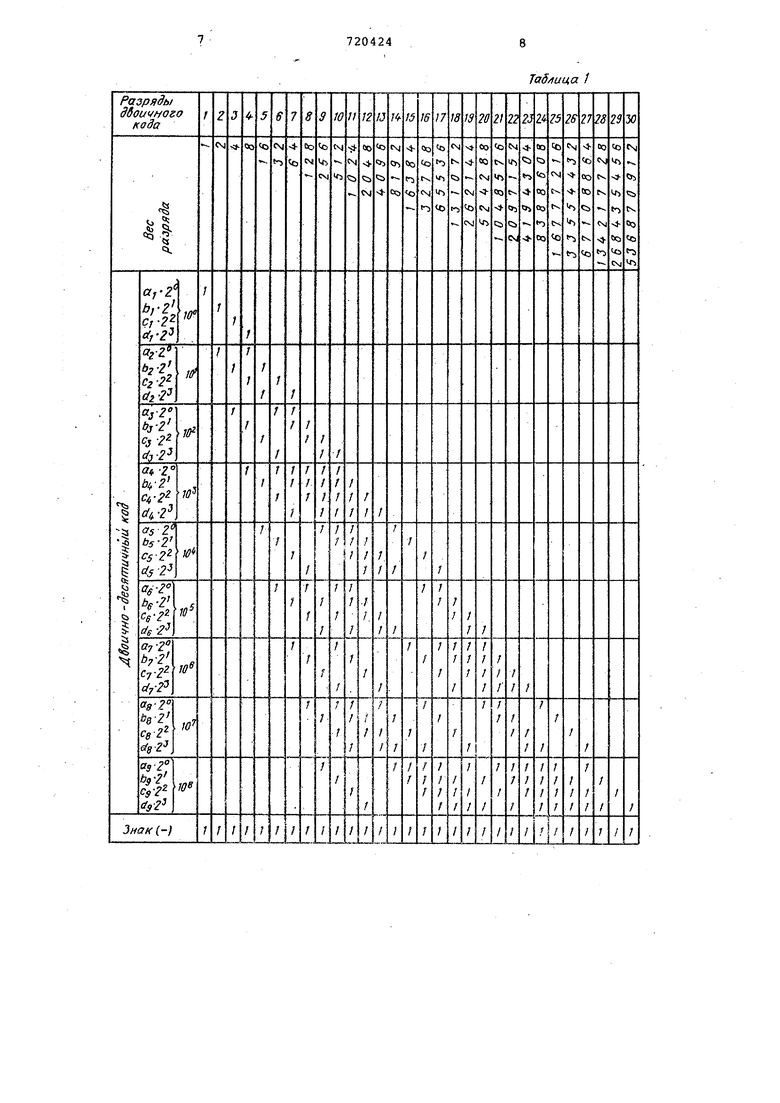

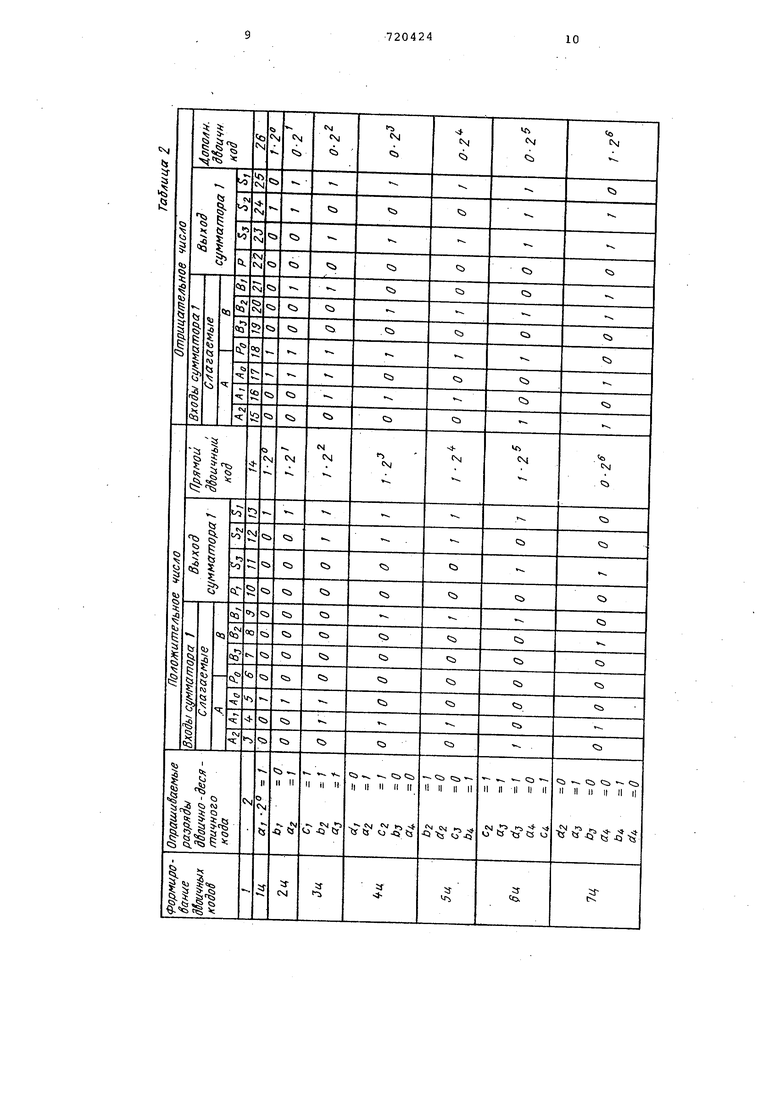

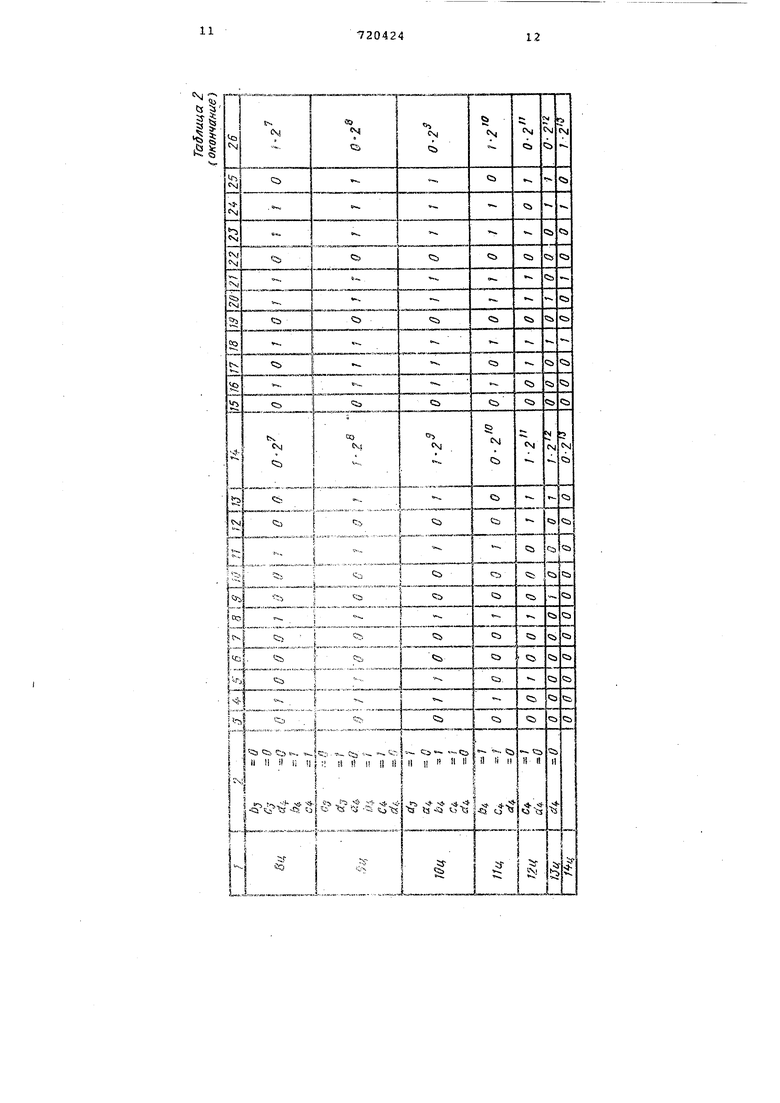

В таблице 1 приведены двоичные эквиваленты двоИч(но-десятичных чисел.

Таблица 2 иллюстрирует процесс преобразования числа ± 6975 соответственно Б прямой и дополнительный, двоичный код.

В приложении приведен алгоритм преобразования двоично-десятичногс числа в двоичный код.

Преобразователь построек следующим образом: входы К-раэрядного сумматора 1 (слагаемое А) сое,цинен,ы с выходами формирователя,поразрядны эквивалентов 2, Количество выходов формирователя, а следонательно разрядность сум штора зависит только от разрядности преоГзразуекюго двоично--десйтичыого кода. Входы форм14ро-вателя 2 соединены с одной стороны с выходами регистра входного кода 3 а с шэугой стороны - с выходакж распределителя импульсов 4, количество выходов которого равно числу разрядов преобразованного двоичногго кода. Выход каждого разряда сумматора с учетом переноса соединен с входом соответствующего разряда регистра сумматора 5. Выходы младглего разряда регистра 5 через элементы И 6, 7 соединены с выходным элементом 8. Вторые входы элементов И соед.-.инены с выходами триггера знака преобразуемого числа 9„ Единичный выход триггера знака подключен кс5 входу переноса первого разряда С5 Мматора. Остальные разряды регистра сумматора подключены ко входам 10, предназначенного для кранбгнйя второго слагаемого (), Выходы регистра 10 соединены со входами сумматора,.

Предлагаемое устройство работг1ет следующим образом. По команде Начало преобразования одиночный импульс устанавливает в нулевое соетояние распределитель И1.шульсов 4 и регистры 5, 10, Времеккой распределитель начинает пропускать на свой вход непрерывную последовательность импульсов , выделенных по заднему фронту импульсов входной частоты с помощью блока 11.

В первом столбце табл. 1 представлены веса каждого разряда двоичнодесятичного кода. В первой строке расположены номера разрядов двоичного кода, во .втором - их веса. На поле табл. 1 - вес каждого двоично-десятичного разряда, а также вес знака, расположенного в последней строке, представлены в двоичном коде.

Для преобразования двоично-десятичного кода в последовательный двоичный код достаточно сложить в двоичной системе значения разрядов двоично-десятичного кода в каждом вертикалном столбце, начиная со второго, с учетом суммы в предыдущем столбце со сдвигом ее на один разряд вправо.

Первым импульсом fg,, после прихода команды Начало преобразования на выходе 1Ц распределителя импульсов возникает сигнал, с помощью которого опрашивается состояние разряда .10° двоично-десятичного кода и значение триггера знака о

Если преобразуемое число отрицательное, значение триггера знака равно единице.

На выходе фop шpoвaтeля образуется двоичный К-разрядный код (слагаемое А), равный значению разряда

2°-lO . В это время на вторые входы сумматора поступает двоичный код pGniCTpa 10, равный нулю (слагаемое В). После сложения двух слагаемых (Аи В) с учетом знака на выходе сумматора получаете код, равный зн чению разряда -10° или aj 2°-10 + - -1°2° при отрицательном преобразуег-юм числе. Этот код записывается вторым импульсом , , выделенным по переднему фронту из входной частоты блоком 12, S регистр 5, значения младшего разряда которого .поступают соответственно на входы элементов И б и 7, управляемые триггером знака 9. Вторым к iпyльcoм fд, состоячие регистра 5 переписывается в регистр 10 без младшего разряда.

2Ц

По сигналу

распределителя импульсов начинается формирование второзх двоичного разряда, для чего опрашивается з соответствии с табл. 1 значение разрядов в 2lO, aj -2 10 и значение триггера знака. Если значения разрядов равны единице, двоичный к - разрядный код слагаемого А равен двум. Слагаемое В в этом случае зависит от знака преобразуемого числа и может принимать значения о

ил

. Третьим импульсо fII,сумма

спагаетлых А и В с учетом знака записывается в регистр 5. Дальнейшая работа преобразователя аналогична описанной. Преобразователь опрашивает разряды двоично-десятичного кода по сигналам распределителя импульсов в соответствии с табл. 1, складывает и выдает :эначения разрядов. Допустим, необходимо преобразовать положительное двоично-десятичное число

djC3b.jaj

diCtb,at N О ОНО 1001 О 111 0101

69752 i о

10 . 10 10 10 При преобразовании максимального четырехзначного двоично-десятичного числа получается 14-разрядный двоичный код , следовательно, временной распределитель должен вырабатывать четырнадцать циклов.

Максимальное число на выходе формирователя равно шести, что определяется седьмым и девятым столбцггми табл. 1, в которых при определенном двоично-десятичном коде будет шесть одновесовых единиц Следовательно, слагаенюе А будет представлено. в виде трехразрядного двоичного кода.

Формирователь поразрядных эквивалентов (фиг. 2) содержит группу 13 элементов И, ko входам которых подключены выходы регистра входного кода и определенные выходы распределителя импульсов, группу 14 элементов ИЛИ, входы которых соединены с выходами элементов И, и сумматор количества .единицы 15.. . 5 В табл. 2 подробно отображен

процесс преобразования - положительного и отрицательного чисел.

Дополнительный код р-разрядного двоичного числа равен прямому коду

Q этого числа плюс р-раэрядный двоичный код с единицами во всех разрядах с последующей инверсией.

В связи с этим на вход переноса (Р) младшего разряда сумматора постоянно подается значение триггера

знака, В столбце 36 таблицы 2 размещен дополнительный двоичный код отрицательного преобразуемого числа

Np 10 010 Oil 000001 Из опре,целения: Л00000000000000,

00110110011111.

10010011000001

Устройство может выполнять преобразование как положительных, так и

5 отрицательных чисел. Количество оборудования в нем сокрагдено в несколько раз благодаря замене полноразрядного сумматора сумматором с небольшой разрядностью при сохранении тохчэ

П же быстродействия. Преобразование

совмещается с выдачей разрядов результата.

Jad/iuu,a /

«М

at

ir Формула изобретения 1. Преобразователь двоично-десятич };ого кода в последовательный двоичный, содержащий регистр входного кода распределитель импульсов, сумматор, регистр сумматора и формировател поразрядных эквивалентов, первай груп па входов которого соединена с выходами регистра входного кода, вторая группа входов - с выходами распредели теля импульсов, а выходы формировате ля соединены с первой группой входов сумматора, выходы которого соединены со входами регистра сумматора, отл чающийся тем, что, с целью упрощения схемы и обеспечения возмож ности преобразования отрицательных чисел, в него введены дополнительный регистр, входы которого соединены с первой группой выходов регистра сумматора, а выходы - со второй груп пой входов сумматора, триггер знака, два элемента И и выходной элемент

Аа-2

аг

ь,-2

cTlZ

а,-23

аг-2°

Ьг -г с

Гг -г

cfn-

ci

.f(0iHj

.

-

(2iu)

4.

J.

w ИЛИ, входы которого соединены с выходами элементов И, первые входы которых соединены с выходами триггера знака, вторые входы элементов И соединены с выходами младших первого и второго разрядов регистра сум-матора соответственно, вход переноса сумматора соединен с единичным выходом триггера знака. 2, Преобразователь по п. 1, о т-личающийся тем, что, в нем формирователь порязрядных эквивалентов содержит группу элементов И, группу элементов ИЛИ и сумматор количества единиц, входы которого соединены с выходами элементов ИЛИ, входы элементов ИЛИ соединены с выходами элементов И. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 393739, кл. -С 06 F 5/02, 1971. 2.Авторское свидетельство СССР , 470803, кл. G 06 F 5/02, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кодов | 1978 |

|

SU744548A1 |

| Преобразователь двоично-десятичного кода в последовательный двоичный код | 1974 |

|

SU543934A1 |

| Преобразователь двоичных кодов угла и дальности в двоично-десятичные коды | 1987 |

|

SU1432782A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1984 |

|

SU1266008A1 |

| Преобразователь целых комплексных чисел в двоичный код | 1980 |

|

SU962914A1 |

| Преобразователь двоично-К-ичного кода в двоичный код | 1983 |

|

SU1126946A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

К-.г

Tl

-I

g.f4.r.«-W

.2СзЧ- -11

g..f2 ft4-r;j 5/ -f f tfi4-«

Начпрео5р. - i- l nrел5Л Ш1

7,3M ll2J3i4 i {-j

Авторы

Даты

1980-03-05—Публикация

1975-05-21—Подача