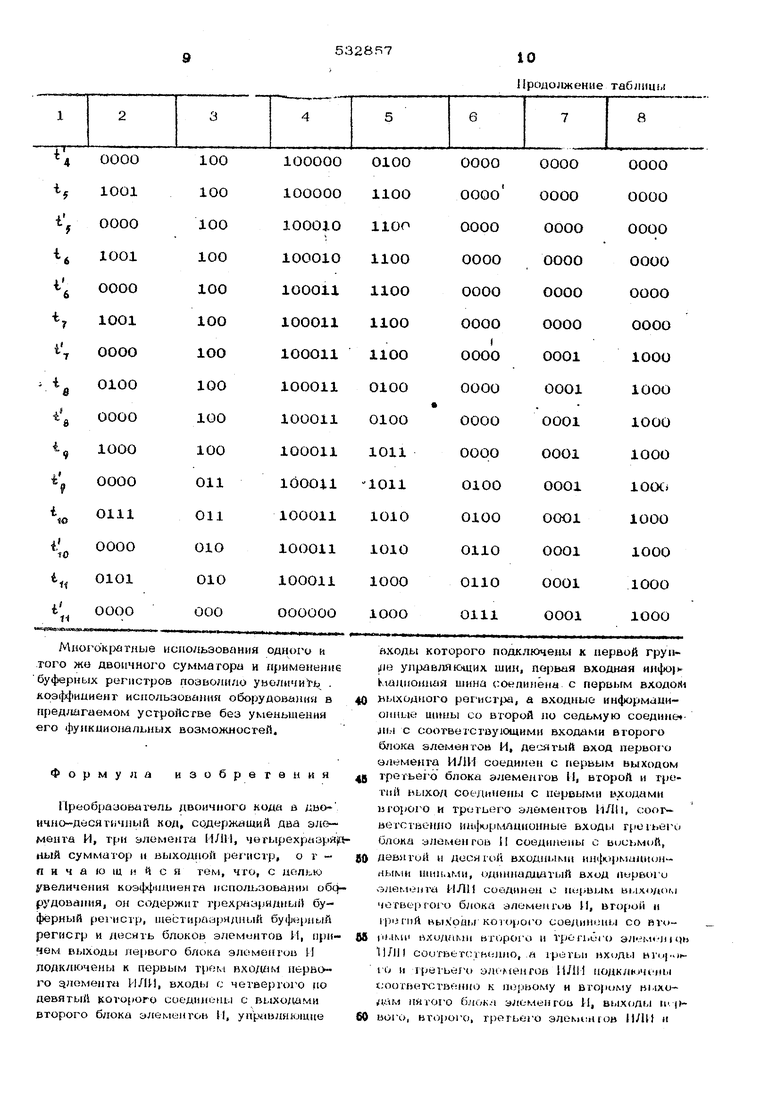

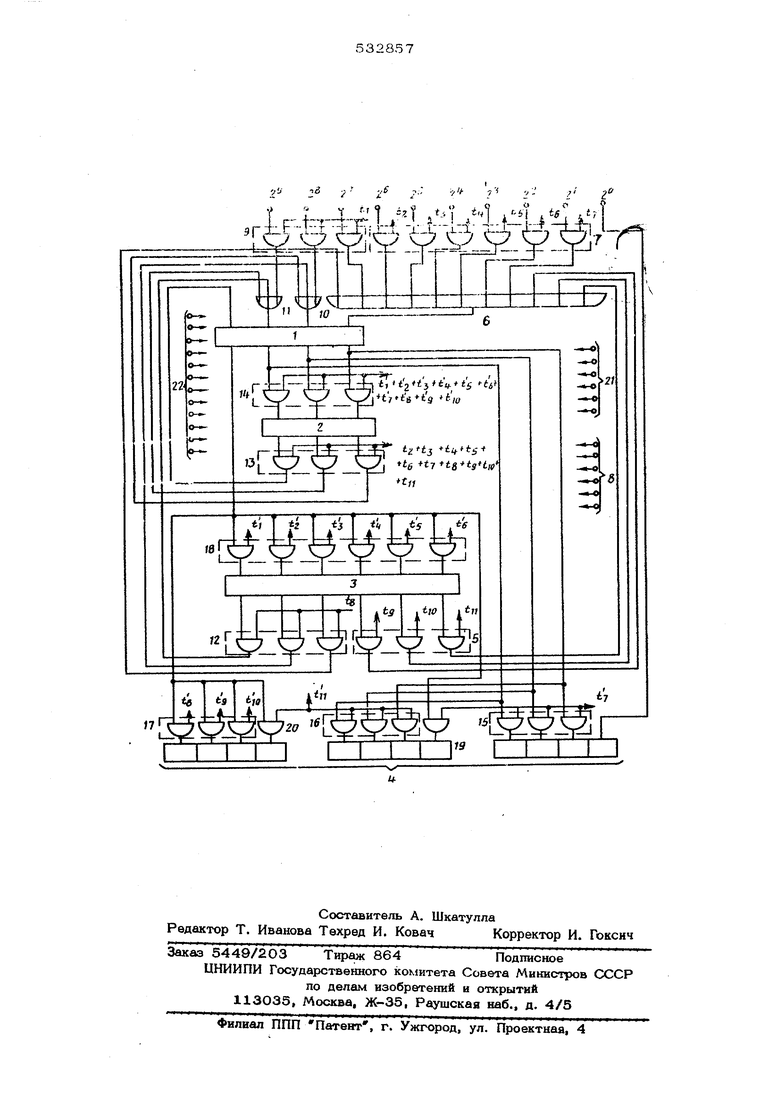

эл.менгов ii, ьыходи первого, второго, ЯЛИ ц третий выход грогьо О cj.iaMOjrj оь . ii iK. .K/u ;ji/iii.i COO ;;. ;i. ;:. э/i. -Bn4Cr-i-4 j-iO к liXii/ici; I lOpBoro, второго, тре Ti.i.;rO l JCIB jpTi.UO ;;... : p я ,дов ч е гt.ipox pa эjiepajj G iu-.ilO jMt:m)iOHHb i ,.-U o Cj .MiMi.. VOpd, .. i; jOCb.MOi-G 6jii: i.Ac;,hj lUjC foro, с СД:. .ioi;roB li ;co.iiii c:jibt между собой iJjii iiLi к nt-pt.oiO |.1ааряда чегь -;хразрйД11Ого сумматора, вторые входы lUOCToro, сед;.у.мого и восьмого блоков элил.а}1,тов i соединены между собой и под ключены к вьскод Бгорого разряда четы- рехразрядаого сумматора, а третьи входы соединены ме/вду собой и подключе:-1ы к вы ходу- третьего разряда сумматора, выход четвертого разряда которого объединен с информационными входами девятого и десятого блоков элэмелтоз 11 я первыми входами обоих элементов М, управляющие входы третьего, четвертого, лятого; шестого, седьмого и восьмого блоков элементов И подключолы ко второй группе управляющих входных тин, а управляющие входы первого девятого и десятого блоков элементов И подключены к трет)ец группе управляющих входных, шин, вторые входы первого и второго элементов И соединены соответственно с управляющими входами седьмого и восьмого блоков элементов И, выход.) шео гого блока элементов И через тре, ный буферный регистр подключены к информационным ВХОД.1М пятого блока элементов И, выходы десятого блока элементов И с первого по третий через шестиразрядный бу ферный регистр подключены к информадионным входам первого блока элементов И, а с четвертого по шестой также через щестк разрядный буферный регистр - к информационным входам четвертого блока элемен- Тов и, выходы седьмого блока элементов И подключены кй второму, третьему и четвертому входам выходного регистра, к входам с пязого по восьмой которого подключены соответственно выходы первого элемента И и восьмого блока элементов И, а к входам с девятого по двенадцатый - выХоды BTopoio элемента И и девятого блока элементов И, На- чертеже изображе1ш блок-схема пред та1таемого преобразователя. Преобразователь состоит из четырехраз рядного двоичного сумматора 1, снабженного логическим устройством для определен 1ГИЯ необходимости добавления тройки, трг,А(;азрядного буферного регистра 2, шео тнразрндного буферного регистра 3, выходного регистра 4 и десяти блоков элементов И. Выходы первого блока элементов И 5 57 о подключены к первьи.1 трем входам эл&менга ИЛИ 6, входы и четвертого по девятый которого соединены с выходами второго блока элементов И 7. Управляющие входы блока элементов И 7 подключены к первой группе управляющих пшн 8, Первая входная информационная шина, соответствук щая младшему разряд кода, соедине11а с перьым входом вгиходнсго регистра 4, а входные информационные шины со второй по седьмую - с соответствующими входами второго блока элементов И 7, Десятый вход элемента ИЛИ 6 соединен с первым выходом третьего блока элементов И 9, ьторой и третий выходь которого соедине иы с первыми входами второго 1О и треть&го 11 элементов ИЛИ. Соответственно информационные входы третьего блока элемен,тов И 9 соединены с восьмой, девятой и десятой входными информационными шинамк. Одиннадцатый вход первого элемента ИЛИ 6 соединен с первым выходом четвертого блока элементов И 12, второй и третий вь ходы которого соединены со вторыми входами элементов ИЛ11 10 и 11 соответственно, а третьи входы последних подключены cooi ветственно к первому и второму выходам пятого блока элементов И 13. Выходы пер вого, второго, третьего элементов ИЛИ и третий выход блока элементов И 13 подкл1. чены соответственно к входам первого, второго, третьего и четвертого разрядов четырехразрядного сумматора 1, Первые информационные входы шестого 14, седьмого 15 и восьмого 16 блоков элементов И соединены между собой и подключены к выходу первого разряда сумматора 1, вторые входы блоков соединены между собой и подключены к выходу второго разряда четырехразрядного сумматора 1 а третьи входы coeдинe)iы между собой и подключены к выходу третьего разряда сум матора, выход четвертого разряда которого объединен с информационными входами девятого 17 и десятого 18 блоков элементов И и первыми входами элементов И 19 и2О, Управляющие входы блоков элементов И 9, 12, 13, 14, 15 и 16 подключены ко второй группе управляющих входных шил 21, а управляющие входы блоков элементов И 5, 17 и 18 подключены к третьей группе унравл;л :щих входных шин 22, вто рые ВХОД., элементов И 19 и 20 соединелы соответственно с управляющими входами блоков элементов И 15 и 16, Выходы блока элементов И 14 через буферный регистр 2 подключены к информационным входам блока элементов И 13, выходы блока элементов И 18 с первого пс третий через буферный регистр 3 подключены к информационным входам первого блока эле- монгов И 5, а с чегвергого по шестой, также через буферный регистр 3, - к информационным входам блока элементов И 12, Выходы блока элементов И 15 подключены ко второму, третьему н четвертому входам выходного регистра 4, к входам с пятого по восьмой которого подключены соответсг венно выходы элемента И 19 и блока эле- ментов И 16, а к входам с девятого по двенадцать - выходы элемента И 20 и блока элементов И 17, Преобразователь работает следующим образом, На вход преобразователя подается десятиразрядный двоичный код, подлежащий преобразованию. Первоначально ячейки буферных регистров 2 Vi 3 очищены и сигнал на их выходах имеют значения, равные Hj-

Лю,

Младший разряд преобразуемого кода (2 ) сразу заносится в младшую ячейку младшей тетрады выходного регистра 4,

Устройство управления вырабатывает

снгналы. t...t и ,.--.-t6,ti,-t, которые разрешают прохождение информации через соответствующие элементы И, Сигналы t следует с некоторым интервалом At (такт), а сигналы i сдвинуты по отношению к сигналам -t на дЧ/2.

В момент ij через блок элементов И 9 на первые три входа сумматора 1 поступают три самых старших разряда преобразуемого кода (2,2 и 2), На четвертый вход сумматора подается сигнал О с тр&тьего выхода блока элементов И 13.

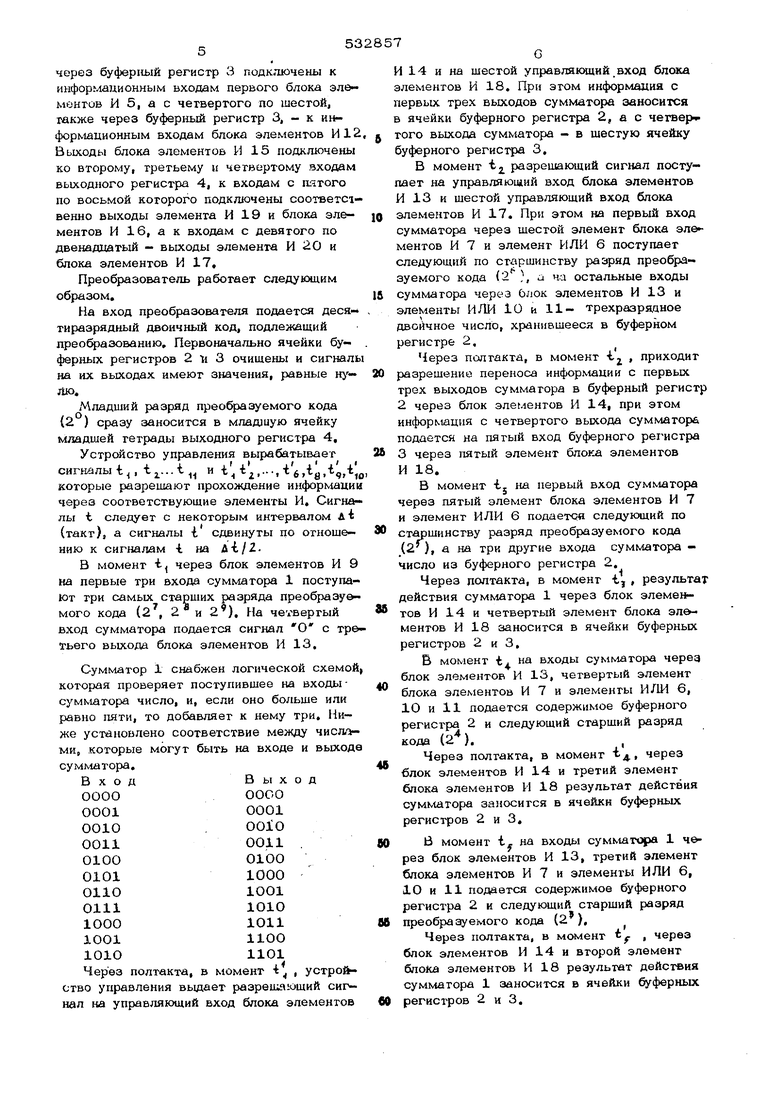

Сумматор 1 снабжен логической схемой которая проверяет поступившее на входы сумматора число, и, если оно больше или равно пяти, то добавляет к нему три. Ниже установлено соответствие между числ,ми, которые могут быть на входе и выходе сумматора.

ВходВыход

0000ОООО

00010001 О01О . OOlO ООНООН .

010001ОО

01011000 оно1001 01111010

10001011

1001110О 101О1101

Через полтакта, в момент , устройство управления выдает разреииающкй сигнал на управляющий вход блока элементов

трех выходов сумматора в буферный регистр 2 через блок элементов И 14, при этом информация с четвертого выхода сумматора подается на пятый вход буферного рехистра 3 через пятый элемент блока элементов И 18,

В момент ij на первый вход сумматора через пятый элемент блока элементов И 7 и элемент ИЛИ 6 подаетсда следующий по старшинству разряд преобразуемого кода (2), а на три другие входа сумматора число из буферного регистра 2,

Через полтакта, в момент tj , результат действия сумматора 1 через блок элеменн тов И 14 и четвертый элемент блока элементов И 18 заносится в ячейки буферных регистров 2 и 3,

В момент tj на входы сумматора через блок элементов И 13, четвертый элемент блока элементов И 7 и элементы И/М 6, 10 и 11 подается содержимое буферного регистра 2 и следующий старший разряд кода (2 ).

Через полтакта, в момент Ьд, через блок элементов И 14 и третий элемент блока элементов И 18 результат действия сумматора заносится в ячейки буферных регистров 2 и 3,

В момент t- на входы суммаг а 1 ч&рез блок элементов И 13, третий элемент блока элементов И 7 и элементы ИЛИ 6, Ю и 11 подается содержимое буферного регистра 2 и следующий старший разряд преобразуемого кода (2),

Через полтакта, в момент , через блок элементов И 14 и второй элемент блока элементов И 18 результат дейсхчвия сумматора 1 заносится в ячейки буферных регистров 2 и 3, И 14 и на шестой управляющий вход блока элементов И 18, При этом информация с первых трех выходов сумматора заносится в ячейки буферного регистра 2, а с четвер того выхода сумматора - в шестую ячейку буферного регистра 3, В момент tj разрешающий сигнал поступает на управляющий вход блока элементов И 13 и шестой управляющий вход блока элементов И 17, При этом на первый вход сумматора через шестой элемент блока эле ментов И 7 и элемент ИЛИ 6 поступает следующий по старшинству разряд преобразуемого кода (2 }, а ча остальные входы сумматора через блок элементов И 13 и элементы ИЛИ Ю и 11- трехразрядное двоичное число, хранившеесн в буферном регистре 2, Через полтакта, в момент -tj , приходит разрешение переноса информации с первых

В MOMi.ur t (j lixo/ibi сумматора 1 чеjpoa блок злсч-.и.Нмш И .13, второй эломеиг П.чокй элРМСИгов П 7 1 элементы ИЛИ 6, Ю 11 11 милаетси сод1;{)жимое буферного pt-rncrpa 2 (1 следующий старший разряд лреобразуимого кода (2. ),

Ч( полгакга, в момент i, , через 6,юкодементоБ И 14 и первый элемент блока элементов И 18 резульгаг действия сумматора 1 заносится в ячейки буферных регистров 2 и 3,

В момент i на входы сумматора 1 че рез блок элементов И 13, первый элемент блока злемелтов И 7 н элемент ИЛИ 6, J.O и 11 подается содержимое буферного jperHCTpa 2 и следующий старший разряд преобразуемого кода (2 ).

Чороз полгакта, в момент i , через б/юк элеменгов И 15 и элемент И 19 ре«. Ьульт41т дййствия сумматора заносится Б ячейки ьы.ч.ОАин)го регистра 4,

В момс-аг ig через блок элементов .И

12н элементы ИЛИ 6, 1О н 11 tm парны (три входа сумматора поддо7ся содержимое Ьрех йнеек буферногю регистра 3 На чет-« оертый вход суммаTOjja с выхода третьего елемеата блока элеменгов И 13 в з1ч вре Мя nocyymier О.

В момент tg резулс-тат действия сум- мЯтора 1 stuiocHTCH через блок элементов И 14 и третий элемент блока эламентоЬ И 17 соотБйгственио в буферный регистр 2 и в ячейку старщего разряда старшей тетрады выходного регистра 4

В момент t через блок элемеигов И

13и элементы ИЛИ 10 и 11 на гри старшнх входа сумматора 1 .подавгея содержимое буферного peiHcipa 2, а на первый

ВХ.ОД сумматоре 4tj|.U3 третий элемент блока элементов И 5 и элемс нт ИЛИ 6 - со аоржимое ячей|си буферно1о регистра 3,

В момент i результат действия суммагора 1 через блок элементов И 14 и

второй элемент блока элементов И 17 аансЦ рнтся в буферный регистр 2 и в ячейку старшей тетрады BLIXO HOI O регистра f.

В момент через блок элементов И 13 R элементы ИЛИ 10 и 11 на три старшие входа сумматора 1 подается содержиpvioe буферного регистра 2, а на первый вход через второй элемент блока элеменгов И . 5 и элемент ИЛИ 6 - содержимое ячейки буферного регистра 3„

В момент результ г действия сумматора через блок элементов р1 14 и первый элемент блока лементов И 17 заносится в буферный регистр 2 и в ячейку старшей тетрады выходного регистра 4.

В моменг -1.. через блок элементов И 13 и элементы ИЛИ 1О и 11 на три стар S1IHX входа сумматора подается содержимое буферного регистра 2, а через первый элемент бло.а элементов И 5 и элемент ИЛИ 6 - на первый вход суммато ш - содержимое ячейки бу(| ериого регнсгра 3,

В момент i , резульгг действия сумматора через блок элементов И 16 и эле мент И 20 заносится в ячейки средней и старше тетрады выходного регистг 4, На этом преобразование заканчивается. Преобразованное число Mo/iiOT быть получено на лыходах ячеик выхо/шого регис1ра 4.

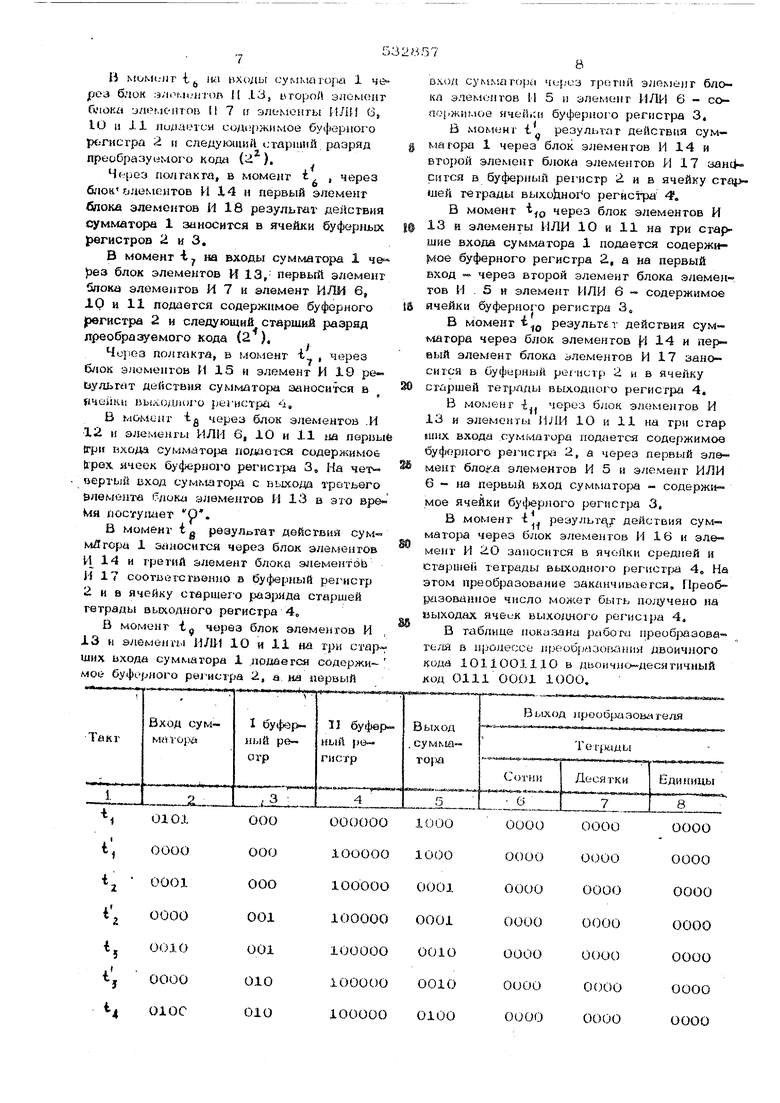

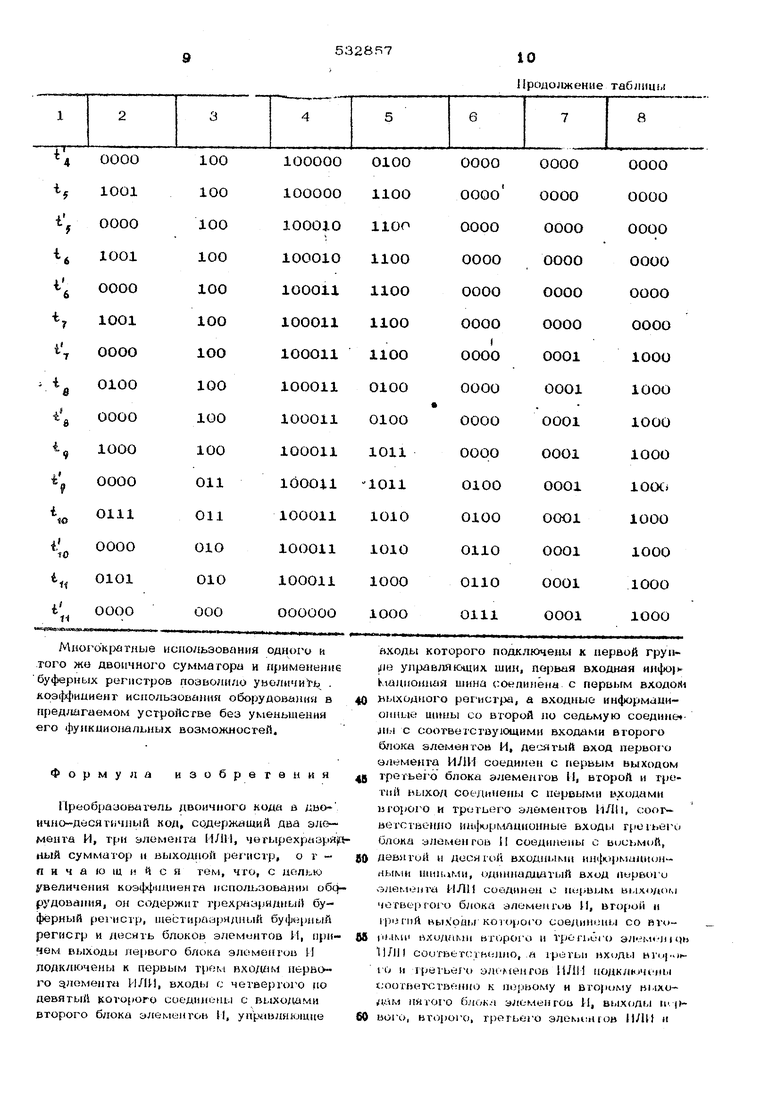

В таблнде показана работа) преоб} азова« те/ш в lijjouecce iipeoDpM3OFi UHu двоичного кода 1О11ОО1110 в двоично-десятичный код О111 OOD1 1ООО.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Устройство для преобразования интервалов времени в цифровой код | 1985 |

|

SU1411701A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1448412A1 |

| Устройство для преобразования двоичного кода в двоично-десятичный | 1976 |

|

SU669352A1 |

| Устройство для деления | 1984 |

|

SU1259251A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ И ВЫЧИТАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2389064C1 |

| Многоканальный преобразователь аналог-код | 1981 |

|

SU978339A1 |

| Логический процессор | 1985 |

|

SU1305704A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ОБРАЗОВ | 2010 |

|

RU2430415C1 |

ООО ООО 001 О01 010 О10

Многок|затные использования одного я того же двоичного сумма гори и применение буферных регистров позволило уиелнчи ь . коэ(})(1тциент исполызоваиия оборудования в предлагаемом усгройсгве без уменьшения его функциональных возможностей.

Формула изобретен ия

Преобрааовагель двоичного кода 0 дьоично-десягичаый код, содержащий два элемента И, три элемента 11/111, чвгь рехрг13ря(аг ный сумматор и выходной регистр, о г п н ч а ю щ и и с я том, что, с целью увеличения коэ(|х{л1Диентй пспо/шзования обфрудования, он содержит трех заарндньнУ буферный регис р, 1иест 1раа|)ядный буфврнь|й регистр и десять блоков элементов И, причем выходы первого блока элсмошов И лодключены к первым трем входам первого элемента ИЛИ, входы с четвертого ио девятый которого соединены с выходами второго блока элементов И, упргпзляюшие

Иродолженне таблицы

йходы которого подключены к первой грун(Ие управляющих шин, первая входная Ьланконная шина соединена с первым входоК1 выходного рогис1-ра, а входные информационные шины со второй ио седьмую соединен4Н;| с соотвегствующими BXOAtJMH второго блока элементов И, десятый вход первого алемента ИЛИ соединен с первым выходом третьехО блока элементов И, второй и третий выход соединены с первыми входами wrojjoro и третьего алиментов ИЛИ, соогветствекио ин1}юрмационные входы третьего блока улеменгов И соединены с висьмс й, девятой и десятой входнь1ми нымя иниими, одиннадцатый вход первого олемепга ИЛИ соединен с iieiiBUM Bi,ix4)AO(vj четве1)го1-о блока алемелгив И, второй и ipeciiA ныхо0|,1 которого соединены со втоiit.iMH rtXo/uiNHi второго и третьего элем 1 )ь или couTBeTciHtiJHio, а 1р1эгьи входь. HTI)IIlo и ipevberi улсменгов ИЛИ подключены 1;оответ Пввнно к но|;1ьому и второму BLIXOдам ня гого блока элемеигои И, вьлходы ги (Н ВО1Ч, BTOpoio, Tperbeio элек11 нгов ИЛИ и

грегий выход пятого блока элементов И подключены соотвегственно к входам первого, второго, третьего и четвергого раз рядов четырехразрядного сумматора, первые информационные входы шестого, седьмого и восьмого блоков элeмeiiтoв И соединены между собой и подключены к вьосоду перво«« го разряда четырехразрядного сумматора, вгирые входы шестого, седьмого и восьмо- го блоков элементов И соединены между со бой и подключены к выходу второго разряда четырехразрядного сумматора, а третьи вхо« ды соединены между собой и подключены к выходу третьего разряда сумматора, выход четвертого разряда которого объединен с информационными входами девятого и десятого блоков элементов И и первыми входа ми обоих элементов И, управляюшие входы третьего, четвертого, пятого, шестого, седьмого и восьмого блоков элементов И подключены ко второй группе управляющих входных шин , а упрг)вляющие входы первого, девятого и десятого блоков элементов И подключены к третьей группе управляюшнх входных шин, вторые входы первого и второго элементов И соединены соответственно с управляющими входами седьмого и

восьмого блоков элементов И, выходы шеотого блока элементов И через трехразря; ный буферный регистр подключены к информационным входам пятого блока элементов И, выходы десятого блока элементов И с первого по третий через шесгиразрядный буферный регистр подключены к информаци онньш входам nepteoro блока элементов и, а с четвертого по шестой через шестираэрядный буферный регистр к информахщо ным входам четвертого блока элементов И выходы седьмого блока элементов И под ключены ко второму, третьему и четвертому входам выходного регистра, к входам

с пятого по восьмой которого подключены соответственно выходы первого элемента

И и восьмого блока элементов И, к входам с девятого по двенадцатый - выходы второго элемента И и девятого блока элементов И,

Источники информации, принятые во внй мание при экспертизе:

1 / 2 7 -у. .7 2

Г /.1 -|Хг зг±1Е -;1::г - ;J:l:, .,

-U

л

W

Lb

t, i tVtests i,

+ 6 +t7 ig ji№ t//

j iUajteu; - 4 i

y Isa ly-

/2

n

i

t;e

ta

.n / гМрьЬ

4t,

:±M

LSSi

I I I I I I I I { r

«B

,

Авторы

Даты

1976-10-25—Публикация

1972-11-23—Подача