I

Изобретение относится к дискретной цифровой технике, в частности к триггерным уетройствам.

Известны тактируемые D-V-трнггеры, содержащие К 5-трнггер, входные элементы И-НЕ II.

Эти устройства сложны и имеют низкое быстродействие,

Известен D-V-трнггер, реализуемый на основе тактируемого D-триггера путем подключения управляющей шнны параллельно тактовой шине, содержащий входной элемент И-НЕ, элемент И-ИЛИ-НЕ н ннвертор, причем первый вход элемента И-НЕ подключен к тактовой шн не, второй - к управляющей шине, выход -- к первому входу первого элемента И элемента И-ИЛИ-НЕ, второй вход которого подключен к выходу нивертора, вход которого подключен к выходу элемента И-ИЛ И-НЕ, первый вход второгоЭлемента И элемента И-ИЛИ-НЕ подключен к тактовой шине, второй - к управляющей шине, третий - к информационной шине. |2.

Недостаток известного О-У-трнггера - низкое быстродействие.

Цель изобретения - повышение быстродействия схемы.

Для достижения поставленной цели в D-V-трнггере, содержащем элемент И-НЕ первьй вход которого подключен к тактовой шине, второй - к управляющей шнне, а выход - к первому входу первого элемента И элемента И- И,1И-НЕ, второй

вход которого подключен к выходу инвертора, вход которого подключен к выходу элемента И-ИЛИ-НЕ, первый вход второго элемента И элемента И-ИЛИ-НЕ подключен к тактовой шнне, а второй - к управляющей шине, третий вход элемента И-НЕ подключен к информационной шине, а его выход подключен к третьему входу второго элемента И элемента И-ИЛИ--НЕ.

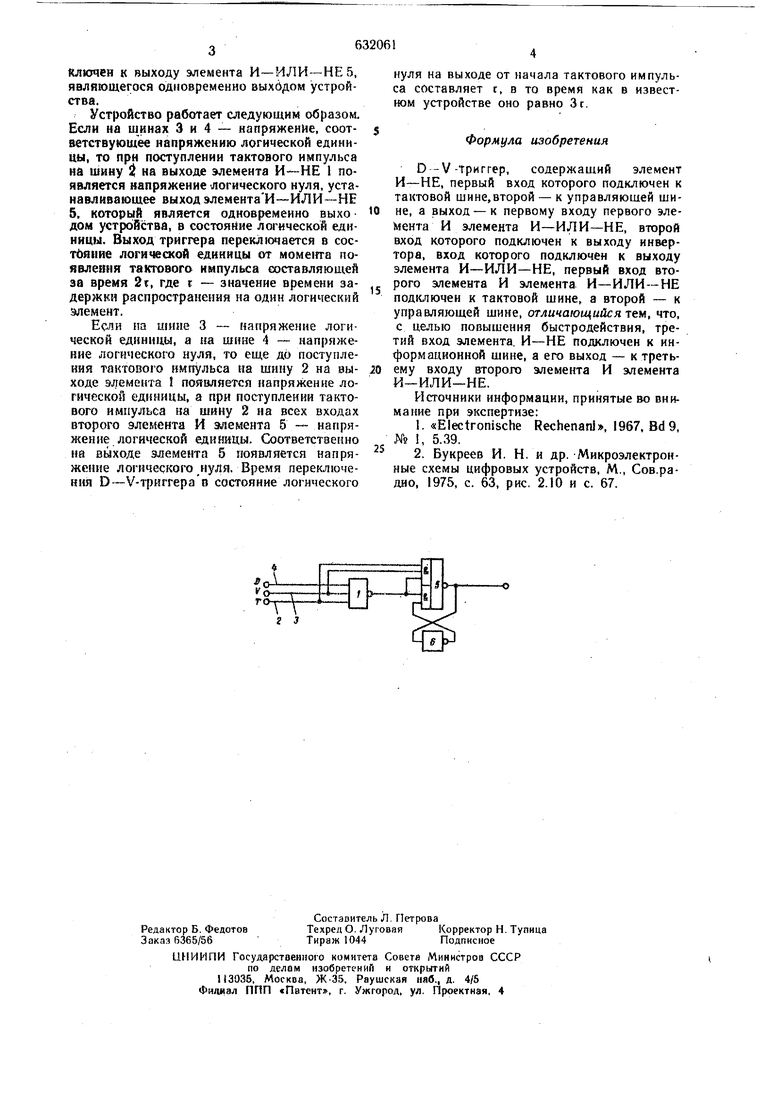

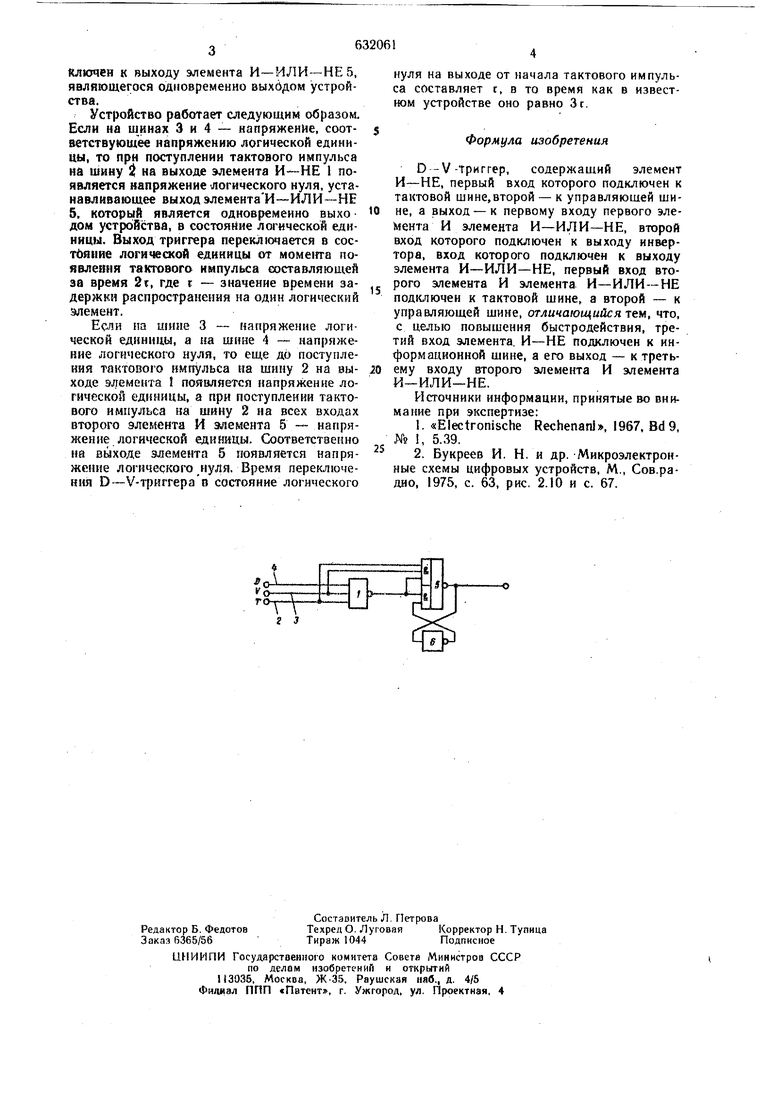

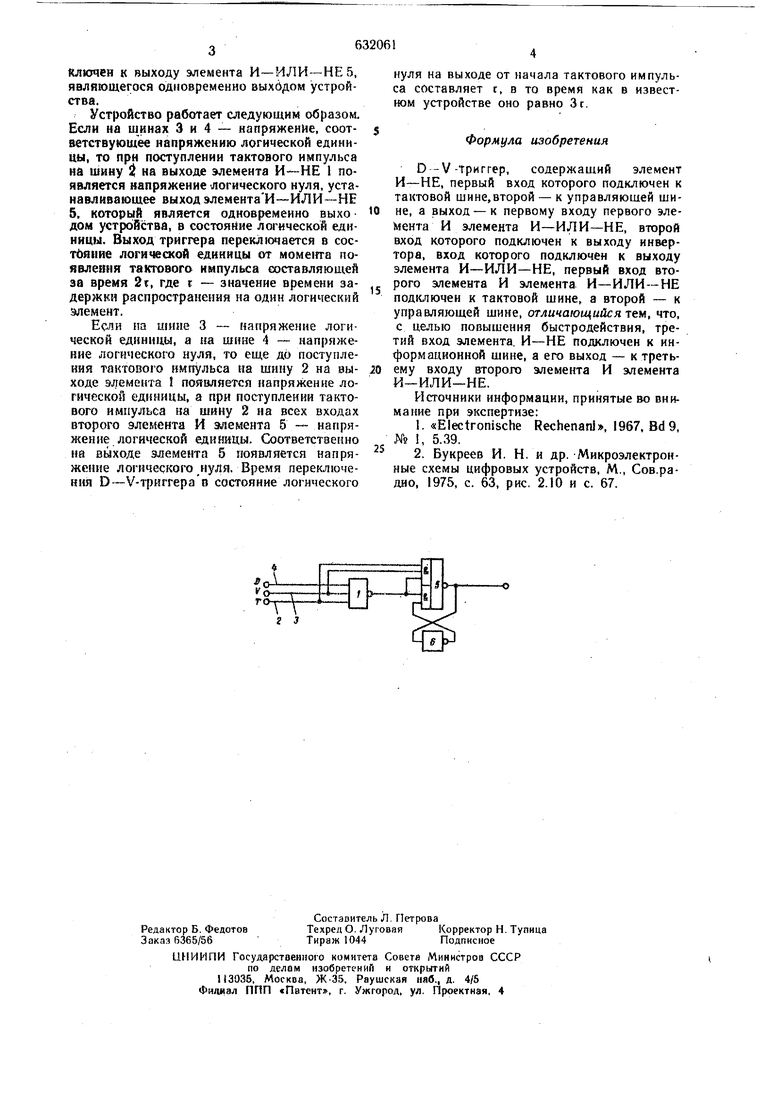

На чертеже изображена электрнческая схема D--V-триггера,

Первый вход элемента И- НЕ I подключен к тактовой шине 2 (Т), второй - к управляющей шине 3 (V), третий - к ннформацнонной шине 4 (D), а выход - к первому входу первого элемента И элемента И-ИЛИ-НЕ 5, второй вход которого подключен к выходу ннвертора 6 и к третьему . бходу второго элемента И элемента И-ИЛИ-НЕ 5, первый вход которого подключен к тактовой шнне 2, а второй - к управляющей шине 3; вход инвертора 6 подключей к выходу элемента И-ИЛИ-НЕ 5, являющегося одновременно выхбдом устройства.

Устройство работает следующим образом. Если на шинах 3 и 4 - напряжение, соответствующее напряжению логической единицы, то при поступлении тактового импульса на шину SJ на выходе элемента И-НЕ 1 появляется напряжение логического нуля, устанавливающее выход элементаИ-ИЛИ-НЕ 5, который является одновременно выхо дом устройства, в состояние логической единицы. Выход триггера переключается в состбяние логической единицы от момента появлешш тактового импульса составляющей за время 2t, где t - значение времени задержки распространения на один логический элемент.

ЕСЛИ па шине 3 - напряжение логической единицы, а на шине 4 - напряжение логического нуля, то еще до поступления тактового импульса на шнну 2 на выходе элемента появляется напряжение логической единицы, а при поступлении тактового нмпульса Ш шину 2 на всех входах второго элемента И элемента б -- напряжение логической единицы. Соответственно на выходе элемента 5 появляется напряжение логического нуля. Время переключения D-У-т1)иггера о состояние логического

нуля на выходе от начала тактового импульса составляет с, в то время как в известном устройстве оно равно 3г.

Формула изобретения

D-V-триггер, содержащий элемент И--НЕ, первый вход которого подключен к тактовой шине,второй - к управляющей щине, а выход - к первому входу первого элемента И элемента И-ИЛИ-НЕ, второй вход которого подключен к выходу инвертора, вход которого подключен к выходу элемента И-ИЛИ--НЕ, первый вход второго элемента И элемента И-ИЛИ-НЕ подключен к тактовой щине, а второй - к управляющей щине, отличающийся тем, что, с целью повышения быстродействия, третий вход элемента. И-НЕ подключен к информационной щнне, а его выход - к третьему входу второго элемента И элемента И-ИЛИ--НЕ.

Источники ннформацин, принятые во внимание при экспертизе:

1.«Electronische RechenanJ, 1967, Bd 9, Mf , 5.39.

2,Букреев И. Н, и др. Микроэлектронные схемы цифровых устройств, М., Сов.радао, 1975, с. 63, рис. 2.10 и с. 67.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления т-фазным тиристорным инвертором | 1978 |

|

SU758470A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Формирователь одиночного импульса (его варианты) | 1983 |

|

SU1190488A1 |

| D-триггер | 1985 |

|

SU1332380A1 |

| Счетчик типа "регистр-сумматор" | 1974 |

|

SU546111A1 |

| Устройство для передачи информации с вращающегося объекта | 1986 |

|

SU1334173A1 |

| Делитель частоты с переменным коэффициентом деления | 1982 |

|

SU1081804A1 |

| Устройство для выделения импульса | 1980 |

|

SU1019606A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| РЕЗОНАНСНЫЙ ИНВЕРТОР НАПРЯЖЕНИЯ | 1993 |

|

RU2072619C1 |

г J

Авторы

Даты

1978-11-05—Публикация

1977-05-13—Подача