pa, ./ -вход которого подключен к шине сложення, а 5-вход к шнне зычлтангя, причем блок формирования кода содержит 5-триггер, 5-вход которого подключен к liHBepCHOMV входу элемента «запрет и первому входу блока формирования кода, а -в.ход - к выходу элемента «запрет, а выход 5-триггера подключен к входу сумматора но модулю два, второй вход которого соединен ео вторым входом блока формирования кода, а выход - с выходом блока формирования кода, прямой вход элемента «запрет, соединен с третьим входом блока формирования кода.

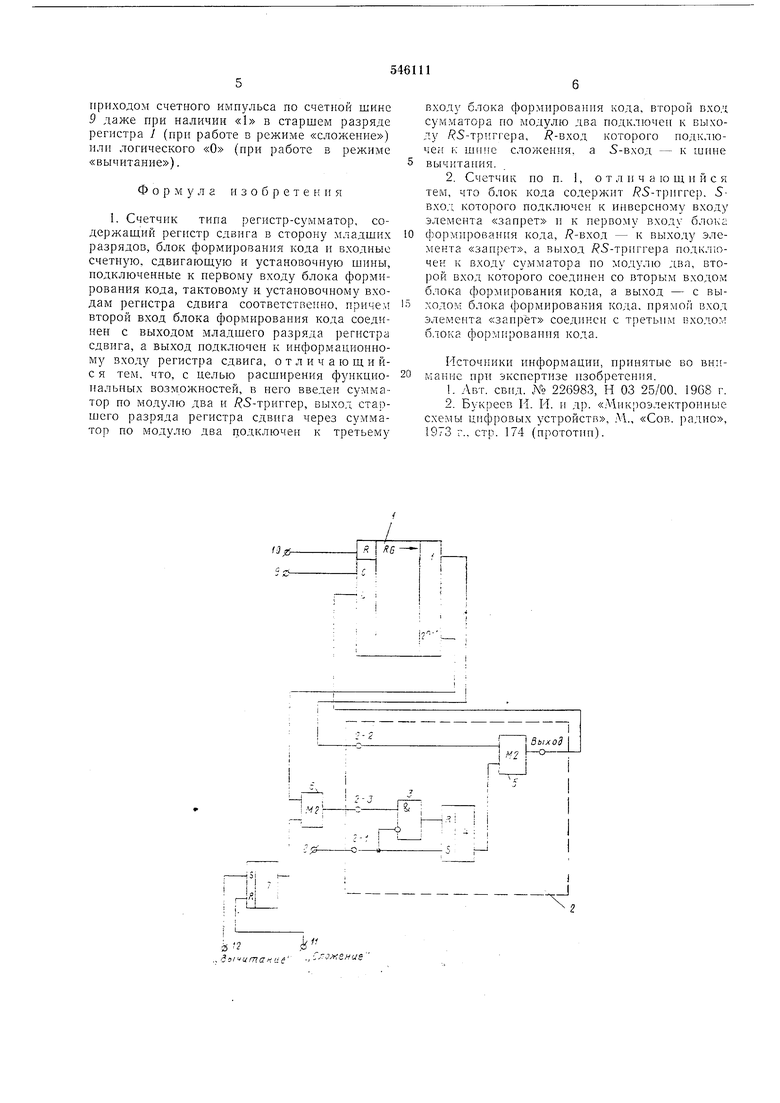

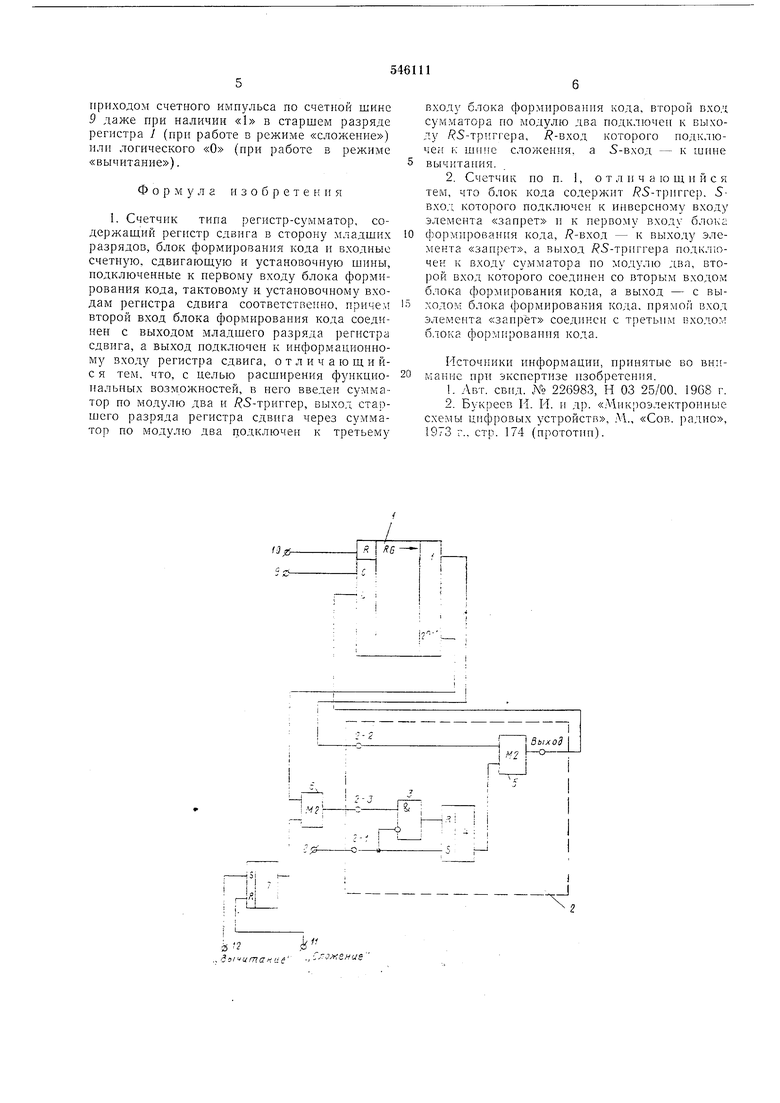

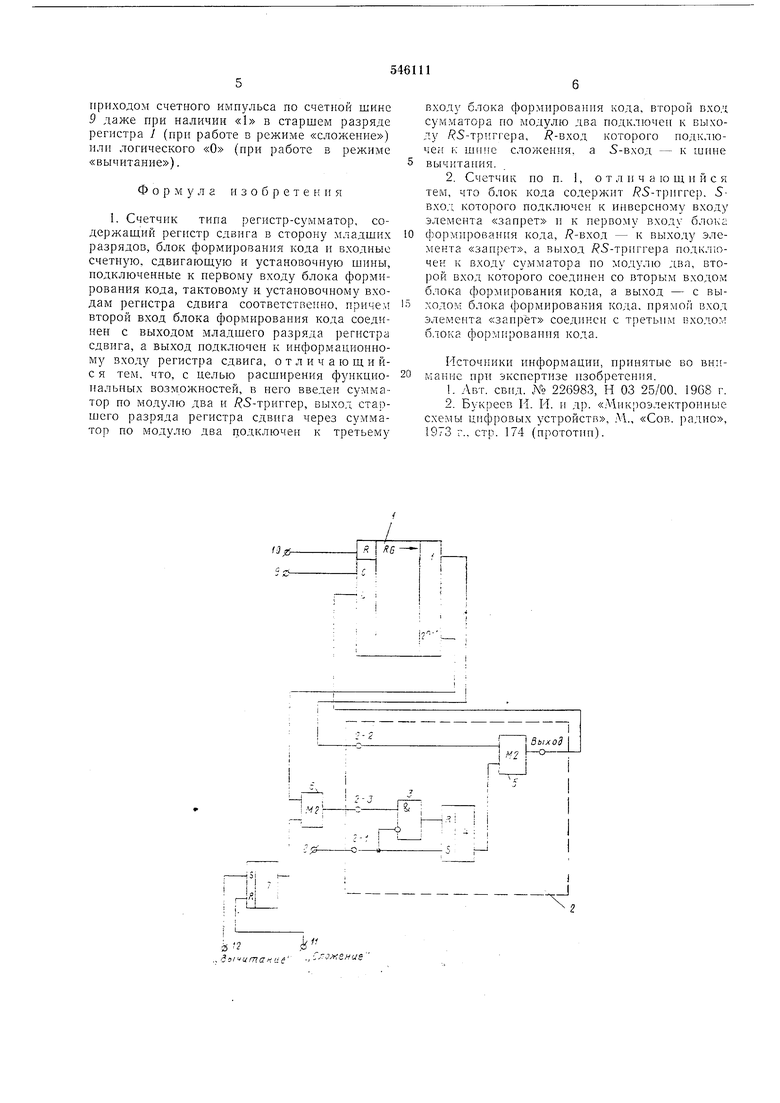

На чертеже представлеиа функциональная схема счетчика.

Счетчик содержит Я-разрядный регистр / сдвига в сторону младшего разряда, блок 2 формирования кода, состояш.ий из элемента 5 «запрет, / 5-триггера 4 и сумматора 5 по модулю два, сумматор 6 по модулю два, RSтриггер 7, счетную шину 8, сдвнгаюш,ую шину 9, установочную шину 10, шину // «сложеН1 е, /2 «вычитание.

Счетная шииа 5 счетчика подключается ко входу 2-/ блока 2 формирования кода, выход младшего разряда подключен ко входу 2-2 блока 2 формнровапия кода. Выход сумматора 6 по модулю два соединен со входом 2-5 блока 2 формирования кода. Выход блока 2 формирования кода подключен к инфорг,;ацнонному входу регистра / . Выход старшего разряда регистра / подключен к одному из входов сумматора 6 по модулю два, второй вход которого соединен с выходом «1 триггера 7, осущ,ествляюш,его управление режимом счета. Два входа упомянутого триггера соединены с управляюшими шииами «сложение //и «вычитаиие 12 устройст1за.

Выход сумматора 5 по модулю два является выходом блока 2 формирования кода, при этом одни из входов сумматора 5 является входом 2-2 блока 2 формирования кода. Информационный вход элемента 3 «запрет является входом 2-3 блока 2 формирования кода, а запреш,аюш,ий вход элемента 3 «запрета, соединенный со входом 5-триггера 4, является входом 2-/ блока 2 формирования кода. Выход элемента 3 «запрет подключен ко входу трнггера 4, выход которого соединен со вторым входом сумматора 5 но модулю два.

В режиме «сложение триггер 7 предварительно устанавливается в положение «О. Таким образом, в процессе работы на информационный вход элемента 3 «запрет через сумматор 6 по модулю два будут поступать прямые значения кода, записываемого в старший разряд регистра / сдвига. Пусть начальный код регистра О ... 00. Счетный импульс по шине 8 поступает на вход триггера 4, устаназлкт;ая его в ноложение «I, что обеспечивает, в свою очередь, инверсную обратную связь регнетра / через сумматор 5 по модулю два. Синхронно с счетным имнульсом по сд ииаю1цей шнне 9 па тактовый вход регистра У подается тактовый импульс сдвига, обеспечивая заииеь в старший разряд регистра логической «1 (зчитывая обратную ииверсную связь регистра / через сумматор 5 по модулю два). Появление единичного сигнала па выходе старшего разряда регистра / обусловливает переключение триггера 4 в состоянне «О (после окончания счетного импульса запирающего

элемента 3 «запрет). Обратная связь регистра / через сумматор 5 по модулю два становится прямой, п при подаче следующих и-1 сдвиговых импульсов но шине 9 во все разряды регистра /, за исключением младшего,

будут занисаны нули. Таким образом, после первого цикла счета в регистре / устаповится код О ... 01. С приходом второго импульса по шине 8 триггер 4 вновь устанавливается в состояние «1, поэтому после первого импульса сдвига во второл цикле счета в старший разряд регистра / запиеывается значение логического «О. После прихода второго импульсг сдвига в старший разряд записывается значение логической «1, что обусловливает переключение триггера 4 в состояние «О, поэтому обратная связь регистра / через сум.матор 5 по модулю два становится прямой. После прихода последующих ft-2 импульсов сдвига по шине 9 в регистре 7 устанавливается код О ... 010. Как видно из примера, в пачале каждого цикла счета триггер 4, управляющий обратной связью регистра У через сумматор 5 по моду.тю два, устанавливается в положеги1е «1, а установка его в положение «О происходит при появлепии первой же единицы на выходе старшего разряда регистра / в процессе работы. Отсюда следует, что после третьего цикла счета в регистре будет записаи код О ... 011, после четвертого цикла - код О ... 0100 и т. д. Таким образом, 32 каждый цикл суммирования происходит увеличепне содержимого регистра У на единицу, т. е. двоичный счет единиц.

Прн работе в режиме «вычитание, триггер 7 устанавливается в положение «1, таким образом в процессе работы на вход «RS трнггера 4- через элемент 3 «запрет и сумматор 6 но модулю два будут поступать инвертированные значения кода, записываемого в

старший разряд регистра /. Это значит, что в состояние «О триггер 4 будет переключаться в процессе счета первым же нулем, записанным в старший разряд регистра /. В остальном работа схемы не отличается от предыдхдцего режима. Таким образом, если начальное состояние регистра 1, О ... 00, то после первого цикла счета состояние регистра / будет 1 ... 11, после второго цикла счета I ... 110, после третьего 1 ... 101 и т. д., т. е.

за каждый цикл счета происходит уменьшеMi:e содержимого регистра 1 на единицу, что соответствует работе в режиме «вычитание. Включение элемента 3 «запрет в состав устройства обусловлено необходимостью надежной установки триггера 4 в состояиие «1 с

приходом счетного импульса по счетной шине 9 даже при наличии «1 в старшем разряде регистра (при работе в режиме «сложение) или логического «О (при работе в режиме «вычитание).

Формула и 3 о б р е т е к и я

1. Счетчик тииа регистр-сугутматор, содержащий регистр сдвига в сторону младших разрядов, блок формирования кода и входные счетиую, сдвигаюш,ую и установочную шины, подключенные к первому входу блока формирования кода, тактовому и установочному входам регистра сдвига соответственно, причем второй вход блока формирования кода соединен с выходом младшего разряда регистра сдвига, а выход подключен к информационному входу регистра сдвига, о т л и ч а ю щ и йс я тем, что, с целью расширения функциональных возможностей, в него введен сумматор по модулю два и 5-триггер, выход старшего разряда регистра сдвига через сумматор по модулю два цодключен к третьему

входу блока формирования кода, второй вход сумматора по модулю два подключен к выходу / 5-триггера, -вход которого подключен к шине сложения, а S-вход - к шнне

вычитаЕГИя.

2. Счетчнк по п. 1, о т л п ч а ю п; и и с я тем, что блок кода содержит / 5-триггер. 5вход которого подключен к инверсному входу элемента «запрет и к первому входу блока

формирования кода, У -вход - к выходу элемента «запрет, а выход / 5-триггера подключен к входу сумматора ио модулю два, второй вход которого соединен со вторым входом блока формирования кода, а выход - с выходом блока формирования кода, прямой вход элемента «запрёт соединен с третьим входом блока формироваиня кода.

Источники ииформации, принятые во внимание при экспертизе изобретеиия.

. Авт. свид. № 226983, Н 03 25/00. 1968 г.

2. Букреев И. И. и др. «Мнкроэлектроииые ехемь цифровых устройств, Л1., «Сов. )адио, 1973 г.. стр. 174 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетное устройство | 1984 |

|

SU1210221A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2013 |

|

RU2534971C1 |

| Преобразователь кодов | 1978 |

|

SU744548A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПАРАЛЛЕЛЬНОГО | 1973 |

|

SU362295A1 |

| Цифровой фазометр | 1980 |

|

SU932423A1 |

| Стохастический преобразователь | 1977 |

|

SU732946A1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2006 |

|

RU2306596C1 |

| Последовательное множительное устройство | 1980 |

|

SU888110A1 |

| Устройство для преобразования частоты следования импульсов в код | 1983 |

|

SU1182676A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU1013955A1 |

Авторы

Даты

1977-02-05—Публикация

1974-10-24—Подача