Изобретение относится к радиотехнике и может использоваться в когерентно-импульсных радиолокационных станциях.

Известно устройство цифровой когерентной обработки, содержащее вычислитель и два канала, каждый из которых содержит последовательно включенные фазовый детектор и аналого-цифровой преобразователь, а также последовательно включенные первый перемножитель, сумматор и блок памяти, выходы второго и третьего перемножителей соединены соответственно с вторым и третьим входами сумматора, входы фазовых детекторов каждого из каналов соединены между собой, первые входы вторых перемножителей каждого из каналов соединены между собой и с выходом первого регистра числа, первые входы третьих перемножителей каждого из каналов соединены между собой и с выходом второго регистра числа [1].

Однако данное устройство получается достаточно сложным, что приводит к невысокой надежности его работы.

Цель изобретения - повышение эффективности выделения сигналов на фоне помех.

Для этого в устройство цифровой когерентной обработки сигналов, содержащее вычислитель и два канала, каждый из которых содержит последовательно включенные детектор и аналого-цифровой преобразователь, а также последовательно включенные первый перемножитель, сумматор и блок памяти, выходы второго и третьего перемножителей соединены соответственно с вторым и третьим входами сумматора, входы фазовых детекторов каждого из каналов соединены между собой, первые входы вторых перемножителей каждого из каналов соединены между собой и с выходом первого регистра числа, первые входы третьих перемножителей каждого из каналов соединены между собой и с выходом второго регистра числа, введены последовательно включенные блок управления и блок весовых коэффициентов, а в каждый из каналов введен коммутатор, при этом выход аналого-цифрового преобразователя каждого из каналов соединен с первым входом первого перемножителя, а выход блока памяти каждого из каналов соединен с первым входом коммутатора, первый выход коммутатора каждого из каналов соединен с соответствующим входом вычислителя, второй выход коммутатора первого канала соединен с вторым входом третьего перемножителя первого канала и вторым входом второго перемножителя второго канала, второй выход коммутатора второго канала соединен с вторым входом второго перемножителя первого канала и вторым входом третьего перемножителя второго канала, второй вход блока управления соединен с вторыми входами коммутаторов обоих каналов, а выход блока весовых коэффициентов соединен с вторыми входами первых перемножителей обоих каналов.

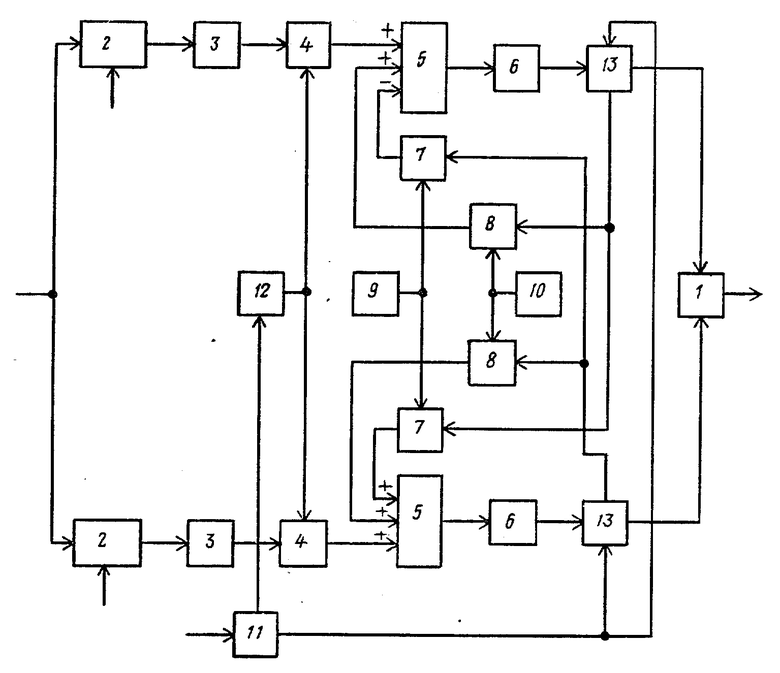

На чертеже изображена структурная электрическая схема предложенного устройства.

Устройство цифровой когерентной обработки сигналов содержит вычислитель 1 и два канала, каждый из которых содержит последовательно включенные фазовый детектор 2 и аналого-цифровой преобразователь 3, а также последовательно включенные первый перемножитель 4, сумматор 5 и блок памяти 6, выходы второго и третьего перемножителей 7 и 8 соединены соответственно с вторым и третьим входами сумматора 5, входы фазовых детекторов 2 каждого из каналов соединены между собой, первые входы вторых перемножителей 7 каждого из каналов соединены между собой и с выходом первого регистра 9 числа, первые входы третьих перемножителей 8 каждого из каналов соединены между собой и с выходом второго регистра 10 числа, а также последовательно включенные блок управления 11 и блок весовых коэффициентов 12, а в каждом из каналов - коммутатор 13, при этом выход аналого-цифрового преобразователя 3 каждого из каналов соединен с первым входом первого перемножителя 4, выход блока памяти каждого из каналов соединен с первым входом коммутатора 13, первый выход коммутатора каждого из каналов соединен с соответствующим входом вычислителя 1, второй выход коммутатора 13 первого канала - с вторым входом третьего перемножителя 8 первого канала и вторым входом второго перемножителя 7 второго канала, второй выход коммутатора 13 второго канала соединен с вторым входом второго перемножителя 7 первого канала и вторым входом третьего перемножителя 8 второго канала, второй выход блока управления 11 соединен с вторыми входами коммутаторов 13 обоих каналов, а выход блока весовых коэффициентов 12 соединен с вторыми входами первых перемножителей 4 обоих каналов.

Устройство работает следующим образом. При электронном управлении антенным лучом осуществляется дискретное сканирование диаграммы направленности. Пусть после очередного скачкообразного перемещения антенного луча в пределах его диаграммы оказалась цель. Луч в течение определенного времени остается неподвижным. При этом с выходов фазовых детекторов 2 на входы аналого-цифровых преобразователей (АЦП) 3 поступают квадратурные составляющие n отраженных от цели импульсов. Начало пачки импульсов определяется моментом дискретного перемещения луча в данное положение, конец - количеством зондирующих импульсов, излученных в данном положении. В аналого-цифровых преобразователях 3 происходит квантование выходных напряжений фазовых детекторов 2 по времени и амплитуде. Квантование по времени состоит в разбиении периода повторения T на l интервалов, величина которых определяется разрешающей способностью радиолокационной станцией по дальности. В каждом временном интервале напряжение квантуется по амплитуде на 2ν уровней, где ν - число разрядов амплитудно-цифрового преобразователя 3. Двоичные числа с выхода аналого-цифровых преобразователей 3 параллельным кодом поступают в первые перемножители 5.

В первых перемножителях 4 каждое двоичное число умножается на соответствующий весовой двоичный коэффициент аk. Соответствие весового коэффициента аk и k-го импульса пачки при известном ее начале обеспечивается с помощью блока весовых коэффициентов 12, соединенного с блоком управления 11. В каждом положении антенного луча после излучения очередного зондирующего импульса блок весовых коэффициентов 12 по командам блока управления 11 переключает весовой коэффициент. Таким образом, каждому периоду и, следовательно, каждому импульсу в пачке соответствует свой весовой коэффициент. Число весовых коэффициентов определяется длительностью пачки и равно n.

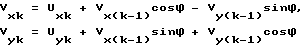

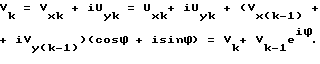

В сумматорах 5 взвешенные квадратурные проекции суммируются с задержанными в блоках памяти 6 на период повторения Т и прошедшими обработку во вторых и третьих перемножителях 7 и 8 взвешенными суммами квадратурных проекций всех предыдущих импульсов пачки. Вновь образованные суммы опять поступают в блоки памяти 6, представляющие собой цифровые линии задержки и выполненные в виде многоканальных (ν - разрядных) регистров сдвига, имеющих количество ячеек, равное числу элементов разрешения по дальности l. С выходов блока памяти 6 через коммутаторы 13 двоичные числа поступают на входы вторых и третьих перемножителей 7 и 8. С помощью этих перемножителей 7 и 8 осуществляется двумерный поворот квадратурных составляющих на угол ϕ. В первом регистре 9 числа записывается и хранится sinϕ, а во втором регистре 10 числа - cosϕ. Квадратурные составляющие на выходе первых перемножителей 4 - Uхk и Uуk, а на выходе блоков памяти 6 - Uхk и Uуk, на выходе сумматоров 5

или

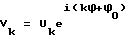

Таким образом, квадратурные составляющие с выходов блоков памяти 6 до поступления в сумматоры 5 подвергаются двумерному повороту на угол ϕ. Если угол ϕ равен доплеровскому набегу фазы сигнала за период повторения, то импульсы пачки накапливаются когерентно. При условии, что  , оба слагаемых в результате соответствующего числа двумерных поворотов вектора V на угол ϕ всегда оказываются в фазе.

, оба слагаемых в результате соответствующего числа двумерных поворотов вектора V на угол ϕ всегда оказываются в фазе.

После перемещения антенного луча в новое положение коммутаторы 13 по команде, поступившей с блока управления 11, подключают выходы блоков памяти 6 к вычислителю 1. В идеальном случае здесь должна вычисляться величина  Однако для простоты технической реализации операцию возведения в квадрат обычно заменяют операцией образования модулей квадратурных составляющих

Однако для простоты технической реализации операцию возведения в квадрат обычно заменяют операцией образования модулей квадратурных составляющих  и

и  . За время подключения блоков памяти 6 к вычислителю 1, равному одному периоду повторения, их содержимое обновляются - накопленные в предыдущем положении антенного луча суммы поступают в вычислитель 1 и затем на выход, а на их место записываются данные от первого зондирования в новом положении антенного луча. При втором зондировании коммутаторы 13 переключают выходы блоков памяти 6 к входам второго и третьего перемножителей 7 и 8, и когерентное накопление импульсов пачки осуществляется в новом положении антенного луча.

. За время подключения блоков памяти 6 к вычислителю 1, равному одному периоду повторения, их содержимое обновляются - накопленные в предыдущем положении антенного луча суммы поступают в вычислитель 1 и затем на выход, а на их место записываются данные от первого зондирования в новом положении антенного луча. При втором зондировании коммутаторы 13 переключают выходы блоков памяти 6 к входам второго и третьего перемножителей 7 и 8, и когерентное накопление импульсов пачки осуществляется в новом положении антенного луча.

Выбор весовых коэффициентов блока весовых коэффициентов 12 определяется характером помехи и осуществляется с помощью того же блока управления 11 по поступающим на него эмпирическим или каким-либо другим данным о помеховой обстановке. Наиболее эффективное выделение сигналов на фоне некоррелированных помех, имеющих равномерный спектр, обеспечивается при равновесном накоплении импульсов, т.е. при одинаковых весовых коэффициентах. При неравномерном или периодическом характере спектра помех весовые коэффициенты выбираются так, чтобы обеспечить минимальную величину пульсаций за пределами полос пропускания устройства. С этой целью весовые коэффициенты выбираются в соответствии с алгоритмами Дольф-Чебышева, Хемминга и др. В частности, использование весовых коэффициентов с симметричной огибающей в виде гауссовой кривой позволяет существенно повысить эффективность выделения сигналов на фоне коррелированных (пассивных) помех.

Предложенное устройство при соответствующем выборе весовых коэффициентов позволяет повысить эффективность выделения сигналов на фоне помех различного происхождения.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1977 |

|

SU778514A2 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1990 |

|

SU1818989A1 |

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

| СПОСОБ ОБРАБОТКИ СИГНАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2409822C1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СИГНАЛА | 2012 |

|

RU2498343C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ДИАГРАММЫ НАПРАВЛЕННОСТИ АКТИВНОЙ ФАЗИРОВАННОЙ АНТЕННОЙ РЕШЕТКИ | 2011 |

|

RU2495449C2 |

| ВЫЧИСЛИТЕЛЬ ДЛЯ АДАПТИВНОГО РЕЖЕКТИРОВАНИЯ ПОМЕХ | 2015 |

|

RU2582871C1 |

| Цифровое устройство для подав-лЕНия пАССиВНыХ пОМЕХ | 1979 |

|

SU809018A1 |

| АДАПТИВНОЕ УСТРОЙСТВО ЗАЩИТЫ РАДИОЛОКАЦИОННОЙ СТАНЦИИ ОТ ПАССИВНЫХ ПОМЕХ | 1994 |

|

RU2097781C1 |

| Устройство для подавления пассивных помех | 1977 |

|

SU687941A2 |

Устройство цифровой когерентной обработки сигналов, содержащее вычислитель и два канала, каждый из которых содержит последовательно включенные фазовый детектор и аналого-цифровой преобразователь, а также последовательно включенные первый перемножитель, сумматор и блок памяти, выходы второго и третьего перемножителей соединены соответственно с вторым и третьим входами сумматора, входы фазовых детекторов каждого из каналов соединены между собой, первые входы вторых перемножителей каждого из каналов соединены между собой и с выходом первого регистра числа, первые входы третьих перемножителей каждого из каналов соединены между собой и с выходом второго регистра числа, отличающееся тем, что, с целью повышения эффективности выделения сигналов на фоне помех, введены последовательно включенные блок управления и блок весовых коэффициентов, а в каждый из каналов введен коммутатор, при этом выход аналого-цифрового преобразователя каждого из каналов соединен с первым входом первого перемножителя, а выход блока памяти каждого из каналов соединен с первым входом коммутатора, а первый выход коммутатора каждого из каналов соединен с соответствующим входом вычислителя, второй выход коммутатора первого канала соединен с вторым входом третьего перемножителя первого канала и вторым входом второго перемножителя второго канала, второй выход коммутатора второго канала соединен с вторым входом второго перемножителя первого канала и вторым входом третьего перемножителя второго канала, второй выход блока управления соединен с вторыми входами коммутаторов обоих каналов, а выход блока весовых коэффициентов соединен с вторыми входами первых перемножителей обоих каналов.

Устройство цифровой когерентной обработки сигналов, содержащее вычислитель и два канала, каждый из которых содержит последовательно включенные фазовый детектор и аналого-цифровой преобразователь, а также последовательно включенные первый перемножитель, сумматор и блок памяти, выходы второго и третьего перемножителей соединены соответственно с вторым и третьим входами сумматора, входы фазовых детекторов каждого из каналов соединены между собой, первые входы вторых перемножителей каждого из каналов соединены между собой и с выходом первого регистра числа, первые входы третьих перемножителей каждого из каналов соединены между собой и с выходом второго регистра числа, отличающееся тем, что, с целью повышения эффективности выделения сигналов на фоне помех, введены последовательно включенные блок управления и блок весовых коэффициентов, а в каждый из каналов введен коммутатор, при этом выход аналого-цифрового преобразователя каждого из каналов соединен с первым входом первого перемножителя, а выход блока памяти каждого из каналов соединен с первым входом коммутатора, а первый выход коммутатора каждого из каналов соединен с соответствующим входом вычислителя, второй выход коммутатора первого канала соединен с вторым входом третьего перемножителя первого канала и вторым входом второго перемножителя второго канала, второй выход коммутатора второго канала соединен с вторым входом второго перемножителя первого канала и вторым входом третьего перемножителя второго канала, второй выход блока управления соединен с вторыми входами коммутаторов обоих каналов, а выход блока весовых коэффициентов соединен с вторыми входами первых перемножителей обоих каналов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Попов Д.И., Федоров В.А | |||

| Подавление пассивных помех в цифровой системе однократный режектор - когерентной накопитель | |||

| Труды ЛИАП, вып | |||

| Прибор для очистки паром от сажи дымогарных трубок в паровозных котлах | 1913 |

|

SU95A1 |

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1998-11-27—Публикация

1976-07-12—Подача