Изобретение относится к вычкслитель ной технике и предназначено для измер&ния характеристик случайных, явлений. Оно может быть использовано при проведении испытаний надежности аппаратуры, в ядерной физике и других областях науки и техники. Известно устройство для проведения статистических испытаний, содержащее триггеры предварительного хранения, счетчики-делители частоты, коммутаторы, блок оперативной памяти m . Недостатком этого устройства является большой объем оборудования на каж дый канал счета и, соответственно, высо кая стоимость. При построении устройств на сотни и тьгсячи каналов счета стремятся найти более экономичные решения путем разделения, с одной стороны, функции счета а с другой, запоминания и вывода резуль татов между счетчиком и блоком операти ной памяти. Из известных устройств наиболее близким по технической сущности к изобретению является устройство,которое содержит группу триггеров, информационные входы которых соединены с информационным входом устройства, выходы подключены к соответствующим входам коммутатора, счетчик, соединенный двусторонними связями с блоком памяти, и счетчик адреса 2 . Недостатком устройства является от носительно малая частота счета по каналам, так как количество импульсов, которое может быть сосчитано по каждому каналу в единицу времени, определяется формулой где 2 - время обращения к блоку памяти;N - количество каналов. Целью изобретения является повышение быстродействия устройства.

Поставленная цель постигается тем, что в устройство ввеаены дополнительные группы триггеров, коммутаторы, счетчики, элементы запоминания переполнений, элемеЕ1ты И, НЕ, первый аешифратор, соециненный с группой млапших разрядов счетчика адреса, второй аешифратор, соединенный с группой старших разрядов счетчика адреса и переключатель, причем информационные входы триггеров каждой дополнительной группы соединены с соответствующим информационным входом устройства, выходы подключены к входам соответствующего коммутатора, а счетчи ки соединены двусторонними связями с блоком памяти, управляющие входы каждого коммутатора и триггеров каждой группы подсоединены к выходу первого дешифратора, выход старшего разряда каждого из счетчиков через соответствующий элемент запоминания переполнений соединен с первым входом соответствующего первого элемента И, второй вход которог через последовательно соединенные элемент НЕ и переключатель соединен с выходом второго дешифратора, счетный вход каждого счетчика подключен к выходам соответствующих первого и второго эле- ментов И, первые входы вторых элементо И соединены с выходом второго дешифратора, выход каждого коммутатора подключен ко второму входу соответствующего второго элемента И.

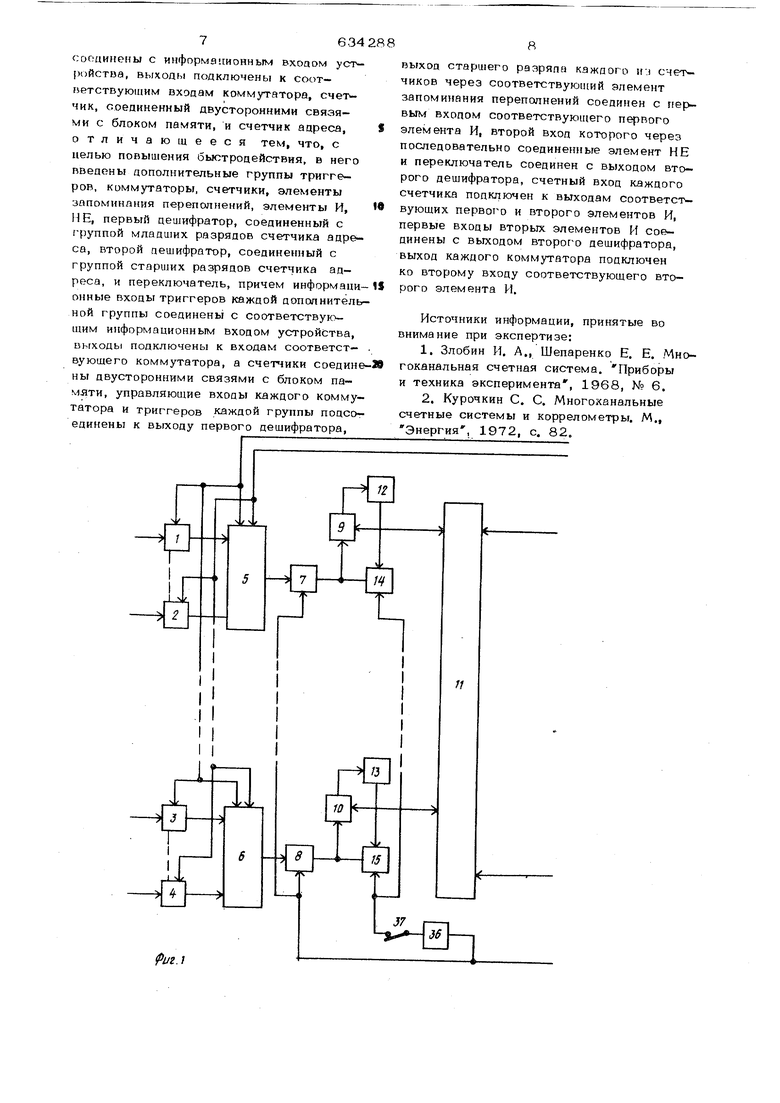

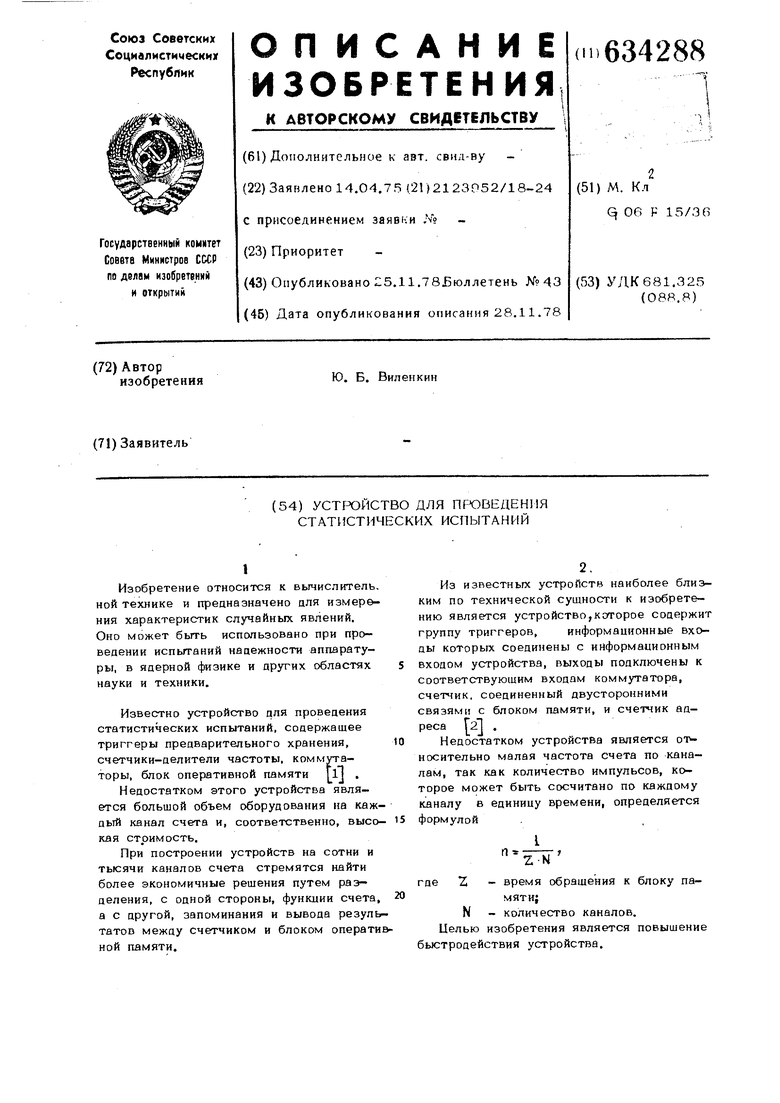

Схема устройства представлена на фиг. 1 и 2,

Источники импульсных сигналов соединены с триггерами 1, 2, 3, 4 нескольких групп, которые соединены с коммутаторами 5, 6, Выходы коммутаторов 5, 6 соединены со входами элементов И 7, 8, выходы которых соединены со счётными входами счетчиков 9, 10. Входы и выходы разрядов счетчиков соединены с соответствующими .выходами и входами разрядов блока 11 памяти. Выходы старшего разряда счетчиков 9, Ю соединены с элементами запоминания переполнений 12, 13, которые соединены со входами элементов И 14, 15, выходы которых соединены со счетными входами счетчиков 9, 10.

Входы младших и старших разрядов адреса блока памяти соединены соответственно с выходами разрядов счетчика адреса (на схеме счетчик адреса показай в виде двух счетчикдв 16 и 17).

Выходы разрядов счетчиков 16 и 17 соединены также с дешифраторами 18 и

19. Счётный вход и выход переполнения счетчика 16 через переключатель 20 соединены со счет 1ЫМ входом счетчика 21, имеющего то же число разрядов, что и счетчик 16. В режиме счета переключатель 20 соединяет выход переполнения счетчика 16 со счетным входом счетчика 21, а в режиме вывода результатов счета переключатель 20 соединяет счетные входы счетчиков 16 и 21, выходы разрядов которых соединены со схемами сравнения 22, 23, 24. Схема сравнения 23 имеет вход разрешения от схемы сравнения 22, а схема сравнения 24 имеет вход разрешения от схемы сравнения 23.

Прямые и инвертированные выходы схем 22, 23, 24 соединены с соответствующими парами элементов И 25 и 26, 27 и 28, 29 и ЗО, другие входы которы Соединены с несколькими выходами дешифратора 19, соответствующими первым по порядку состояниям счетчика 17. Оотальные выходы дешифратора 19, кроме выхода, соответствующего последнему состоянию счетчика 17, соединены с элементом ИЛИ 31, который через элемент И 32, второй вход которого соединен с генератором тактовых импульсов (ГТИ) 33 соединен со счетным входом счетчика 17. Входы элемента ИЛИ 31 соединены также с выходами элементов И 26, 28 ЗО. Выходы элементов И 25, 27, 29 и последний выход дешифратора 19 соединены с элементом ИЛИ 34, который через эл&мент И 35, второй вход которого соединен с генератором 33, соединен со сче- ньпи входом счетчика 16 и входом сброса счетчика 17. Выход дешифратора 19 соединен со входами элементов И 7, 8 и элементом НЕ 36, который через переклю чатель 37 соединен со входами элементов И 14, 15. Переключатель 37 замкнут в режиме счета и разомкнут в режиме вывода его результатов.

Устройство для проведения статистических испытаний работает следующим образом. В каждом тактовом интервале генератора 33 происходит обращение к слову блока 11 памяти, считывание из него кодов в счетчики 9, 10, выработка в них новых кодов и запись их в выбранное слово блок 11 памяти. При сброшенном состоянии счетчика 17 происходит обращение к последовательным словам первого массива слов. При этом дешифратор 18 обеспечивает подключение через коммутаторы 5, 6 к элементам И 7, 8 соответствующих триггеров из 1, 2, 3, 4, Если эти триггеры находятся в еди личном состоянии, то есть, если за инте вал разрешения системы на них поступили импульсы приращения, то в соответст вующие счетчики из 9, 10 поступают счетные ик.лульсы. Если после обращения к очерепному слову первого массива не имеет место совпадение кодов, поступающих на схему сравнения 22, то включается элемент И 25, элемент ИЛИ 34 и очередной тактовый импульс проходит через элемент И 35 на счетный вход счетчика 16 и на вхоа сброса счетчика 17, После этого происходит обращение к следующему ело- ву первого массива и опрос следующих триггеров. Если имеет место совпадение кодов, поступающих на схему 22, то включается элемент И 26, элемент ИЛИ 31 и элемент И 32 пропускает очередной тактовый импульс на счетный вход счетчика 17, а состояние счетчика 16 за тактовы интервал не изменяется. .Счетчик 17 выходит из первого состояния и разрешающий сигнал снимается с элементов И 7, 8 и через элемент НЕ 36 подается на элементы И 14, 15. В следующем тактовом интервале происходит обращение к слову второго массива с тем же поря ковым номером в массиве. . К копам, хранящимся в этом слове, добавляются сигналы переноса, хранящиеся в элементах запоминания переполнений 12, 13. Если в тактовом интервале, в котором происходит обращение к слову второго массива, имеет место совпадение кодов, поступающих на схемы 22 и 23, то в конце тактового интервала происходит добавление 1 в счетчик 17 и в следующем тактовом интервале происходит обращение к тому же номеру слова третьего массива. Если в такте обращения к слову второго массива совпадение на обеих схемах 22 и 23 не будет иметь место, то произойдет добавление 1 в счетчик 16, сброс счетчика 17, опрос следующей группы триггеров и- обращение к следующему слову первого массива. Если при обращении к слову третьего массива имеет место совпадение на сх& мах 22, 23, 24, то в следующем такте произойдет обращение к слову четвертого массива с тем же порядковым номером в нем. Если при обращении к слову третьего массива совпадение на схемах 22. 6 8 23, 24 не имеет место, то в конне имеет место, це такта происходит сброс счетчика происходит сброс 17 и добавление в счетчик 16, опрос следующей группы входных каналов -и обращение к соответствующему слову первого массива. После обращения к слову четвертого массива благодаря соединению соответству-; ющих номеров выходов дешифратора 19с элементом ИЛИ 31, происходит добавление 1 Б счетчик 17. При достижении счетчиком 17 последнего состояния благодаря соединению последнего выхода дешифратора 19 с элементом ИЛИ 34 происходит сброс счетчика 17 и добавление I в счетчик 16, после чего в следующем такте произойдет обращение к следующему номеру слова первого массива. Поате окончания цикла обращений ко всем словам первого массива сигнал переполнения со счетчика 16 добавляет 1 в счетчик 21, и начинается новый циют опроса входных коммутаторов и обращений к словам первого массива, в котором аналогичным образом происходит обращение к словам других массивов. Описанное построение устройства обеопечивает то, что каналы счета образуют ся одноименными разрядами всех,массивов. При выводе результатов счета последовательно опрашиваются одинаковые номера Слов всех-массивов, в результате чего выводятся результаты счета , по m каналам. После этого номер опрашиваемых слов в массивах увел1гчивается на 1 и т.д. 0.0 вывода результатов счета по всем каналам. Такой режим работы устройства обеспечивается тем, что из-за соединения при выводе результатов счетных входов счетчиков 16 и 21 их коды всегда совпадают. Поэтому после опроса слова первого массива опрашиваются слова с тем же номером в дру1-их массивах. При опросе последнего массива бл годаря включению эл-емента И 35 от дешифратора 19 происходит добавление 1 в счетчике 16 и 21, затем обеспечивается последовательный опрос слов массивов с новым номером в этих массивах. Так как в режиме вьтода элементы И 14, 15 отключены, то накопленные результаты при выводе не изменяются. Формула изобретения Устройство аля проведения статистиеских испытаний, содержащее группу риггеров, информационные входы которых

7634

сог;ци е 1Ы с информационным вхоаом устройства, выходр) подключены к соот- (ьетствующим входам коммутатора, счетчик, соединенный двусторонними связями с блоком памяти, и счетчик ацреса, отличающееся тем, что, с целью повышения быстродействия, в него введены дополнительные группы триггеров, коммутаторы, счетчики, элементы запоминания переполнений, элементы И, НЕ, первый дешифратор, соединенный с группой младших разрядов счетчика адреса, второй дешифратор, соединенный с группой старших разрядов счетчика адреса, и переключатель, причем информаци- онные входы триггеров каждой дополнительной группы соединены с cooTBeTCTsyKvишм информационным входом устройства, выходы подключены к входам соответст- вующего коммутатора, а счетчики соедине ны двусторонними связями с блоком памяти, управляющие входы каждого коммутатора и триггеров .каждой группы подсоединены к выходу первого дешифратора.

8

выход старшего разряпа каждого и:) счетчиков через соответствующий элемент запоминания переполнений соединен с входом соответствующего первого элемента И, второй вход которого через последовательно соединенные элемент НЕ и переключатель соединен с выходом второго дешифратора, счетный вход каждого счетчика подключен к выходам соответствующих первого и второго элементов И, первые входы вторых элементов И соединены с выходом второго дешифратора, выход каждого коммутатора подключен ко второму входу соответствующего второго элемента И,

Источники информации, принятые во внимание при экспертизе:

1.Злобин И. А., Шепаренко Е. В. Многоканальная счетная система. Приборы

и техника эксперимента, 1968, № 6,

2.Курочкин С. С. Многоканальные счетные системы и коррелометры. М., Энергия , 1972, с. 82.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для последовательного программного управления | 1983 |

|

SU1126928A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для ввода информации | 1983 |

|

SU1151942A1 |

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

| Способ селективной записи импульсных процессов и устройство для его осуществления | 1988 |

|

SU1636800A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1985 |

|

SU1259274A1 |

Авторы

Даты

1978-11-25—Публикация

1975-04-14—Подача