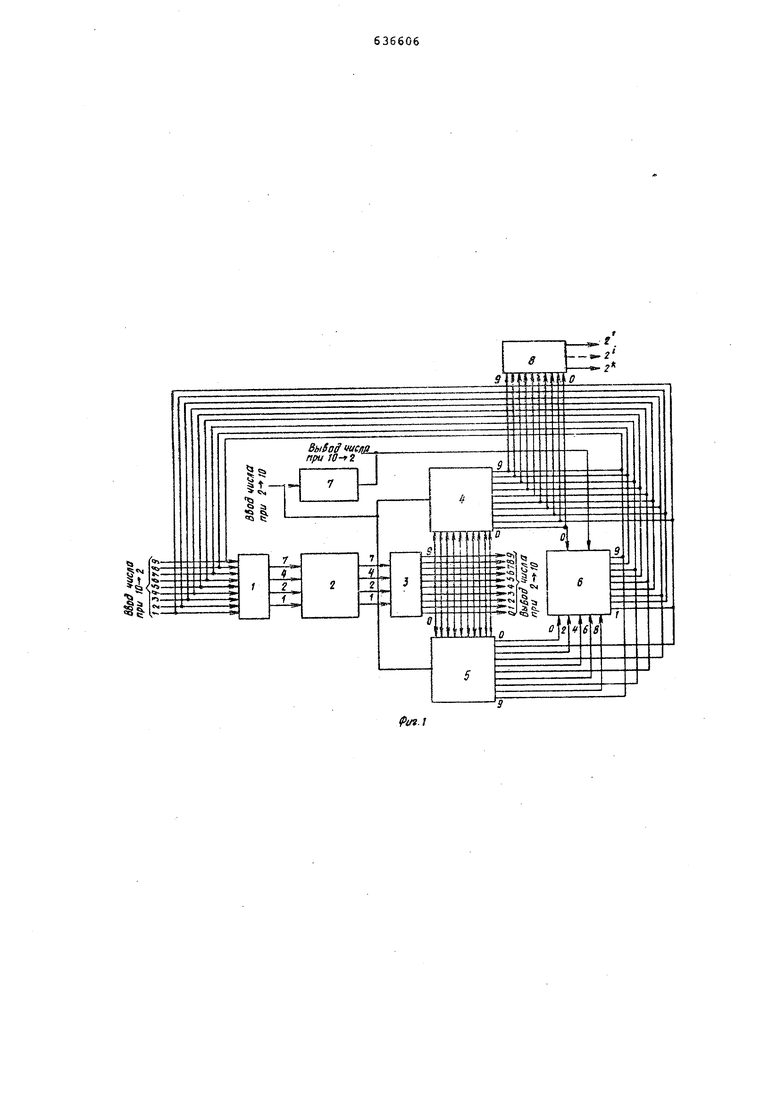

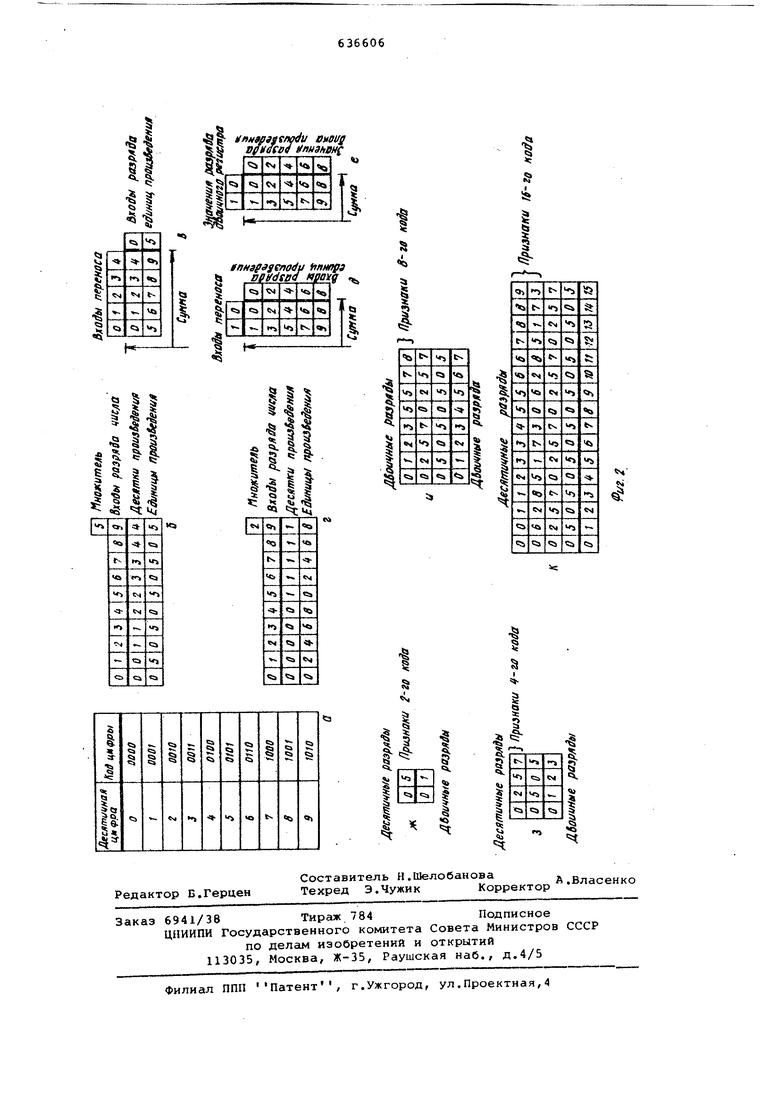

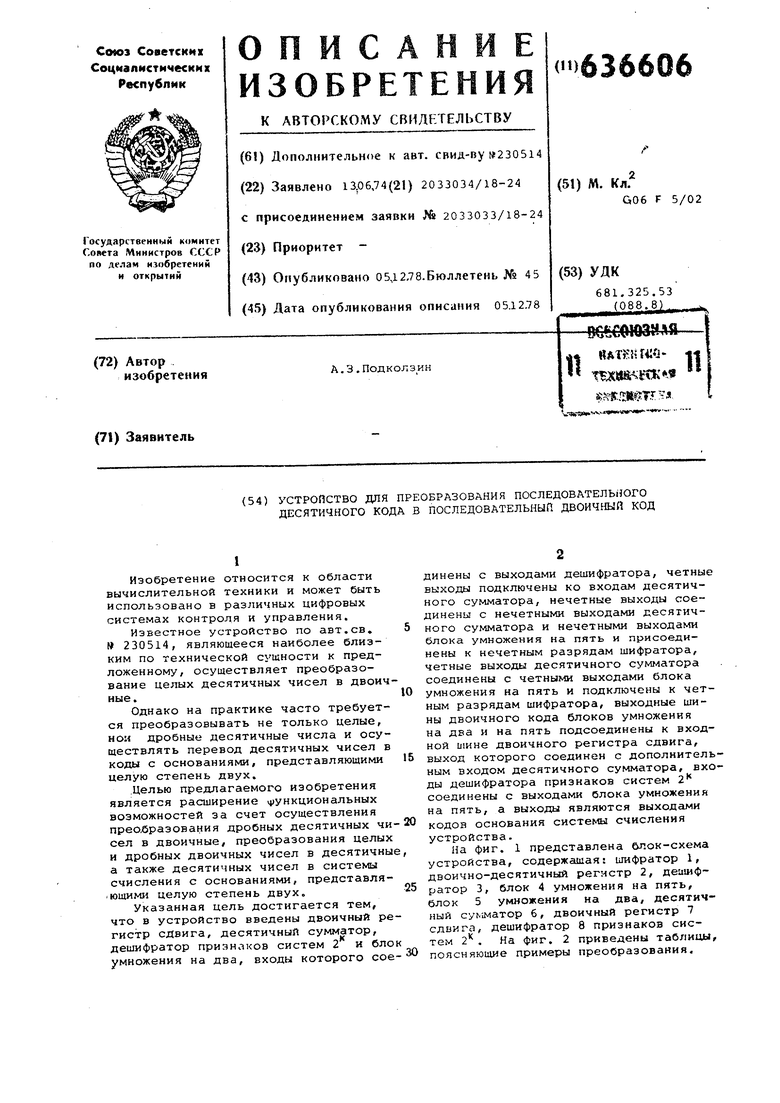

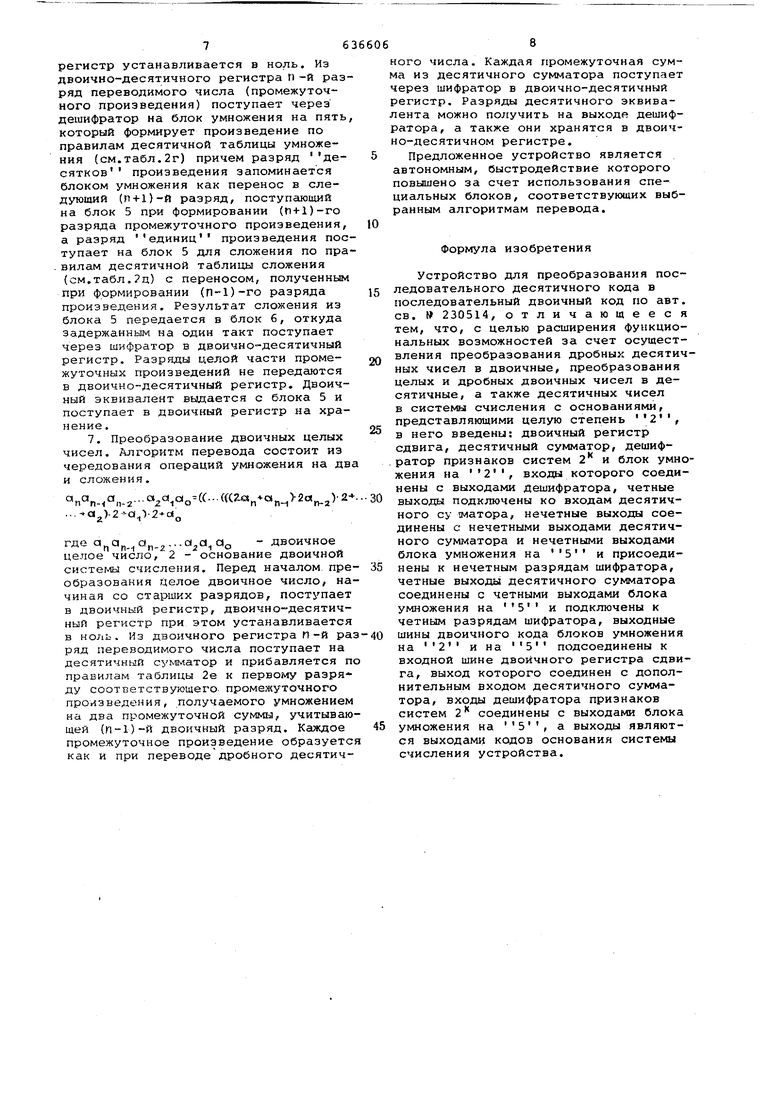

Изобретение относится к области вычислительной техники и может быть использовано в различных цифровых системах контроля и управления. Известное устройство по авт.св. 230514, являющееся наиболее близким по технической сущности к предложенному, осуществляет преобразование целых десятичных чисел в двоич ные . Однако на практике часто требуется преобразовывать не только целые, НОИ дробные десятичные числа и осуществлять перевод десятичных чисел в коды с основаниями, представляющими целую степень двух. .Целью предлагаемого изобретения является расширение ч ункциональных возможностей за счет осуществления преобразования дробных десятичных чи сел в двоичные, преобразования целых и дробных двоичных чисел в десятичны а также десятичных чисел в системы счисления с основаниями, представля-ющими целую степень двух. Указанная цель достигается тем, что в устройство введены двоичный ре гистр сдвига, десятичный сумматор, дешифратор признаков систем 2 и бло умножения на два, входы которого сое динены с выходами дешифратора, четные выходы подключены ко входам десятичного сумматора, нечетные выходы соединены с нечетными выходами десятичного сумматора и нечетными выходами блока умножения на пять и присоединены к нечетным разрядам шифратора, четные выходы десятичного сумматора соединены с четными выходами блока умножения на пять и подключены к четным разрядам шифратора, выходные шины двоичного кода блоков умножения на два и на пять подсоединены к входной шине двоичного регистра сдвига, выход которого соединен с дополнительным входом десятичного сумматора, входы дешифратора признаков систем 2 соединены с выходами блока умножения на пять, а выходы являются выходами кодов основания системы счисления устройства. На фиг. 1 представлена блок-схема устройства, содержащая: шифратор 1, двоично-десятичный регистр 2, дешифратор 3, блок 4 умножения на пять, блок 5 умножения на два, десятичный cyNiMaTOp б, двоичный регистр 7 сдвига, дешифратор 8 признаков систем 2 . На фиг. 2 приведены таблицы, поясняющие примеры преобразования. а Устройство состоит из специализирован ных блоков, каждый из которых может быть реализован на стандартных элементах вычислительной техники. Для преобразования десятичных чисе в одну из систем - двоичную, четверичную, восьмиричную, шестнадцатиричную - принята единая тактовая система управления: 4 х 13 х 29, де: ч - количество тактовых импульсов с периодом следования Т, необходимое для умножения на пять или на два одного разряда переводимого числа или промежуточного резул тата; 13 - количество серий А, необходимое для умножения на пять переводимого целого десятич ного числа или промежуточ. ного результата при получении 16-ричного кода; при умножении на два и при получении 8-ричных, 4-ричных, двоичных чисел требует ся меньшее число серий А; 13 серий А составляют одну управляющую серию В; количество серий А для П-разрядного десятичного кода зависи в общем случае, от того кода, в како это число переводится 29 - количество серий В, необход мое для получения двоичного эквивалента 9-разрядного де сятичного числа; для И -разрядного десятичног целого числа это количество определяется показателем ст пени двух, ближайшей к деся тичному числу. Рассмотрим основные режимы работы пре/иТЯгаемого устройства: 1. П чюбразование десятичных целы чисел ь двоичные. ;и1горитм перевода десятичного целого числа в двоичное используется тот же, что и в известном устройстве - число последователь но умножается на пять; очередное произЧЗ ведение образуется умножением на пять предыдущего произведения с отброшенным 1лладшим разрядом; умножение продолжается до тех пор, пока последнее произведение не станет равньли нулю. Двоичным разрядам соответствуют (см. таол. младшие (отбрасываемые) разряды произведений : если младший разряд произведения равняется пяти, то с;оответствующий двоичный разряд рав-. няется единице; если младший разряд произведения равен нулю то и соответствующий двоичный разряд равен нулю; при этом старший разряд двоичного эквивалента соответствует млад/д1ему ра ряду предпоследнего промежуточного произведения. Перед началом преобразования 9-раз рядное десятичное целое число поступает, начиная с младших разрядов, через ujuOpaTOp 1 по шинам подачи разря6дов извне в двоично-десятичный регистр 2. В процессе 1реобразования участвует все устройство. Из двоичнодесятичного регистрап -и разряд переводимого числа {промежуточного произведения) поступает через дешифратор на блок умножения на пять, где формируется произведение по правилам десятичной таблицы умножения (см,табл. 26); причем разряд десятков произведения запоминается блоком умножения как перенос в следующий (П+1)-Й разряд, а разряд единиц складывается по правилам десятичной таблицы сложения (см.табл.2в) с переносом, полученным при формировании (n-l)-ro разряда произведения. Результат сложения из блока умножения на пять передается через шифратор в двоично-десятичный регистр. Младшие разряды промежуточных произведений не передаются в двоично-десятичный регистр, так как шифратор при этом заблокирован. Разг ряды двоичного эквивалента вьадаются с дешифратора признаков систем 2. 2. Преобразование десятичных целых чисел в четверичные. Алгоритм перевода состоит в двукратном умножении числа на пять. При каждом первом умножении на пять младшие разряды промежуточных произведений не отбрасываются. При каждом втором умножении на пять у промежуточных произведений отбрасываются два младших разряда, по значени}.) старшего из которых (см. табл.2з) формируется определенный разряд четверичного эквивалента. Умножение продолжается до тех пор, пока последнее произведение не станет равным нулю. При этом старшему разряду четверичного эквивалента соответствуют два младших разряда предпоследнего промежуточного произведения. Перед началом преобразования 8-разрядное десятичное целое число, начиная с младших разрядов, через шифратор поступает в двоично-десятичный регистр, занимая в нем все разряды. кроме старшего, в который записывается ноль. Каждое промежуточное произведение образуется также, как и в предыдущем примере. Каждое нечетное произведение передается в двоично-десятичный регистр с сохранением всех разрядов. Два младших разряда каждого четного произведения не передаются в двоично-десятичный регистр и поступают последовательно на дешифратор ггризнаков систем 2. Шифратор при отбрасывании двух младших разрядов четного произведения остается заблокированным. 3, Преобразование десятичных целых чисел в восьмиричные. Алгоритм перевода заключается в трехкратном умножении десятичного целого числа на пять. При каждом первом и втором умножениях на пять младиие разряды промйжуточных произведений не отбрасынаются. При каждом тратьйм умножении на пять у промежуточных произведеяиП отбрасываются три младших разряда, по значению старшего из которнх {см.табл.2и) формируется определенный разряд восьмиричного эквивалента. Умножение продолжается до тех пор, пока последнее произведение не станет равным нулю. При этом стар шему разряду восьмиричного эквива.Г1ента соответствуют три младших разряда предпоследнего промежуточного произведения. Перед началом преобразования 7разрядное целое десятичное число пос тупает, с млал1иих разрядов, через шифратор в двоично-десятичный регист занимая в нем все разряды, кроме дву старших, в которые записывается ноль Промежуточные произведения 1,2,4,5, 7,8,..25, 26 передаются в двоично-десятичний регистр с сохранением всех разрядов. Промежуточные произведения 3,6,9...27 передаются в двоично-десятичный регистр без трех разрядов. Эти три младшие разряда по ледовательно поступают на дешифратор признаков систем 2, который учитывает только старший по значению из этих трех разрядов. Шифратор при отбрасывании трех младших разрядов каж дого 3 ,6 , 9 ,12 . . .27 произведения остается заблокированньлм. 4. Преобразование десятичных целы чисел в шестнадцатиричные. Алгоритм перевода сводится к четырехкратному последовательному умножению числа на пять. При каждом первом, втором и третьем умножениях на пять младшие разряды промежуточных произведений не отбрасываются. При каждом четвер том умножении на пять у промежуточных произведений отбрасываются четы ре младших разряда, по значениям дв старших из которых (см.табл.2к) формируется определенный разряд шестнад цатиричного эквивалента. Признак око чания перевода -- нулевое последнее произведение. При этом cTapnieMy раз ряду шестнадцатиричного эквивалента соответствуют четыре младших разряд предпоследнего промежуточного произ ведения. Перед началом преобразования 6-разрядное целое десятичное чи ло поступает, начиная с младших раз рядов, через шифратор в двоично-дес тичный регистр, занимая в нем все разряды, кроме трех старших, заполняемых нулями. Промежуточные произведения 1, 2 , 3 , 5 , 6 , 7 . . . 25 , 26 , 27 пере даются в двоично-десятичный регистр с сохранением всех разрядов Промежуточние произведения 4,8,12...24, 28 передаются в двоично-десятичный регистр без 4eTbjpex младших разрядо два старших по значению из которых постулаьзт нгз ди-: :иф1 агор признаков систем 2. и1ифратор при отбрасывании четырех младших разрядов каждого 4, 8,,. 24,28 произведения остается забокированным. 5.Преобразование двоичных ;:робных чисел. Алгоритм перевода состоит из чередования операций умножения на пять и сложения: ,в,в,в...в.в,.в„Ч(с...,1 .,)К-.-.о Б 5- о В215 1ов) 5 где: 10 - основание десятичной системы счисления; 0,В,В.гВз...В„ двоичное дробное число; дая преобразования дробных двоичных чисел по описанному алгоритму 9-разрядному десятичному дробному числу (помешенному в двоично-десятичный регистр) должно соответствовать 9-разрядное двоичное дробное число. Перевод дробних двоичных чисел, имеющих больше девяти двоичных разрядов возможен, если в устройство ввести схему округления десятичного дробного числа, образуемого при переводе. Перед началом преобразования 9-разрядное дробное двоичное число поступает с младших разрядов по шине подачи разрядов в двоичный регистр, двоично-десятичный регистр устанавливается в ноль. Из двоичного регистра П-разряд переводимого числа поступает на десятичный сумматор и прибавляется к соответствующему нулевому разряду прог.1ежуточного произведения, получаемого умножением на пять промежуточной суммы, учитывагошчй (Ц-1)-й двоичный разряд. Каждое промежуточное произведение образуется, как и при переводе целого десятичного числа. Промежуточное произведение из блока 4 передается через десятичный сумматор и шифратор в двоично-десятичныП регистр. В соответствующий разряд промежуточного произведения записывается с помощью десятичного сумматора соответствующее значение двоичного разряда переводимого числа. Разряды десятичного эквивалента можно получить на выходе де1:11 фратора, кроме того, они хранятся в двоичис-десятичном регистре. 6.Преобразование десятичных дробных чисел. Алгоритм перевода состоит из последовательного умножения на два десятичного дробного числа. Двоичным разрядаги соответствуют отбрасываемые разряды целой части промежуточных произведений, при этом старший разрял двоичного эквивалента соответствует разряду целой части первого промежуточного произведения. Перед началом преобразования 9-разрядное дробное десятичное число поступает, с м.ч.х1шнх разрядов, через шифратор 1 в двоично-десятичный регистр, двоичный регистр устанавливается в ноль. Из двоично-десятичного регистра П-и разряд переводимого числа (промежуточного произведения) поступает через дешифратор на блок умножения на пять который формирует произведение по правилам десятичной таблицы умножения (см.табл.2г) причем разряд десятков произведения запоминается блоком умножения как перенос в следующий (п+1)-й разряд, поступающий на блок 5 при формировании (п+1)-го разряда промежуточного произведения, а разряд единиц произведения пос тупает на блок 5 для сложения по пра . вилам десятичной таблицы сложения (см.табл.2ц) с переносом, полученным при формировании (n-l)-ro разряда произведения. Результат сложения из блока 5 передается в блок б, откуда Задержанным на один такт поступает через шифратор в двоично-десятичный регистр. Разряды целой части промежуточных произведений не передаются в двоично-десятичный регистр. Двоичный эквивалент вьщается с блока 5 и поступает в двоичный регистр на хранение. 7. Преобразование двоичных целых чисел. Алгоритм перевода состоит из чередования операций умножения на дв и сложения. «nanM«n-z-«a i«o f-f« -«n «n-,2c.j)-2 -Ю,,)( где .а....,ао - двоичное целое число, 2 - основание двоичной систег ш счисления. Перед началом пре образования Целое двоичное число, на чиная со старших разрядов, поступает в двоичный регистр, двоично-десятичный регистр при этом устанавливается в ноль. Из двоичного регистра П-и ра ряд переводимого числа поступает на десятичный сумматор и прибавляется п правилам таблицы 2е к первому разряду соответствующего- промежуточного произведения, получаемого умножением на два промежуточной суммы, учитываю щей (п-1)-й двоичный разряд. Каждое промежуточное произведение образуетс как и при переводе дробного десятич68 ного числа. Каждая промежуточная сума из десятичного сумматора поступает через шифратор в двоично-десятичный регистр. Разряды десятичного эквиваента можно получить на выходе дешифратора, а также они хранятся в двоично-десятичном регистре. Предложенное устройство является автономным, быстродействие которого повышено за счет использования специальных блоков, соответствующих выбранным алгоритмам перевода. Формула изобретения Устройство для преобразования последовательного десятичного кода в последовательный двоичный код по авт. св. 230514, отличающееся тем, что, с целью расширения функциональных возможностей за счет осуществления преобразования дробных десятичных чисел в двоичные, преобразования целых и дробных двоичных чисел в десятичные, а также десятичных чисел в системы счисления с основаниями, представляющими целую степень 2, в него введены: двоичный регистр сдвига, десятичный сумматор, дешифратор признаков систем 2 и блок умножения на 2 , входы которого соединены с выходами дешифратора, четные выходы подключены ко входам десятичного су 1матора, нечетные выходы соединены с нечетными выходами десятичного сумматора и нечетными выходами блока умножения на 5 и присоединены к нечетным разрядам шифратора, четные выходь десятичного сумматора соединены с четными выходами блока умножения на и подключены к четным разрядам шифратора, выходные шины двоичного кода блоков умножения на 2 и на 5 подсоединены к входной шине двоичного регистра сдвига, выход которого соединен с дополнительным входом десятичного сумматора, входы дешифратора признаков систем 2 соединены с выходами блока умножения на 5, а выходы являются выходами кодов основания системы счисления устройства.

Ипнваввупмч onOl/O я/чаЫ пнзнвнс

I

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь п-разрядного десятичного кода в пятиричный | 1976 |

|

SU645150A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

| Устройство для преобразования последовательного двоичного кода в десятичный | 1977 |

|

SU622076A1 |

| Преобразователь десятичной дробиВ пяТиРичНую | 1979 |

|

SU796837A1 |

| Устройство для преобразования последовательного двоичного кода в десятичный код | 1978 |

|

SU752324A2 |

| Устройство для преобразования позиционного десятичного кода в двоичный код | 1977 |

|

SU622075A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1979 |

|

SU773616A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1285604A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

Авторы

Даты

1978-12-05—Публикация

1974-06-13—Подача