.(54) ПРЕОБРАЗОВАТЕЛЬ ДЕСЯТИЧНОЙ ДРОБИ В ПЯТИРИЧНУЮ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь п-разрядного десятичного кода в пятиричный | 1976 |

|

SU645150A1 |

| Устройство для преобразования последовательного десятичного кода в последовательный двоичный код | 1974 |

|

SU636606A2 |

| Устройство для преобразования последовательного двоичного кода в десятичный | 1977 |

|

SU622076A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU888102A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый КОд | 1979 |

|

SU849199A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

1

Изобретение относится к автомати.ке и вычислительной технике и может быть использовано при построении десятичных преобразователей.

Известен преобразователь десятичного кода в двоичный, содержащий сдвиговый регистр, блоки коррекции и блок управления ij.

Недостаток этого преобразователя состоит в большой сложности и невысокой скорости преобразования.

Наиболее близким по технической сущности к предлагаемому является преобразователь десятичного кода в пятиричный, содержащий двоично-десятичный сдвиговый регистр, дешифратор двоично-десятичного кода, входы которого соединены с выходами двоичиодесятичного сдвигового регистра, и шифратор десятичного кода в двоичнодесятичный, первая группа входов которого является группой входов преобразователя, а выходы соединены со входами двоично-десятичного сдвигового регистра 2 .

Недостаток данного преобразователя состоит в невозможности преобразования дробных чисел и в невысокой скорости преобразования, связаннойс прохождением полученной тетради

выходного кода через сдвиговый регистр прежде чем он поступит в выходной регистр.

Цель изобретения - увеличение быстродействия.

Поставленная цель достигается за счет того, что в преобразователь десятичной дроби в пятиричную, содержащий двоично-десятичный сдвиговый

O регистр, дешифратор двоично-десятичного кода, входы которого соединены с выход 1ми двоично-десятичного сдвигового регистра, ишифратор десятичного кода в двоично-десятичный, первая группа входов которого является группой входов преобразователя, а выходы соединены со входами двоичнодесятичного сдвигового регистра,введены блок деления на два и регистр

0 пятиричного кода, управляющий вход которого соединен с управляющим выходом блока деления на два, разрядные выходы регистра пятиричного кода являются выходами преобразователя,

5 информационные выходы блока деления на два соединены со второй группой входов шифратора; десятичного кода в двоично-десятичный, информационные входы регистра пятиричного кода

0 соединены с информационными вьоходами

старших разрядов блока вьвделения на два.

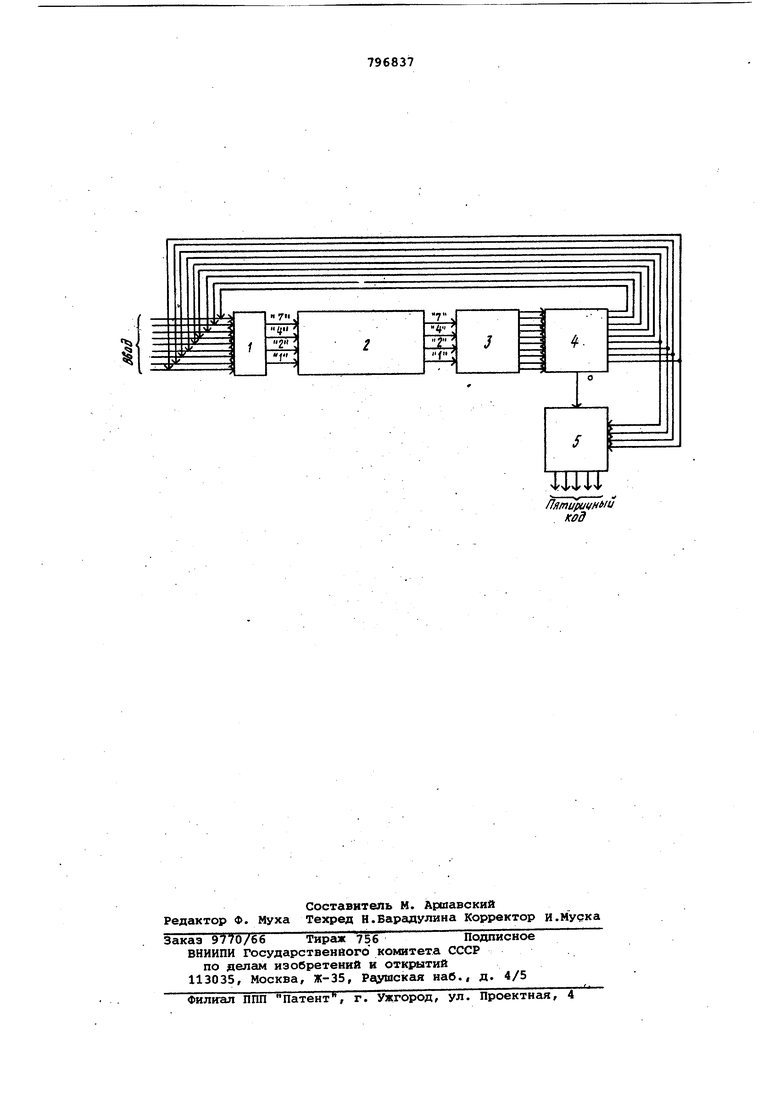

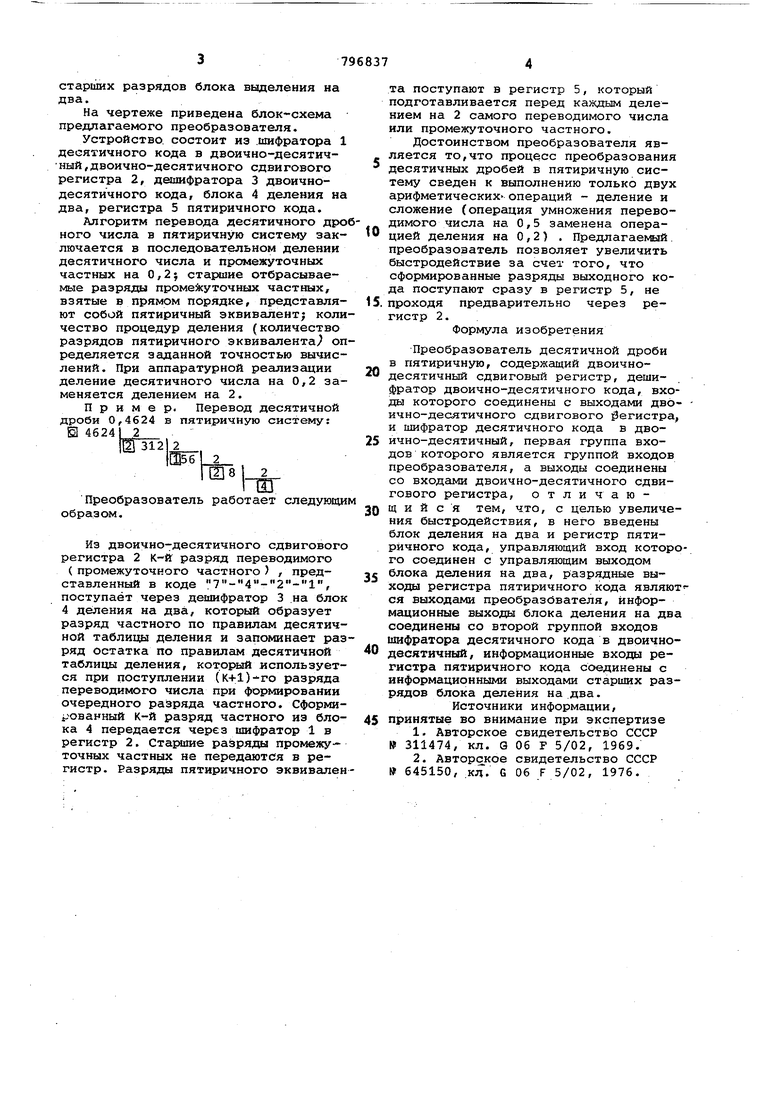

На чертеже приведена блок-схема предлагаемого преобразователя.

Устройство состоит из .ьшфратора 1 десятичного кода в двоично-десятичный,двоично-десятичного сдвигового регистра 2, дыаифратора 3 двоичнодесятичного кода, блока 4 деления на два, регистра 5 пятиричного кода.

Алгоритм перевода десятичного дроного числа в пятиричную систему заключается в последовательном делении десятичного числа и промежуточных частных на 0,2; старадие отбрасываемые разряды промежуточных частных, взятые в прямом порядке, представляют собой пятиричный эквивалент; количество процедур деления (количество разрядов пятиричного эквивалента определяется заданной точностью вычислений. При аппаратурной реализации деление десятичного числа на 0,2 заменяется делением на 2.

Пример. Перевод десятичной дроби 0,4624 в пятиричную систему: т 4624

1ШЗГ212

Ш 2

Преобразователь работает следующи образом.

Из двоично-десятичного сдвигового регистра 2 к-й разряд переводимого ( промежуточного частного ) , представленный в коде , поступает через дешифратор 3 .на блок 4 деления на два, который образует разряд частного по правилам десятичной таблищл деления и запоминает разряд остатка по правилам десятичной таблицы деления, котор 1й используется при поступлении (К+1)-го разряда переводимого числа при формировании очередного разряда частного. Сформированный К-й разряд частного из блока 4 передается через шифратор 1 в регистр 2. Стараие разряды промежуточных частных не передаются в регистр. Разряды пятиричного эквивалента поступают в регистр 5, который подготавливается перед каждым делением на 2 самого переводимого числа или промежуточного частного.

Достоинством преобразователя является то,что процесс преобразования десятичных дробей в пятиричную систему сведен к выполнению только двух арифметических- операций - деление и сложение (операция умножения переводимого числа на 0,5 заменена операО цией деления на 0,2) . Предлагаемый, преобразователь позволяет увеличить быстродействие за счет того, что сформированные разряды выходного кода поступают сразу в регистр 5, не

Формула изобретения

Преобразователь десятичной дроби в пятиричную, содержащий двоично0 десятичный сдвиговый регистр, дешифратор двоично-десятичного кода, входы которого соединены с выходами двоично-десятичного сдвигового регистра, и шифратор десятичного кода в дво5 ично-десятичный, первая группа входов которого является группой входов преобразователя, а выходы соединены со входами двоично-десятичного сдвигового регистра, отличаюQ щ и и с я тем, что, с целью увеличения быстродействия, в него введены блок деления на два и регистр пятиричного кода, управляющий вход которого соединен с управляющим выходом

c блока деления на два, разрядные выходы регистра пятиричного кода являют ся выходами преобразователя, информационные выходы блока деления на два соединены со второй группой входов шифратора десятичного кода в двоично0 десятичный, информационные входы регистра пятиричного кода соединены с информационными выходами старших разрядов блока деления на два.

Источники информации,

5 принятые во внимание при экспертизе

Пятири н ги код

Авторы

Даты

1981-01-15—Публикация

1979-02-12—Подача