Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ.

Целью изобретения является повышение быстродействия и расширение функциональных возможностей путем обеспечения преобразования дробных чисел,,

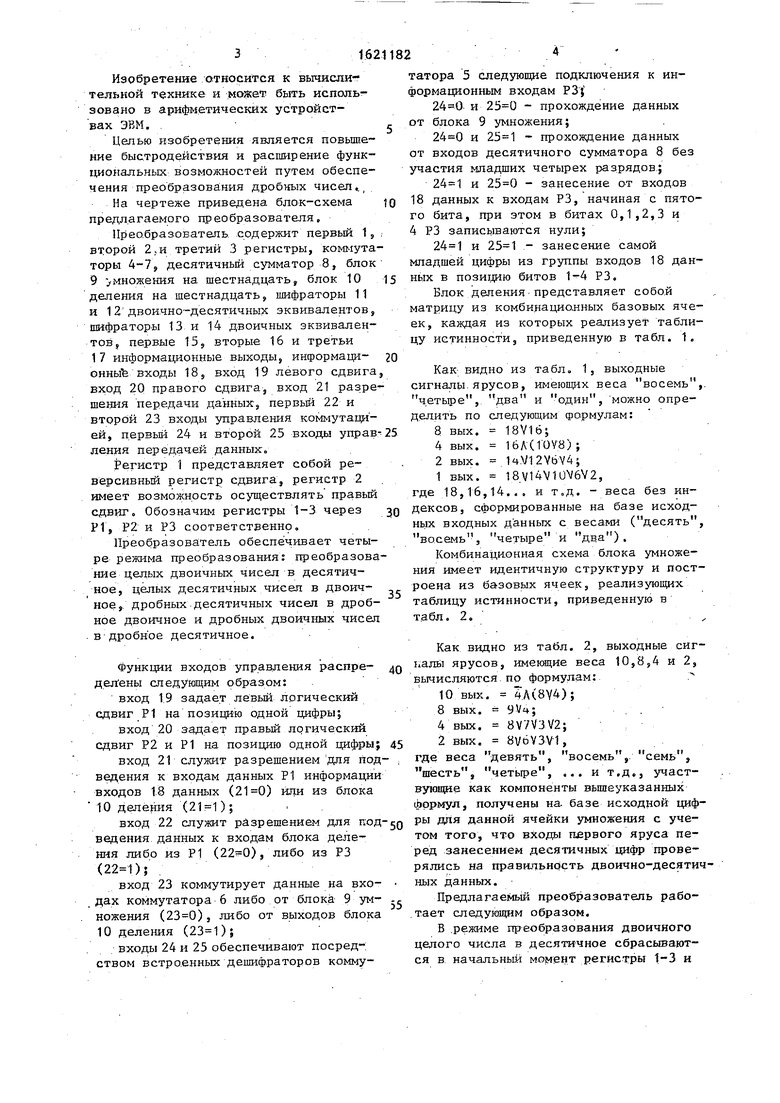

На чертеже приведена блок-схема предлагаемого преобразователя.

Преобразователь содержит первый 1, второй 2,и третий 3 регистры, коммутаторы 4-75 десятичный сумматор 8, блок 9 множения на шестнадцать, блок 10 деления на шестнадцать, шифраторы 11 и 12 двоично-десятичных эквивалентов, шифраторы 13 и 14 двоичных эквивалентов, первые 15, вторые 16 и третьи 17 информационные выходы, информаци- онные входы 18, вход 19 левого сдвига вход 20 правого сдвига, вход 21 разрешения передачи данных, первый 22 и второй 23 входы управления коммутацией, первый 24 и второй 25 входы управ ления передачей данных.

Регистр 1 представляет собой реверсивный регистр сдвига, регистр 2 имеет возможность осуществлять правый сдвиг. Обозначим регистры 1-3 через Р1, Р2 и РЗ соответственно.

Преобразователь обеспечивает четыре режима преобразования: преобразование целых двоичных чисел в десятичное, целых десятичных чисел в двоич

иое, дробных десятичных чисел в дробное двоичное и дробных двоичных чисел в дробное десятичное.

Функции входов управления распре- делены следующим образом:

вход 19 задает левый логический сдвиг Р1 на позицию одной цифры;

вход 20 задает правый логический сдвиг Р2 и Р1 на позицию одной цифры;

вход 21 служит разрешением для подведения к входам данных Р1 информации входов 18 данных () или из блока 10 деления ();

татора 5 следующие подключения к информационным входам РЗ}

и - прохождение данных от блока 9 умножения;

и - прохождение данных от входов десятичного сумматора 8 без участия младших четырех разрядов;

и - занесение от входов 18 данных к входам РЗ, начиная с пятого бита, при этом в битах 0,1,2,3 и 4 РЗ записываются нули;

и - занесение самой младшей цифры из группы входов 18 данных в позицию битов 1-4 РЗ,

Блок деления представляет собой матрицу из комбинационных базовых ячеек, каждая из которых реализует таблицу истинности, приведенную в табл. 1.

Как видно из табл. 1,

выходные

сигналы ярусов, имеющих веса восемь, и один, можно опре четыре,

два

делить по следующим формулам: 8 вых. 18V16; 4 вых. 16Д(ЮУ8) ; 2 вых. l4V12VbV4;

1вых. 18V14V1UV6V2,

где 18,16,14... и т.д. - веса без индексов, сформированные на базе исходных входных данных с весами (десять, восемь, четыре и два).

Комбинационная схема блока умножения имеет идентичную структуру и построена из базовых ячеек, реализующих таблицу истинности, приведенную в табл. 2.

Как видно из табл. 2, выходные сиг- ьалы ярусов, имеющие веса 10,8,4 и 2, вычисляются по формулам:

10 вых. Л(8У4);

8 вых.

4 вых. 8V7V3V2;

2вых. 8V6V3V1,

где веса девять, восемь, семь, шесть, четыре, ... и т.д., участвующие как компоненты вышеуказанных сйормул, получены на базе исходной циф

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Арифметическое устройство с фиксированной точкой | 1984 |

|

SU1241230A1 |

| Устройство для преобразования двоичных чисел в двоично-десятичные и обратно | 1983 |

|

SU1142826A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый | 1979 |

|

SU798800A1 |

| Устройство для преобразования двоичных чисел в двоично-десятичные и обратно | 1986 |

|

SU1388995A1 |

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1977 |

|

SU739523A1 |

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ, Цель изобретения - повышение быстродействия и расширение функциональных возможностей путем обеспечения преобразования дробных чисел. Поставленная цель достигается тем, что в преобразователь, содержащий регистры 1-3, коммутаторы 4-7, десятичный сумматор 8, шифраторы двоичных эквивалентов 13,14, шифраторы двоично-десятичных эквивалентов 11,12, дополнительно введены блок умножения на шестнадцать 9 и блок деления на шестнадцать 10-, 1 ил., 2 та бл.

вход 22 служит разрешением для под-5о Ры япя данной ячейки умножения с учеведения данных к входам блока деления либо из Р1 (), либо из РЗ ();

вход 23 коммутирует данные на входах коммутатора 6 либо от блока 9 умножения (), либо от выходов блока 10 деления ();

входы 24 и 25 обеспечивают посредством встроенных дешифраторов комму55

том того, что входы первого яруса перед занесением десятичных цифр проверялись на правильность двоично-десятич ных данных.

Предлагаемый преобразователь работает следующим образом.

В режиме преобразования двоичного целого числа в десятичное сбрасываются в начальный момент регистры 1-3 и

том того, что входы первого яруса перед занесением десятичных цифр проверялись на правильность двоично-десятичных данных.

Предлагаемый преобразователь работает следующим образом.

В режиме преобразования двоичного целого числа в десятичное сбрасываются в начальный момент регистры 1-3 и

по разрешению исходные данные от группы входов 18 подводятся к Р2 и Р1. При этом самая старшая тетрада запи- .сывается в Р2, для которой десятичный эквивалент всегда совпадает с двоичным, а последующие цифры записываются в Р1 до предпоследней цифры включительно. Далее первая старший цифра от Р2 совместно с нулевыми цифрами РЗ подаются на вход блока 9 умножения, По разрешению выход блока 9 подается на вход сумматора 8, а на вторые входы - выходы шифраторов 11 и 12, при

162

этом через выходы шифратора 12 посту- jr ка 10 деления. Выходы блока 10, соотпает десятичный эквивалент второй старшей цифры преобразуемого двоичного числа, а сигналы на выходе шифратора 11, подключенного через второй

вход сумматора к четырем старшим раз- 20 ям четырех младших цифр частного Р1

рядам сумматора 8, равны nyjuo, так как в позиции самой младшей тетрады Р1 записаны нули. Затем по разрешениям , и и при включении синхросигналов РЗ и Р2 перпое значение промежуточного произведения, равное сумме произведении первоп старшей цифры на шестнадцать плюс десятичный эквивалент второй старшей цифры исходного двоичного числа, записывается в РЗ и Р2. Одновременно с приемом в РЗ и Р2, посредством сигнала производится левый логический сдвиг Р1, при котором позицию старшей тетрады Р1 занимает очередная

шифратор 13 выдает на выходы 16 очередную (вторую) цифру результата пре образования и т.д. 1 В начале преобразования дробных

25 десятичных чисел сбрасываются Р1 , Р2 и РЗ и на входах управления задаются уровни , и , при этом исходное дробное число, подведенное от группы входов 19, записывается в

Зо РЗ со сдвигом вправо на пять разрядо После этого на входах управления уст навливаются коды и , по которым к выходам коммутаторов 5 по ра решению подводится первое значе ние промежуточного (произведение исстаршая цифра преобразуемого операн- ходного числа на 16) преобразования.

да.

На втором такте работы преобразователя результат промежуточного преобразования первого такта, записанный в РЗ и Р2, умножается на шестнадцать блоком 9 и через коммутатор 6 подводится к первому входу сумматора 8, к второму входу которого подведен десятичный эквивалент очередной старшей цифры с выходов шифратора 12 и т.д.

В режиме преобразования десятичных целых чисел в двоичное исходный десятичный операнд от группы входов 18 записывается в ранее сброшенные Р1 и Р2. При этом входы управления возбуждаются следующими уровнями: , , и и как при режиме преобразования двоичных целых чисел самая старшая цифра располагается в Р2, остальные - в Р1 до предпоследней тетрады включительно. После этого по значениям четырех младших цифр Р1, начиная от предпоследней

1182

10

тетрады, шифраторы 13 вычислят первую шестнадцатиричную цифру результата . При этом использовано известное положение из теории чисел: остаток, получаемый при делении на шестнадцать сколь угодно большого десятичного числа, равен остатку, который получился бы при делении четырех младших цифр этого большого числа. В дальнейшем исходное целое число с выходов Р2 и Р1 (без содержимого последней тетраты Р1) по разрешению через коммутатор 7 подводится на входы бловетствующие целой части от деления на шестнадцать, по разрешению подводятся на Р1, одновременно сбрасывается Р2. После этого по новым значенишифратор 13 выдает на выходы 16 очередную (вторую) цифру результата преобразования и т.д. 1 В начале преобразования дробных

5 десятичных чисел сбрасываются Р1 , Р2 и РЗ и на входах управления задаются уровни , и , при этом исходное дробное число, подведенное от группы входов 19, записывается в

о РЗ со сдвигом вправо на пять разрядов. После этого на входах управления устанавливаются коды и , по которым к выходам коммутаторов 5 по разрешению подводится первое значение промежуточного (произведение ис0

При этом коммутация выходных данных блока 9 умножения к входам данных РЗ выполнена такой, что выход первой ячейки блока умножения с весом десять поступает па вход нулевого бита РЗ, а выход второй старшей ячейки блока умножения с весами восемь, четыре, два и один соответствен5 но заносится в разряды 1,2,3 и 4 РЗ. К четырем входам первых двух ячеек блока умножения подводятся логические нули, а исходное число на вход блока умножения подводится, начиная от вхо0 дов старшего третьего столбца, и поэтому две старшие ячейки выпочняют функцию формирователей десятичного эквивалента текущих значении двоичных цифр результата,

После расположения данных и Bt-fpa- ботки разрешений на входах 23, 24 и 25 через время, равное задержкам блоков 9,6 и 5, производится запуск синхросигнала РЗ, где устанавливается

5

первое значение промежуточного произведения, после чего выходы 0,1,2,3,4 регистра РЗ через шифратор 14 на выходы 16 выдают первую цифру шестнадцатиричной дроби, а выходы 5,6,,.,п разрядов РЗ подводятся к входам блока 9 умножения как компонента промежуточного произведения для выполнения второго такта преобразования, описанного выше при получении первой дробной шестнадцатиричной цифры.

В начале преобразования дробных двоичных чисел сбрасываются регистры 1,2 и 3. Управляющие входы возбуждаются уровнями , , , и . После этого от группы входов 18 данных и Р2 и Р1 до предпоследней цифры включительно записывается исходный двоичный операнд, а в позиции битов 1,2,3,4 РЗ заносится самая младшая цифра этого операнда. Затем через небольшую задержку, дважды возбуждая сигнал 20, в самой младшей тетраде Р1 оказывается вторая младшая цифра исходного операнда. После этого на входе 24 устанавливается уровень логического нуля.

Через время, равное задержкам блоков 7,10 и 6, к первому входу сум-

iI такт

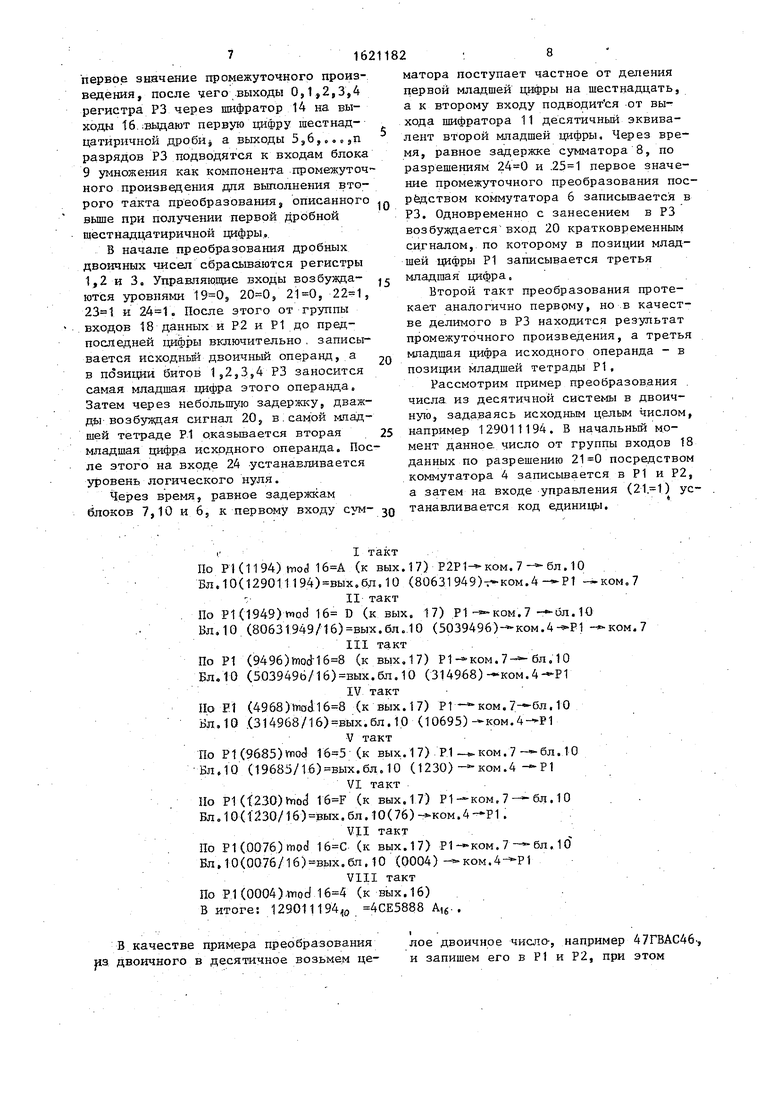

По Pi(1194) mod (к вых.17) . 7 бл. 1 Бл,10(129011194)вых.бл,10 (80631 949)г-ком.4

IIтакт

По P1(1949) 16 D (к вых. 17) Р1 -ком.7 --бл.

Бл.10 (80631949/16)вых.бл.10 (5039496).

IIIтакт

По Р1 (9496 )тосМ (к вых. 17) . бл. 10 Бл.10 (503949ь/16)вых.бл,10 (314968) .

IVтакт

Но Ft (4968) (к вых.17) Р1 - ком. 7-бл. 10 Бл.10 (3149 э8/16)вых.бл.10 (10695) -ком.4-НР1

Vтакт

По PlC9685)vnocJ (к вых.17) Р1 . 7 --бл. 10 Вл.Ю (19685/16)вых.бл„10 (1230) - ком.4 - Р1

VIтакт

По Р1 (mo)biod (к вых. 17) Р1- ком. 7- бл. 10 Бл.10ШЗО/16)вых.бл.10(76).4- Р1 .

VIIтакт

По Р1 (0076) mod (к вых. 17) .. 10 Бл,10(007б/1б)вых„бл.10 (0004) .

VIIIтакт По Р1(0004)mod (к вых.16)

В итоге: 129011194W 4CE5888 А,б .

В качестве примера преобразования из двоичного в десятичное возьмем це

матора поступает частное от деления первой младшей цифры на шестнадцать, а к второму входу подводился от выхода шифратора 11 десятичный эквивалент второй младшей цифры. Через время, равное задержке сумматора 8, по разрешениям и первое значение промежуточного преобразования посредством коммутатора 6 записывается в РЗ. Одновременно с занесением в РЗ возбуждается вход 20 кратковременным сигналом, по которому в позиции младшей цифры Р1 записывается третья младшая цифра.

Второй такт преобразования протекает аналогично первому, но в качестве делимого в РЗ находится результат промежуточного произведения, а третья младшая цифра исходного операнда - в позиции младшей тетрады Р1,

Рассмотрим пример преобразования числа из десятичной системы в двоич- задаваясь исходным целым числом, например 129011194. В начальный момент данное число от группы входов 18 данных по разрешению посредством коммутатора 4 записывается в Р1 и Р2, а затем на входе управления () устанавливается код единицы.

i

лое двоичное число-, например 47ГВАС46,

и запишем его в Р1 и Р2, при этом

старшая цифра этого набора 4 распола- 9 и 12 подводятся цифры 4 и 7, в РЗ - гается в четырех разрядах Р2, а ос- нулевая информация , а на входе тальные цифры, начиная с цифры 7, - в 21 1 - для прохождения компонента от Р1. В исходный момент к входам блоков с младшей тетрады сумматора к Р2.

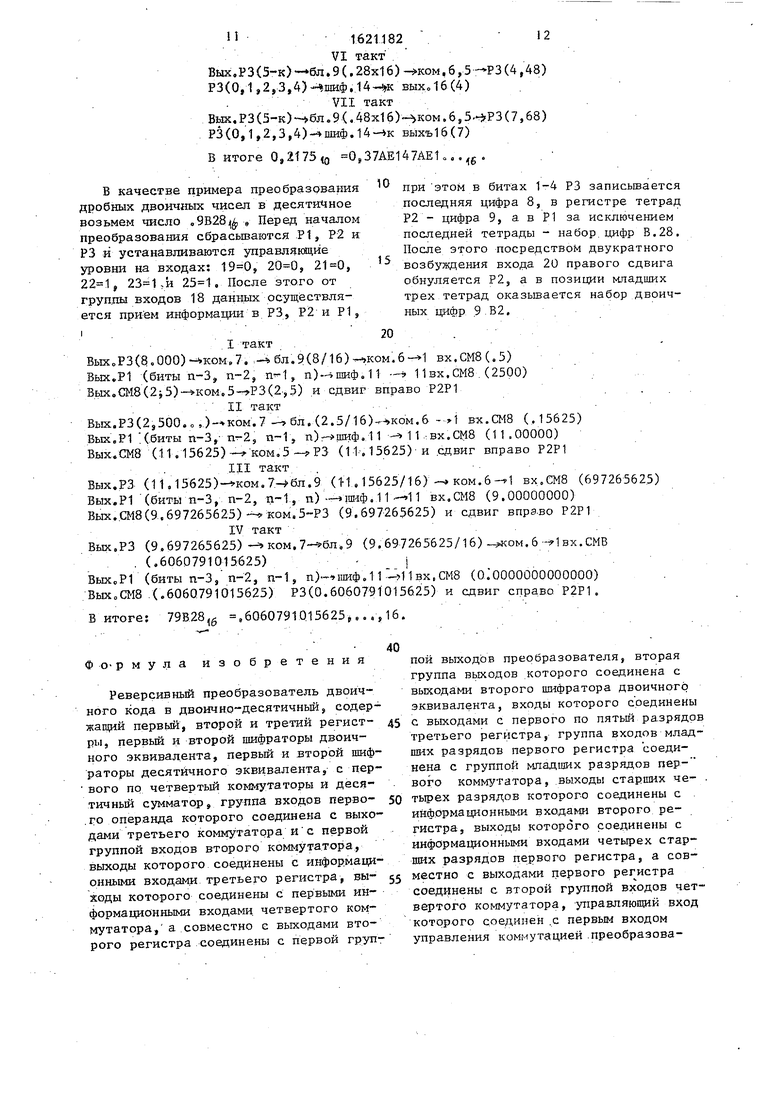

Iтакт

РЗР2- бл.9 (000004x16)- вых,бл..6 -1 вх.СМ8(64) Р1 (0-3) .12(00007)-ком.5 вх.СМ8(07) Вых.СМВШ) - РЗР2 и сдвиг Р1 влево

IIтакт

РЗР2- бл.9 (71x16) --вых.бл.9,.6-1 вх.СМ8 (1136) Р1(-03) -бл.12(Р)-ком.5-11 ВХ.СМ8 (0015) Вых, CMB(f151) и сдвиг Р1 влево

IIIтакт

РЗР2-бл ,9(1151x16) вых. бл. 9 -ком. 6 -1 вх, СМ8 ( f 8416) Р1 (0-3) -бл.12(В).5 - 11 ВХ.СМ8 (00011) Вых.СМ8(18427)-РЗР2 и сдвиг Р1 влево

IVтакт

РЗР2- бл. 9(1 8427x16) вых. бл.9-ком. 6- 1вх.СМ8 (294832) Р1(0-3)-бл.12(А)-ком.5 --11 ВХ.СМ8 (000010) Вых. СМ8( 294842)-РЗР2 и сдвиг Р1 влево

Vтакт

РЗР2-бл.9 (294842x16)- вых. бл, 9-ком.6 --1вх.СМ8(471 7472) Р1 (0-3) -бл. 12 (С)-ком. 5-Н1 вх. СМ8(0000012) Вых.СМ8(4717484) - -РЗР2 и сдвиг Р1 влево

VIтакт

РЗР2-бл.9(471 7484x16)- вых.бл.9 .6 .СМ8(75479744) Р1 (0-3) -бл. 12(4) - ком. 5-11 ВХ.СМ8 (00000004) Вых.СМ8(75479748)--РЗР2 и сдвиг Р1 влево

VIII такт

РЗР2-бл. 9(754 79748x16)-вых.бл. 9- ком. 6-1 вх. ©18(1207675968) Р1(0-3).12(7).5-М1 вх.СМ8(0000000007) Вых.СМ8(1207675974)

В итоге: 47ГВАС46 6 1207675974

i

В качестве преобразования дробного , и и указанное число десятичного числа возьмем 0,2175w , 40 через группы входов 18 записывается в В исходный момент сбрасываются Р1, Р2 соответствующие разряды РЗ (со сдвии РЗ, возбуждаются входы управления гом вправо).

t

Iтакт

Вых.РЗ(56б,...,К).9(.2175х1б).6,(3,48) Р3(,3,4). вых.16(3)

IIтакт

Вых.РЗ(5-к).9(.48х1б).6,(7,68) Р3(0,1,2,3,4) шиф. вых, 16(7)

IIIтакт

Вых.РЗ(5-к).9(.68х16).6,5 (10,88) Р3(0,,3,4). вых,1б(А)

такт

Вых.РЗ(5-к).9(.88х16)ком.6,,08) Р3(0,1,2,3,4).14--). к вых. )

VI такт

Вых.РЗ()(.08х1б)ком.6,(1,28) Р3(0,1,2,3,4) пнф. вых,16(1)

и

111621182 12

VIтакт

Вых.РЗ(5-к).9(.28х16),6,(4,48) Р3(0,1,2,3,4)-%шиф. выхо1б(4)

VIIтакт

Вых.РЗ(5-к).9(.48х16)ком.6,5.(7,68) Р3(0,1,2,3,4). выхъ1б(7)

В итоге 0,2175,0 0,37AE147AEt,. ме .

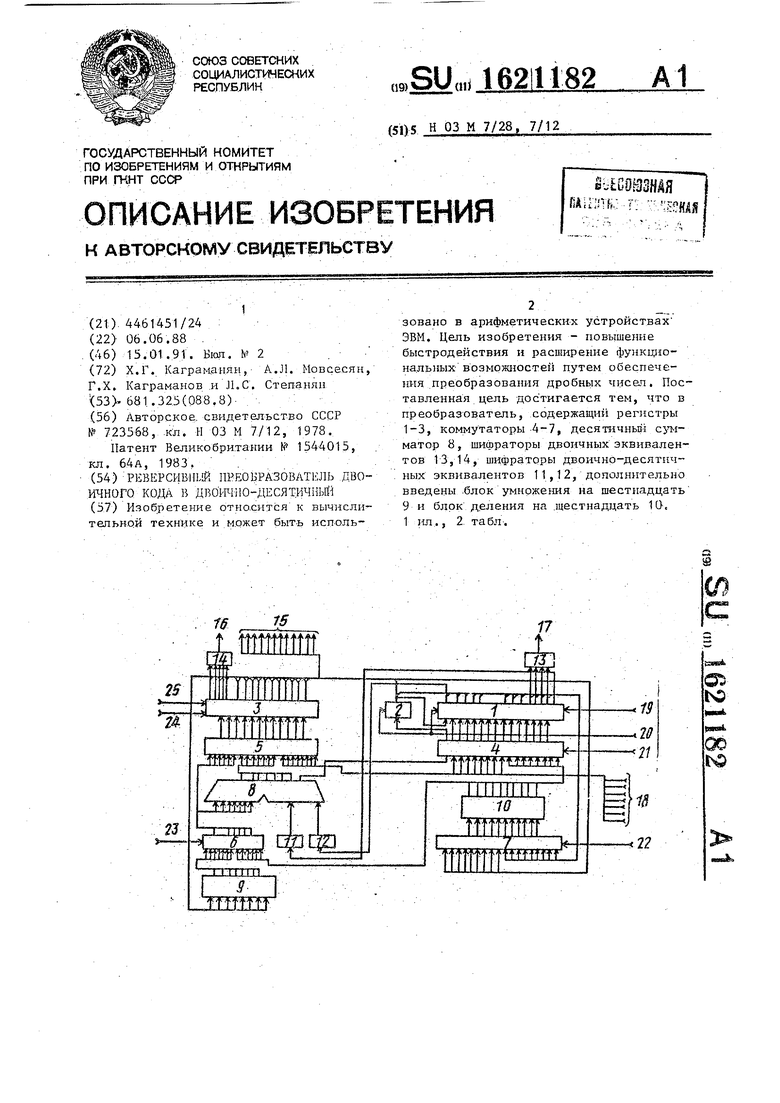

В качестве примера преобразования дробных двоичных чисел в десятичное возьмем число „9В28 „ Перед началом преобразования сбрасьшаются PI, P2 и РЗ и устанавливаются управляющие уровни на входах: , , , , ,и , После этого от группы входов 18 данных осуществляется прием информации в РЗ, Р2 и Р1,

20

Iтакт

Вых„РЗ(8.000)-уком,7. -% бл. 9(8/16) . вх.СМ8(.5) Вых.Р1 (биты n-З, п-2, п-1, п)шиф.11 - 11вх.СМ8 (2500) Вых.СМ8(2}5),(2,5) и сдвиг вправо Р2Р1

IIтакт

Вых.РЗ(2,500.„,).7 - бл. (2.5/16).6 - 1 вх.СМЗ (.15625) Вых.Р1 (биты п-3, п-29 п-1, п)шиф.11 - 11 вх.СМ8 (11.00000) Вых.СМЗ (11.15625) - ком,5 РЗ (11.15625) и сдвиг вправо Р2Р1

IIIтакт

Вых.РЗ (11.15625)..9 (1-1.15625/16) - ком.6

Вых.Р1 (биты n-З, п-2, п-1, п) .11 вх,СМ8 (9.00000000)

Вых.СМ8(9.697265625)- ком.5-РЗ (9.697265625) и сдвиг вправо Р2Р1

IVтакт

Вых.РЗ (9.697265625) ..9 (9.697265625/16)ком.6 .СМВ

. (.6060791015625) |

Вых„Р1 (биты n-З, п-2, п-1, п)шиф.1 1 - l lBX,CM8 (OiOOOOOOOOOOOOO) ВыХоСМЗ (.6060791015625) Р3(0.6060791015625) и сдвиг справо Р2Р1.

В итоге: 79В28,б ,6060791015625,...,16.

ВХ.СМ8 (6972

Фо-рмула изобретения

Реверсивный преобразователь двоичного кода в двоично-десятичный, содержащий первый, второй и третий регистры, первый и второй шифраторы двоичного эквивалента, первый и второй шифраторы десятичного эквивалента, с первого по четвертый коммутаторы и десятичный сумматор, группа входов первого операнда которого соединена с выходами третьего коммутатора и с первой группой входов второго коммутатора, выходы которого соединены с информационными входами третьего регистра, выходы которого соединены с первыми информационными входами четвертого коммутатора, а совместно с выходами второго регистра соединены с первой груп

при этом в битах 1-4 РЗ записывается последняя цифра 8, в регистре тетрад Р2 - цифра 9, а в Р1 за исключением последней тетрады - набор цифр В.28. После этого посредством двукратного возбуждения входа 20 правого сдвига обнуляется Р2, а в позиции младших трех тетрад оказывается набор двоичных цифр 9 В2.

20

000000)

ВХ.СМ8 (697265625)

40

5

0

пой выходов преобразователя, вторая группа выходов которого соединена с выходами второго шифратора двоичного эквивалента, входы которого соединены с выходами с первого по пятый разрядов третьего регистра, группа входов младших разрядов первого регистра соединена с группой младших разрядов пер- вого коммутатора, выходы старших че- . тырех разрядов которого соединены с информационными входами второго регистра, выходы которого соединены с информационными входами четырех старших разрядов первого регистра, а совместно с выходами первого регистра соединены с второй группой входов четвертого коммутатора, управляющий вход которого соединен с первым входом управления коммутацией преобразова13

теля, вход правого сдвига которого соединен с входами правых сдвигов второго и первого регистра, вход левого сдвига которого соединены с входом левого сдвига преобразователя, информационные входы которого соединены с первой группой входов первого коммутатора и второй группой входов второго коммутатора, третья группа входов которого соединена с разрядными выходами десятичного сумматора, входы младшей и старшей тетрады второго операнда которого соединены соответственно с выходами второго и первого шиф- раторов двоично-десятичных эквивалентов, входы которых соответственно соединены с выходами старшей и младшей тетрад первого регистра, выход пере162

полнения десятичного сумматора соеди- 20 второй группой входов первого коммунен с третьим входом первого коммутатора, управляющий вход которого соединен с входом разрешения передачи данных преобразователя, второй вход управления коммутацией которого соеди- 25 нен с управляющим входом третьего коммутатора, выходы первого регистра с

18214

второй по пятую тетрад соответственно соединены с входами первого шифратора двоичных эквивалентов, выходы ко- торого являются третьей группой выходов преобразователя, первый и второй входы управления передачей данных которого соответственно соединены с первым и вторым управляющими входами третьего регистра, отличающийся тем, что, с целью повышения быстродействия и расширения функциональных возможностей за счет обеспечения преобразования дробных чисел, в него введены блок умножения на шестнадцать и блок деления на шестнадцать, входы которого соединены с выходами четвертого коммутатора, а выходы блока деления на шестнадцать соединены с

0

татора и первой группой входов третьего коммутатора, вторая группа входов которого соединена с выходами блока умножения на шестнадцать, входы которого соединены с выходами третьего ре- .гистра.

| Преобразователь двоичной дроби в двоично-десятичную дробь | 1978 |

|

SU723568A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент Великобритании № 1544015, кл | |||

| Нефтяной конвертер | 1922 |

|

SU64A1 |

Авторы

Даты

1991-01-15—Публикация

1988-06-06—Подача