сятичным выходом каскада преобразования, информационный вход блока старш§ го каскада преобразования соединен с выходом регистра двоичного числа, каждый каскад преобразования дополнительно, содержит формирователь двоичного эквивалента.,. девять элементов ИЛИ, девять схем сравнения и дешифратор двоично-десятичного кода, выходы которого соединены с первыми входами соответствующих элементов ИЛИ, вторые входы которых соединены с выходами блока выделения старшей единицы, а выходы соединены со входами формирователя двоичного эквивалента, выход которого соединен с первым входом суммато- ра, второй вход которого соединен с первыми входами всех схем сравнения и с информационным входом каскада преобразования, выход сумматора является двоичным выходом касКс1да преобразования, управляющий вход которого соединен с управляющими вхоами формирователя двоичного эквивалента и блока выделения старшей диницы, информационные входы котоого соединены с выходами схем сравнения, вторые входы которых соединены с входом двоичных эквивалентов, вход дешифратора двоично-десятичного кода является десятичным входом каскада , преобразования.

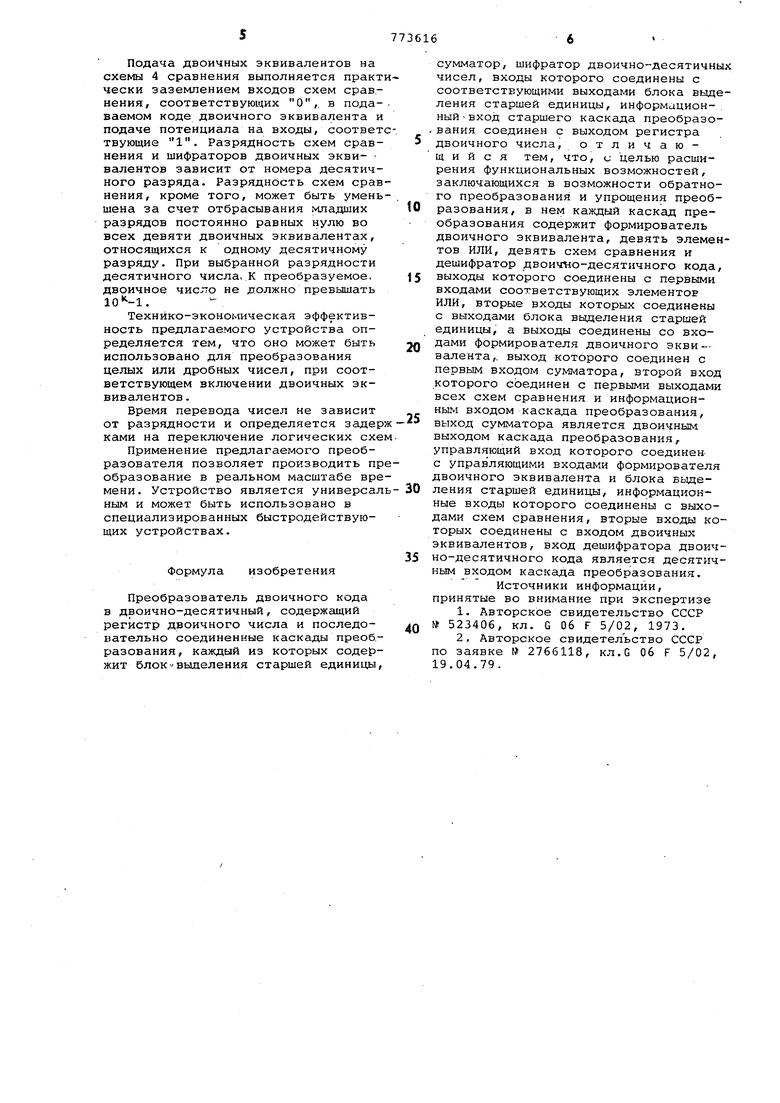

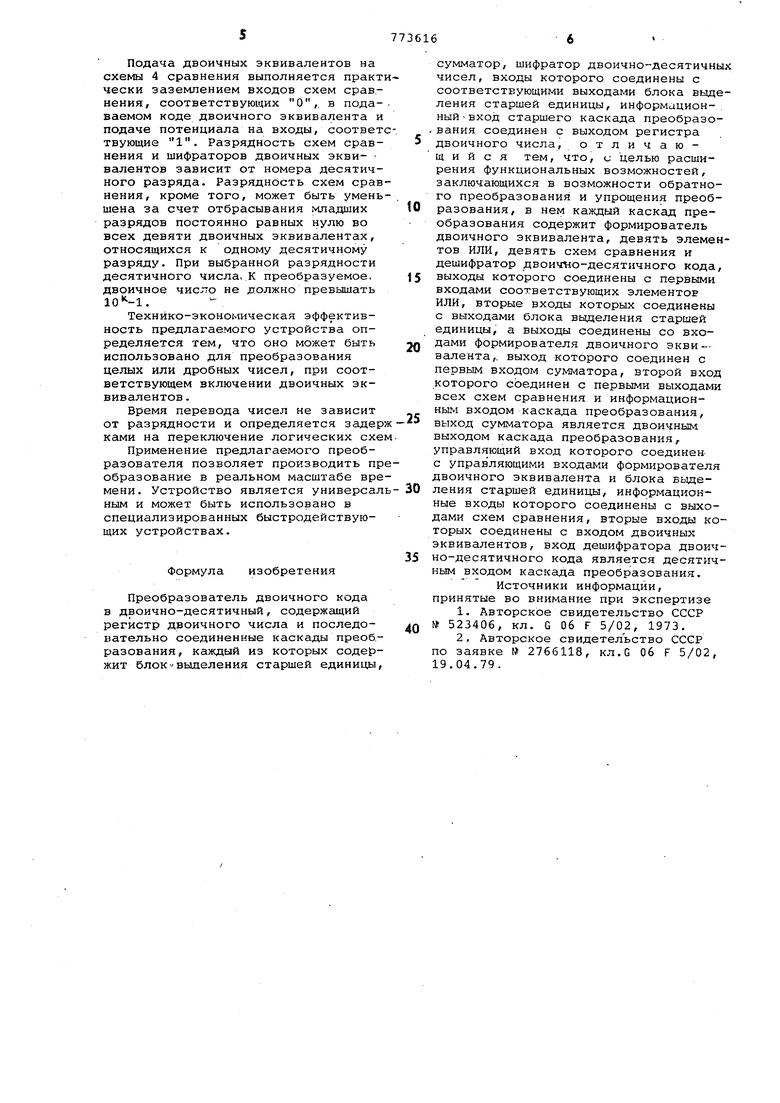

На чертеже представлена структурная схема реверсивного преобразователя двоичного кода в двоично-десятичный ,

Устройство содержит регистр 1 дно-. ичного числа, старший каскад 2 преобразования, предпоследний каскад 3 преобразования, схемы 4 сравнения, блок 5 выделения старшей единицы, сумматор 6, формирователь 7 двоичного эквивалента, шифратор 8 двоично-десятичных чисал, девять элементов ИЛИ 9, дешифратор 10 двоично-десятичного кода, вход 11 двоичных эквивалентов, десятичный выход 12 старшегЬ каскада преобразования, вход 13 старшего каскада преобразования, десятичный выход 14 предпоследнего каскада преобразования, вход 15 предпоследнего каскада преобразования, двоичный выход 16 каскада преобразования, управляющий вход 17,-вход 18-двоичного числа, вход 19 младшего каскада преобразования.

Предлагаемый преобразователь .работает следующим образом.

В режиме прямого преобразования двоичный код преобразуемого числа через вход 18 заносится в регистр 1. На управляющий вход 17 подается 1, что соответствует прямому преобразованию. С выхода регистра 1 параллельным кодом число А подается на вход сумматора 6 и на все первые входы девяти схем 4 сравнения, относящихся к старшему каскаду 2 преобразования.

На вторые входы 11 схем 4 сравнение подается девять двоичных эквивалентов десятичных чисел вида: В Ц-ю где ,2, . . . ,9; К - 0,1,2...-номер разряда десятичного числа.

С помощью схем 4 .сравнения определяются те двоичные эквивалекты, для которых справедливо неравенство . Схемы сравнения, для которых удовлетворяется это условие, вырабатывают на выходе сигналыj поступающие на блок 5 выделения старшей единицы. Сигнал с выхода блока 5 поступает через первый вход соответствующего элемента ИЛИ 9 (на другие входы элементов ИЛИ подан О в режиме прямого преобразования) на формирователь 7 двоичного эквивалента. Восстановленный соответствующий двоичный эквивалент десятичного числа в дополнительном коде подается на вход сумматора 6 и вычитается из преобразуемого двоичного числа. Кроме того, сигнал с выхода блока 5 поступает на двоично-десятичный код шифратора 8, на выходе 12 которого формируется двоично-десятичный код старшей десятичной цифры, По.лученный остаток разности с выхода сумматора 6 поступает на первый вход сумматора и девять схем сравнения следующего десятичного разряда. Процесс формирова.1ия остатков и двоично-десятичных кодов в следующих десятичных разрядах происходит аналогично. Младшая двоичнодесятичная цифра получается непоср дственно на выводах 16 четырех младших разрядов сумматора 6 предпоследн 1го каскадаЗ преобразования,

В режиме обратного преобразования двоично-десятичный код подается на дешифратор 10 двоично-десятичного кода. Старший разряд подается через вход 13, а младший - через вход 19 на четыре младших разряда регистра 1, На управляющий вход 17 подается О, который запрещает работу блока 5, в результате чего erg) выходы принимают нулевое значение и приводит шифратор 7 двоичных эквивалентов в режим формирования двоичных уэквивалентов в прямом коде.

Младший разряд преобразуемого десятичного числа подается на первый вход сумматора 6 и складывается с двоичным эквивалентом старшего десятичного разряда, который соответствует поданному двоично-десятичному коду,. Полученная схема с выхода сумматора 6 подается на первый вход су Шагора следующего каскада преобразования. Далее процесс формирования двоичного числа происходит аналогично. Результат преобразования снимается с выхода 16 сумматора 6 предпоследнего каскада преобразования. Подача двоичных эквивалентов на схемы 4 сравнения выполняется практ чески заземлением входов схем сравнения, соответствующих О,, в подаваемом коде двоичного эквивалента и подаче потенциала на входы, соответ твующие 1. Разрядность схем сравнения и шифраторов двоичных экви- валентов зависит от номера десятичного разряда. Разрядность схем срав нения, кроме того, может быть умень шена за счет отбрасывания младших разрядов постоянно равных нулю во всех девяти двоичных эквивалентах, относящихся к одному десятичному разряду. При выбранной разрядности десятичного числа, К преобразуемое, двоичное число не должно превышать 10 -1. Технико-экономическая эффективность предлагаемого устройства определяется тем, что оно может быть использовано для преобразования целых или дробных чисел, при соответствующем включении двоичных эквивалентов . Время перевода чисел не зависит от разрядности и определяется заде нами на переключение логических сх Применение предлагаемого преобразователя позволяет производить п образование в реальном масштабе вр мени. Устройство является универса ным и может быть использовано в специализированных быстродействующих устройствах. Формула изобретения Преобразователь двоичного кода в двоично-десятичный, содержащий регистр двоичного числа и последовательно соединенные каскады преоб разования, каждый из которых содер жит блок-выделения старшей единицы сумматор, шифратор двоично-десятичных чисел, входы которого соединены с соответствующими выходами блока выделения старшей единицы, информационный -вход старшего каскада преобразования соединен с выходом регистра двоичного числа, отличающ и и с я тем, что, с целью расширения функциональных возможностей, заключающихся в возможности обратного преобразования и упрощения преобразования, в нем каждый каскад преобразования содержит формирователь двоичного эквивалента, девять элементов ИЛИ, девять схем сравнения и дешифратор двоично-десятичного кода, выходы которого соединены с первыми входами соответствующих элементов ИЛИ, вторые входы которых соединены с выходами блока выделения старшей единицы, а выходы соединены со входами формирователя двоичного эквивалента,, выход которого соединен с первым входом сумматора, второй вход которого соединен с первыми выходами всех схем сравнения и информационны.м входом каскада преобразования, выход сумматора является двоичным выходом каскада преобразования, управляющий вход которого соединенс управляющими входами формирователя двоичного эквивалента и блока вьщеления старшей единицы, информационные входы которого соединены с выходами схем сравнения, вторые входы которых соединены с входом двоичных эквивалентов, вход дешифратора двоично-десятичного кода является десятичным входом каскада преобразования. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 523406, кл. G Об F 5/02, 1973. 2,Авторское свидетельство СССР по заявке № 2766118, кл.С Об F 5/02, 19.04.79.

fi

17

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный преобразовательдВОичНОгО КОдА B дВОичНО-дЕСяТичНый | 1979 |

|

SU849198A1 |

| Преобразователь двоичного кодаВ дЕСяТичНый | 1979 |

|

SU830371A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| Устройство для преобразования двоично-десятичного кода в двоичный код и обратно | 1990 |

|

SU1755375A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1982 |

|

SU1097995A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Устройство для преобразования последовательного десятичного кода в последовательный двоичный код | 1974 |

|

SU636606A2 |

Авторы

Даты

1980-10-23—Публикация

1979-04-27—Подача