Изобретение относится к технике связи. Известно устройство для преобразования двоичного сигнала в модулированный псёвдопятеричный сигнал, содержащее последовательно соединен ные входной сумматор по модулю два, первый сдвигающий регистр, выход ко торого подключен к первому входу первого элемента И и через первый элемент НЕ к первому входу второго элемента И, второй сдвигающий регистр, выход которого подключен к рдному из входов третьего эл ш«1ента И и второго элемента НЕ и через последовательно соединенные входной сумматор по модулю два и третий эле мент НЕ к первому входу четвертого элемента И, последовательно соедине ные четвертый элемент НЕ и пятый элемент И, а также выходной суммато причем на управляющий вход шестого элемента И и четвертого элемента НЕ подан прямоугольный сигшал несущей частоты l . Однако в известном устройстве остаточные напряжения влияют на формирование выходного сигнала. . Цель изобретения - снижение алия- НИН остаточных напряжений на формирование выходного сигнала. Для этого в устройство для преобразования двоичного сигнала в модулированный псевдопятеричный сигнал, содержащее последовательно соединенные входной сумматор по модулю два, первый сдвигающий регистр, выход которого подключен к первому входу первого элемента И и через первый элемент НЕ к первому входу второго элемента И, и второй сдвигающий регистр, выход которого подключен к од7 ному из входов третьего элемента И и второго элемента НЕ и через последовательно соединенные входной сумматор по модулю два и третий элемент НЕ к первому входу четвертого элемента И, последовательно соединенные четвертый элемент НЕ и пятый элемент И, а также выходной сумматор, причем на управляющий вход шестого элемента И и четвертого элемента НЕ подан прямоугольный сигнал несущей частоты, введены- дополнительный элемент НЕ и элемент ИЛИ-НЕ, при этом информационный вход входного сумматора по модулю два подключен к входу дополнительного злемента НЕ и ко второму входу первого и второго элементов И, к третьему входу которых подключены соответственно вход и выход четвертого элемента НЕ, а выходы первого и второго элементов И подключены к соответствующим входам выходного сумматора. Между выходами входного сумматора по модулю два и первого элемента НЕ включен третий элемент И, выход которого подключен к входу пятого элемента И и к одному из входов элемента ИЛИ-НЕ. Между выходами первого сдвигающего регистра и второго эл мента НЕ включен четвертый элемент И, выход которого подключен к входу шестого элемента И и к другому входу элемента ИЛИ-НЕ, причем выходы пятого и шестого элементов И, выход дополнительного элемента НЕ и выход элемента ИЛИ-НЕ подключены к соответствующим входам выходного сумматора.

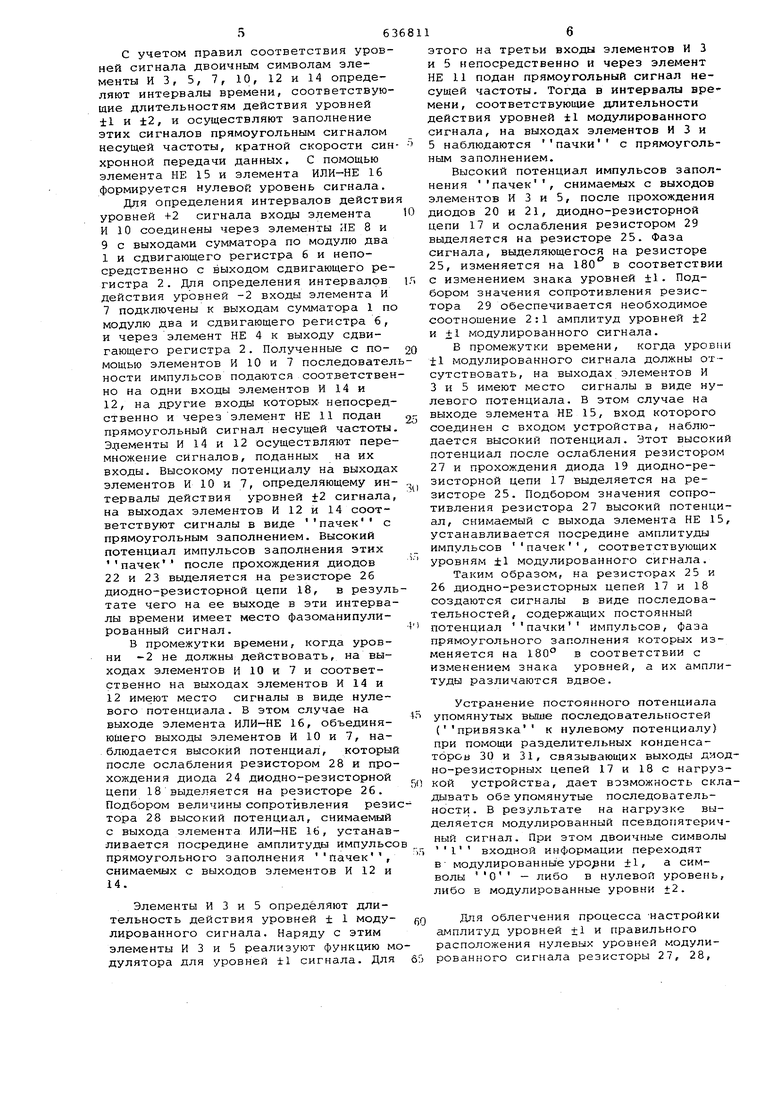

На чертеже приведена функциональная схема устройства.

Устройство для преобразования двоичного сигнала в модулированный псевдопятеричный сигнал содержит: последовательно соединенные входной сумматор 1 по модулю два, первый сдвигающий регистр 2, выход которого подключен к первому входу первого элемента И 3 и через первый элемент НЕ 4 к первому входу второго элемент И 5; второй сдвигающий регистр 6, выход которого подключен к одному из входов третьего элемента И 7 и второго элемента НЕ 8 и через последовательно сое диненные входной сумматор 1 по модулю два и третий элемент НЕ 9 к первому входу четвертого элемента И 10; последовательно соединенные четвертый элемент НЕ 11 и пятый элемент И 12, а также выходной сумматор 13, шестой элемент И 14, дополнительный элемент НЕ 15 и элемент ИЛИ-НЕ 16 Информационный вход входного суммтора 1 по модулю два подключен к входу дополнительного элемента НЕ 15 и ко второму входу первого и второго элементов И 3 и 5, к третьему входу которых подключены соответственно вход и выход четвертого элемента НЕ 11, а выходы первого и второго элементов И 3 и 5 подключены к соответствующим входам выходного сумматора 13. Между выходами входного сумматора 1 по модулю два и первого элемента НЕ 4 включен третий элемент И 7, выход которого подключен к входу пятого элемента И 12 и к одному из входов элемента ИЛИ-НЕ 16, а между выходами первого сдвигающего регистра 2 и второго элемента НЕ 8 включен четвертый элемент И 10, выход которого подключен к входу щестого элемента И 14 и к другому входу элемента

ИЛИ-НЕ 16. При ЭТОМ выходы пятого и шестого элементов И 12 и 14, выход дополнительного элемента НЕ 15 и выход элемента ИЛИ-НЕ 16 подключены к соответствующим входам выходного сумматора 13. На управляющий вход шестого элемента и 14 и четвертого элемента НЕ 11 подан прямоугольный сигнал несущей частоты.

Выходной сумматор 13 содержит две диодно-резисторные цепи 17 и 18, состоящие из диодов 19, 20, 21 и 22, 23, 24 и резисторов 25 и 26, резисторы 27, 28, 29 и разделительные конденсаторы 30, 31.

Устройство работает следующим образом. Исходная информация в виде двоичной последовательности однополярных импульсов поступает от источника двоичного сигнала на вход сумматора 1 по модулю два, где она складывается с последовательно задержанной относительно входной на требуемое число тактов сдвигающими регистрами 2 и 6 на одинаковое число тактов задержки.

Устройство осуществляет псевдопятеричное кодирование (нестатическое преобразование) входной информации и модуляцию при помощи прямоугольного сигнала несущей частоты, причем функции псевдопятеричного кодопреобразователя и модулятора в нем совмещены. На выходе устройства образуется модулированный сигнал с пятью уровнями.

С учетом правила псевдопятеричного кодирования, гласящего: сигнал с выхода сумматора 1 по модулю два и с выхода сдвигающего регистра 6 умножается на -1, а сигнал с выхода сдвигающего регистра 2 умножается на +2,заданный уровень модулированного сигнала имеет место при определенном совпадении двоичных символов в соответствующих точках устройства. Необходимое соотношение символов заданному уровню приведено в таблице. С учетом правил соответствия уровней сигнала двоичным символам элементы И 3, 5, 1, 10, 12 и 14 определяют интервалы времени, соответствующие длительностям действия уровней ±1 и ±2, и осуществляют заполнение этих сигналов прямоугольным сигналом несущей частоты, кратной скорости сии кронной передачи данных, С помощью элемента НЕ 15 и элемента ИЛИ-НЕ 16 формируется нулевой уровень сигнала. Для определения интервалов действи уровней +2 сигнала входы элемента И 10 соединены через элементы ЛЕ 8 и 9 с выходами сумматора по модулю два 1 и сдвигающего регистра 6 и непосредственно с выходом сдвигающего регистра 2. Для определения интервалов действия уровней -2 входы элемента И 7 подключены к выходам сумматора 1 п модулю два и сдвигающего регистра б, и через элемент НЕ 4 к выходу сдвигающего регистра 2. Полученные с помощью элементов И 10 и 7 последовател ности импульсов подаются соответствен но на одни входы элементов И 14 и 12, на другие входы которых непосредственно и черезэлемент НЕ 11 подан прямоугольный сигнал несущей частоты Э: ементы И 14 и 12 осуществляют пере множение сигналов, поданных на их входы. Высокому потенциалу на выходах элементов И 10 и 7, определяющему интервалы действия уровней ±2 сигнала на выходах элементов И 12 и 14 соответствуют сигналы в виде пачек с прямоугольным заполнением. Высокий потенциал импульсов заполнения этих пачек после прохождения диодов 22 и 23 выделяется на резисторе 26 диодно-резисторной цепи 18, в резул тате чего на ее выходе в эти интерва лы времени имеет место фазоманипулированный сигнал. В промежутки времени, когда уровни -2 не должны действовать, на выходах элементов и 10 и 7 и соответственно на выходах элементов И 14 и 12 имеют место сигналы в виде нулевого потенциала. В этом случае на выходе Элемента ИЛИ-НЕ 16, объединяющего выходы элементов И 10 и 7, наблюдается высокий потенциал, который после ослабления резистором 28 и прохождения диода 24 диодво-резисторной цепи 18 выделяется на резисторе 26. Подбором величины сопротивления рези тора 28 высокий потенциал, снимаемый с выхода элемента ИЛИ-НЕ 1ъ, устанавливается посредине амплитудда импульсо прямоугольного заполнения пачек. снимаемых с выходов элементов И 12 и 14. Элементы и 3 и 5 определяют длительность действия уровней ± 1 модулированного сигнала. Наряду с этим элементы И 3 и 5 реализуют функцию м дулятора для уровней ±1 сигнала. Для 6 1б этого на третьи входы элементов И 3 и 5 непосредственно и через элемент НЕ 11 подан прямоугольный сигнал несущей частоты. Тогда в интервалы времени, соответствующие длительности действия уровней ±1 модулированного сигнала, на выходах элег ентов И 3 и 5 наблюдаются пачки с прямоугольным заполнением. Высокий потенциал импульсов заполнения пачек, снимаемых с выходов элементов И 3 и 5, после прохождения диодов 20 и 21, диодно-резисторной цепи 17 и ослабления резистором 29 выделяется на резисторе 25. Фаза сигнала, выделяющегося на резисторе 25, изменяется на 180 в соответствии с изменением знака уровней ±1. Подбором значения сопротивления резистора 29 обеспечивается необходимое соотношение 2:1 амплитуд уровней +2 и +1 модулированного сигнала. В промежутки времени, когда уроваи ±1 модулированного сигнала должны отсутствовать, на выходах элементов И 3 и 5 имеют место сигналы в виде нулевого потенциала. В этом случае на выходе элемента НЕ 15, вход которого соединен с входом устройства, наблюдается высокий потенциал. Этот высокий потенциал после ослабления резистором 27 и прохождения диода 19 диодно-резисторной цепи 17 выделяется на резисторе 25. Подбором значения сопротивления резистора 27 высокий потенциал, снимаемый с выхода элемента НЕ 15, устанавливается посредине амплитуды импульсов пачек, соответствующих уровням ±1 модулированного сигнала. Таким образом, на резисторах 25 и 26 диодно-резисторных цепей 17 и 18 создаются сигналы в виде последовательностей, содержащих постоянный потенциал пачки Импульсов, фаза прямоугольного заполнения которых изменяется на 180° в соответствии с изменением знака уровней, а их амплитуды различаются вдвое. Устранение постоянного потенциала упомянутых выше последовательностей (привязка к нулевому потенциалу} при помощи разделительных конденсаторов 30 и 31, связывающих выходы диодно-резисторных цепей 17 и 18 с нагрузкой устройства, дает возможность складывать обэ упомянутые последовательности . В результате на нагрузке выделяется модулированный псевдопятеричный сигнал. При этом двоичные символы 1 входной информации переходят Б- модулированные уровни ±1, а символы О - либо в нулевой уровень, либо в модулированные уровни ±2. Для облегчения процесса -настройки амплитуд уровней +1 и правильного расположения нулевых уровней модулированного сигнала резисторы 27, 28, 29 могут быть выполнены в виде потен4MOh4teTpoa. В устройстве устраняется влияние остаточных напряжений на выходе элементов ИЗ, 5, 12, 14, элвмента-НЕ 15 и элемента ИЛИ-НЕ 16, на формирование спектра модулированного сигнала, так как открыт только один из входных диодов в кгьждой из диодно-резисторных цепей 17 и 18. Формула иэовретения Устройство для преобразования дволчного сигнала в модулированный псвадопятеричный сигнал, содержавшее последовательно соединенные 1входной сум матор по модулю два, первый сдвигаюьдай регистр, выход ifоторого подключен к первсшу входу первого элемента И и через первый элемент НЕ к первому яко ду второго элемента И, и второй сдвигающий регистр, выход которого подключен к одному из входов третьего элемента И и второго элемента ИВ и че рез последовательно ейедиаенные яходной сумматор по модулю два и третий элемент НЕ к первому входу четвертого элемента И, последовательно соеданенные четвертый элемент НЕ и пятый элемейт К, а также выходной сумматор причем на управляющий вход шестого элемента И и четвертого элемента НЕ подан прямоугольный сигнал несущей частоты, о т л и ч а ю щ с я тем, что, с целью снижения влияния оста точных напряжений на формирование выходного сигнала, введены дополнительный элемент НЕ и элемент ИЛИ-НЕ, при этом информационный вход входного сумматора по модулю два подключен к входу дополнительного элемента НЕ и к второму входу первого и второго элементов И, к третьему входу которых подключены соответственно вход и выход четвертого элемента НЕ, а выходы первого и второго элементов И подключены к соответствующим входам выходного сумматора, между выходами входного сумматора по модулю два и первого элемента НЕ включен третий элемент И, выход которого подключен к входу пятого элемента Лик одному из ВХОДОВ элемента ИЛИ-НЕ, а между выходами первого сдвигающего регистра и второго элемента НЕ включен четвертый элемент И, выход которого подключен к входу шестого элемента и и к iBpyroMjf входу элемента ИЛИ-НЕ, причем выходы пятого и шестого элементов И, выход дополнительного элемеяча НЕ и выход; элемента ИЛИ-НЕ подключен к соответствующим. входам выходного cy AiaTOpa. ; , Источники информации, принятые во внимание при Экспертизе: 1. Boder Р. Ein Ddtenmoaem fur f4do trit /s mffc Einseitentjandmodueation. Dalenubertra gung Vcwrtrajre der Fac-htagon Dotenobertfagwi f n Mcmnfeeim xom 49,Ы5 2-f, Marz i969. Но1сНг« Лвп1.ес п1бсЪе Facht)eHthte,Bcind 57, 19fe9,Veft)ancl Beutsciier EtectrotecliMlfer.vOE-Verta CMBH,Bertin,i969,&224-25O.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство преобразования двоичного сигнала в модулированный псевдо-пятеричный сигнал | 1975 |

|

SU598259A1 |

| Устройство для преобразования двоичного сигнала в модулированный псевдо-троичный сигнал | 1975 |

|

SU581590A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| АВТОКОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ ПСЕВДОСЛУЧАЙНОГО ФАЗОМАНИПУЛИРОВАННОГО СИГНАЛА | 1991 |

|

RU2013005C1 |

| Инфранизкочастотный программный генератор | 1980 |

|

SU919055A1 |

| Цифровой фильтр | 1976 |

|

SU643888A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННОГО СИГНАЛА | 1996 |

|

RU2110145C1 |

| Устройство для формирования биимпульсного сигнала | 1985 |

|

SU1282345A1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАНИЯ ЧАСТОТЫ | 2016 |

|

RU2644070C1 |

Авторы

Даты

1978-12-05—Публикация

1976-01-27—Подача