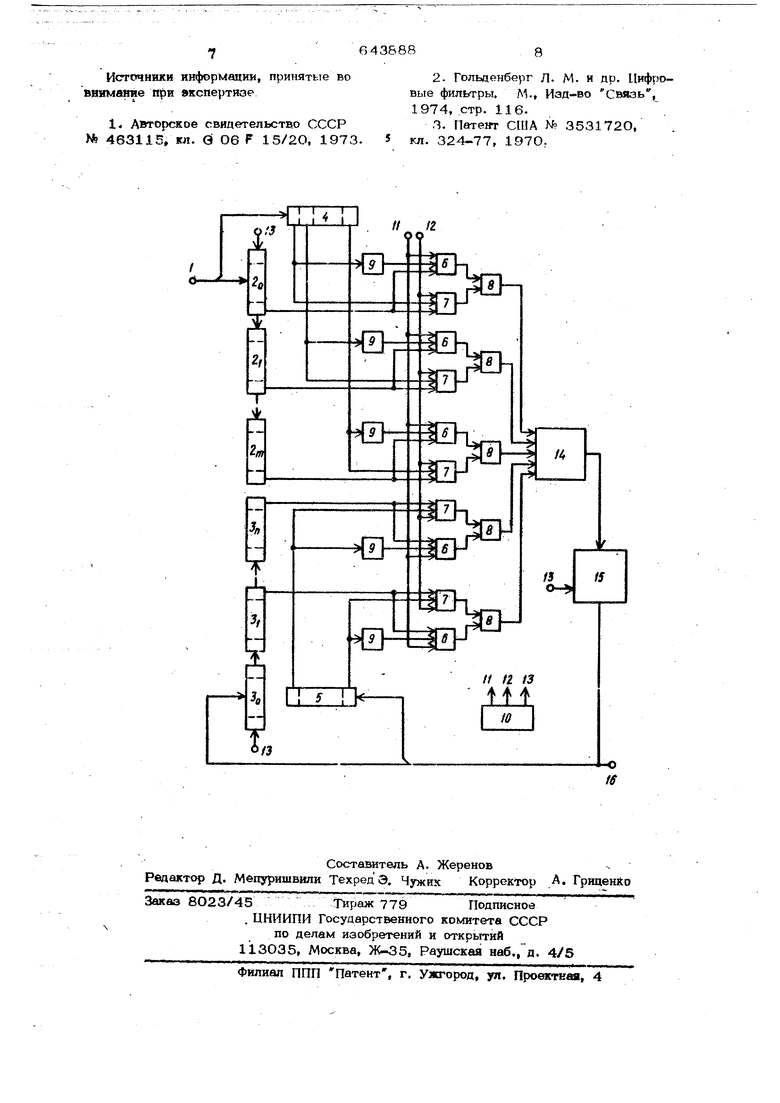

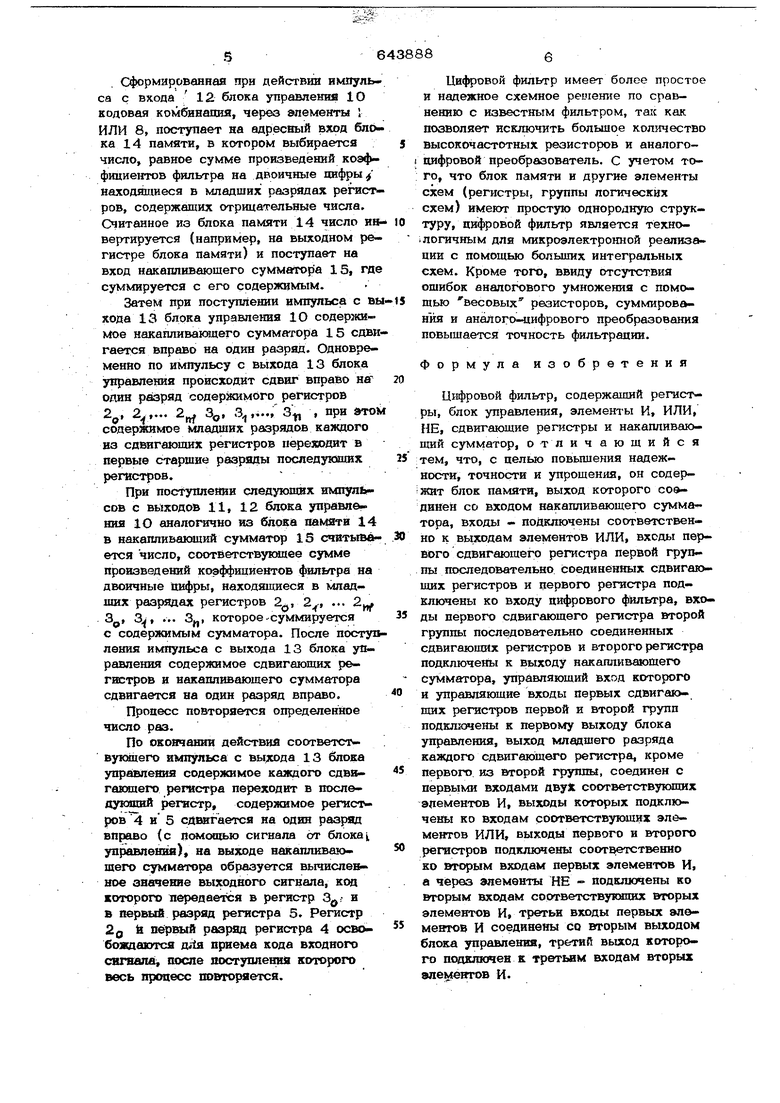

(54) ЦИФРОВОЙ ФИЛЬТР элемевтов ИЛИ, входы первого сдвигающего регистра первой группы после- дователыго соединенных сдвигающих регистров и первого регистра подкпкзчены ко входу цифрового филыгра, входы пер:вого сдвигающего регистра второй группы последовм-ельно соединенных сдвигающих регистров и второго penicrpa подключены к выходу накапливающего сумматора, управляющий вхсд которого и управляющие входы первых сдвигающих регистров первой и втророй групп пошслкяены к первому выходу блока удравлевиа, выход младшего разряда каж дого сдвигакмаего регистра, кроме первого иа второй группы, соединен с первыми входами двух соответствующих элементов И, выходы которых подключены ко входам соответствующих элементов ИЛИ, выходы Первого и второго регистров подключены соответственно ко вторым входам первых элементов И, а через элементы НЕ - подключены ко вт рым входам соответствующих вторых элементов И, третьи входы первых элемет-ов И соединены со вторым выходом блока управления, третий выход которог подключен к третьим входам вторых эле ментов И. На чертеже представлена схема кифрового филнгра, на которой приняты-сле дующие, обозначения: вход 1 фильтра, регистры 2р, 2j, сдвигающие 3„ , регист1 зь1 4,5 fi tM f 3л, 3, m О И 6, 7, элементы ИЛИ 8, элементы элементы НЕ 9, блок 10 управлений, выходы 11, 12, 13 блока управления, блок 14 памяти, накапливающий сумматор 15, выход 16 фильтра. Вход фильтра 1 связан с цепочкой пбсЛёдс вательн6 соединейньтх сдЕйгаюаш регистров 2р, 2,, ,..., 2 первой груп в которых хранятся L гвоичные коды зна .ченнй входной последователйьностя, и с входом регистра 4, хранящего соответ с №шё знаковые разряды кодов вяЬдной последовательности. Последовательн соединенные регистры второй группы (регистры обратной связи) SQ, 3, . . 3 J, служат для хранения двоичных J кодов значений выходной последьаатель кости, а регистр 5 дпа зф&ненва их знаковых разрядов. Используемый в схеме ш«|даового || льтра блок пама-га представляет собой шхггойнное запоминающее устройство (например, резисторное или диодное), в котором хранятся суммы произведений коэффшиентов фильтра на двоичные цифры для всех BosMojiraHX наборов цифр. При поступлении импульса с выхода 11 блока управления на выходах элементов И 6 образуется кодовая комбинация. Потенциал 1 появляется на выходах тех элементов И 6, на входах которых происходит совпадение единичного .по тенциала младшего разряда импульса с выхода 11 блока управления 10 и -швертированного кода знака, равного О для положительных чисел. Потенциал О появляется на выходах всех элементов И 6 за счет действия потенциала О в младшем разряде числа или в соответствующем разряде регистров 4 или 5. Импульс с выхода 12 блока управления в момент действия с выхода 11 отсутствует, что обеспечивает потенциал О на всех элементах И 7. Образованная таким образом на выходах элементов И кодовая ком6инй1ШЯ1 через элементы ИЛИ 8 поступает на адресный вход блшса 14 памяти. По выбранному адресу считывается число, равное сумме произведений коэффициент тов 4ншьтра на соответствующие двовч ные цифрыкодовой комбинации, поступивдгей на адресный вход. Считываемое из блока памяти число представляет со- , бой часть суммы,равной сумме проиаве деШЕй коэффициентрв фильтра на младшие двоичные цифры положительных кодов, з аковЫй разряд которых имеет потенциал О, При П1е)стуш1енви вмпульса с выхода 12 блока управления 10 кодовая комбинация образуется аа выходах элементов И 7. В получаемой кодовой комбинашш I стоят на местах соответствуюншх значащему младшему разряду кодов от- рипательных чисел. Это обеспечивается совпадением на входах элементов И 7 значащей младп1его разряда, импульса с выхода 12 блока управления и кода знака числа.О в кодовой комбинащт появляется при наличии О в младшем разряде числа шш при наличия О в соответствужицих разрядах знаковых регистров 4 и 5. Нулевой потешшал на выхода:; 9Лвментов И 6. об зпечввается отсутствием импульса с выхода 11 блока управления 10 в момент действия импульса с выхода 12.

Сформированная при действии импульса с входа 12 блока управления Ю кодовая комбинашш, через элементы 1 ИЛИ 8, поступает на адресный вход блока 14 памяти, в котором выбирается число, равное сумме произведений коэффициентов фильтра на двоичные цифры/ находящиеся в младших разрядах регистров, содержащих отрицательные числа. Считанное из блока памяти 14 число ин вертируется (например, на выходном регистре блока памяти) и поступает на вход накапливающего сумматора 15, где суммируется с его содержимым.

Затем при поступлении импульса с вы хода 13 блока управления 10 содерзки- мое накапливающего сумматора 15 сдвигается вправо на один разряд. Одновременно по импульсу с выхода 13 блока управления происходит сдвиг вправо на один разряд содержимого регистров 2. 2,... 2 Зд, 3 ,.., 3 , при этом содержимое младших разрядов каждого из сдвигающих регистров переходит в первые старшие разряды последуквдих регистров.

При постгуплейви следующих нмпулЬсов с выходов 11, 12 блока управлвг ния Ю аналогично из блока памяти 14 в накаплиьакиций сумматор 15 счйтывается число, соответствующее сумме произведений коэффициентов фил1Угра на двоичные цифры, находящиеся в младших разрядах регистров 2, 2, ... 2 В, 3, ... 3j,, которое-суммируется

с содержимым сумматора. После поступления импульса с выхода 13 блока управления содержимое сдвигающих регистров и накапливающего сумматора сдвигается на один разряд вправо.

Процесс повторяется определенное число раз.

По окончании действия соответствующего импульса с выхода 13 блока управлеюш содержимое каждого едва гаювдего регистра переходит в последующий peracrpt содержимое регистров 4 и 5 слагается на один разряд вправо (с псялощью сигнала от блока управлення), на выходе накапливаюшего сумматора образуется вычислев ное значение выходного сигнала, код которого передается в регистр и в первый разряд регистра 5. Регистр 2 о и первый разряд регистра 4 освобождаются дЛя приема кода входного скгввла, после лоступлевня которого весь процесс повторяется.

Цифровой фильтр имеет более просто И надежное схемное решение по сравнению с известным фильтром, Taic как позволяет исключить большое количеств высокочастотных резисторов и аналогоJ цифровой преобразователь. С учетом того, что блок памяти и другие элементы схем (регистры, группы логических схем) имеют простую однородную структуру, цифровой фильтр является тёхноi логичным для микроэлектронной реализацин с помощью болы1шх интегральных схем. Кроме того, ввиду отсутствия ощибок аналогового умножения с помощью весовых резисторов, суммирования и аналого-цифрового преобразования повышается точность фильтрации.

формула изобретения

Цифровой фильтр, содержащий регистры, блок управления, элементы И, ИЛИ, НЕ, сдвигающие регистры и накапливающий сумматор, отлич ающи йс я тем, что, с целью повьпиения надежности, точности и упрощения, он содер жит блок памяти, выход которого соединен со входом накапливающего сумматора, входы - подключены соответственно к выходам элементов ИЛИ, входы первого сдвигающего регистра первой группы последовательно Соединенных сдвигающих регистров и первого регистра подключены ко входу цифрового фйлкгра, входы первого сдвигающего регистра второй группы последователыю соединенных сдвигающих регистров и второго регистра подключены к выходу накапливающего сумматора, управляющий вхпд которого и управляющие входы первых сдвигающих регистров первой и второй групп подключены к первому выходу блока управления, выход младшего разряда каждого сдвигающего регистра, кроме первого КЗ второй группы, соединен с первыми входами дву соответствующих элементов И, выходы которых подключены ко входам соответствующих элементов ИЛИ, выходы первого и второго регистров подключены соответственно ко вторым входам первых элементов И, а через элементы НЕ - подключены ко вторым входам соответствукшгах вторых элементов И, третьи входы первых элементов И соединены со вторым выходом блока управления, третий выход которого подключен к третьим входам вторых элементов И. Источники информании, принятые во внимаяне при вкспертиое 1, Авторское свидетельство СССР № 463115, кл. Q Об F 15/2О, 1973. 5 2.Гольденберг Л. М. и др. Цифровые фильтры. M.f Иад-во Связь, 1974, стр. 116. 3.Патент США № 353172О, кл. 324-77, 197О.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь | 1987 |

|

SU1538254A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Устройство для вычисления гиперболических функций | 1977 |

|

SU732888A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Программно-управляемый цифровой фильтр | 1987 |

|

SU1513475A1 |

| Устройство для отображения информации | 1986 |

|

SU1319072A1 |

| Цифровое устройство для преобразования координат | 1981 |

|

SU960808A1 |

| Цифровой знаковый коррелометр | 1980 |

|

SU962975A1 |

| Генератор широкополосных случайных процессов | 1980 |

|

SU881743A1 |

Авторы

Даты

1979-01-25—Публикация

1976-10-25—Подача