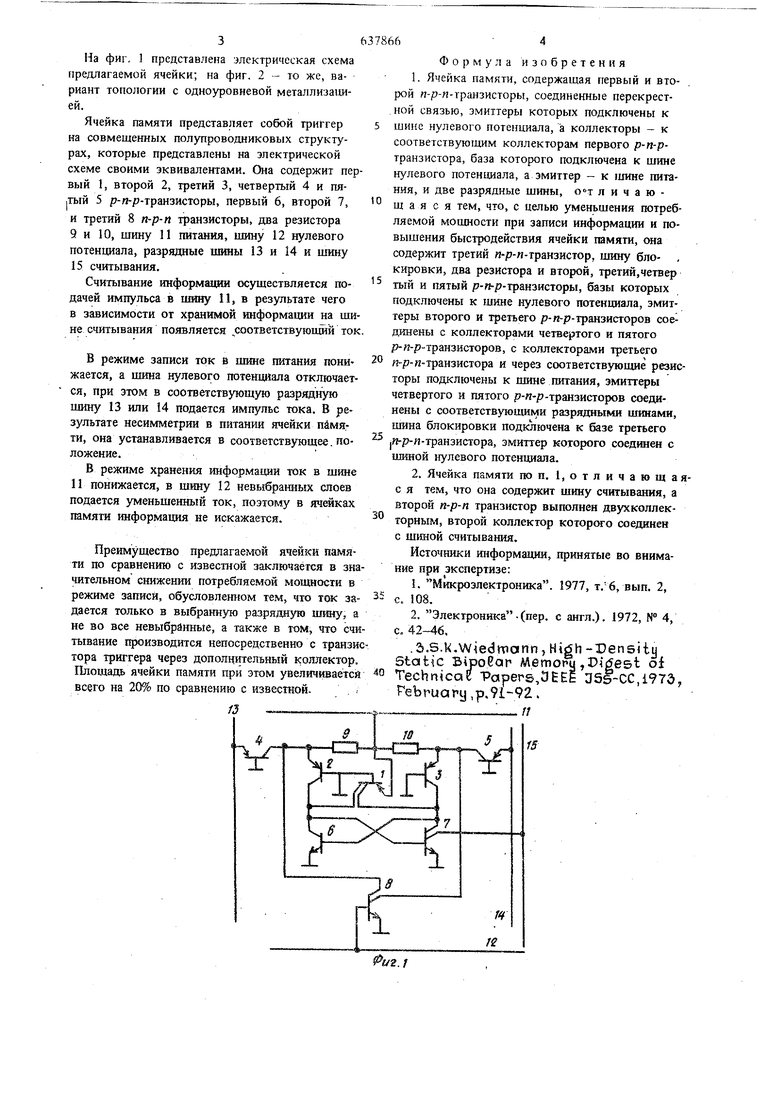

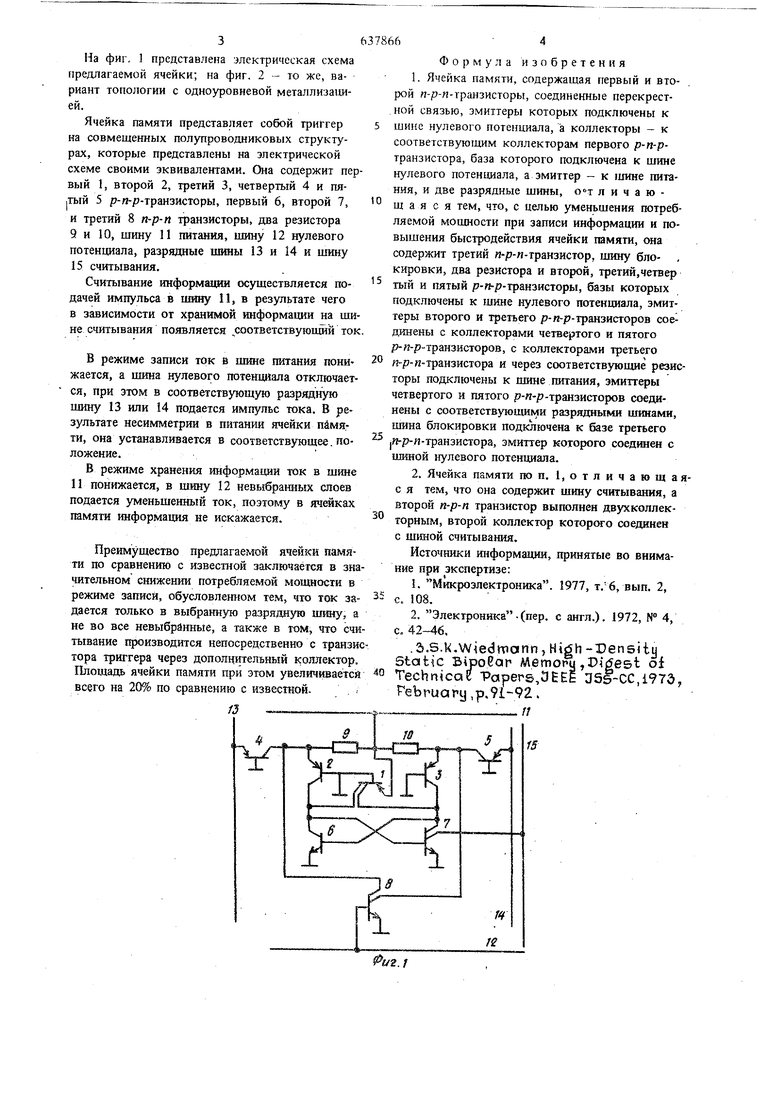

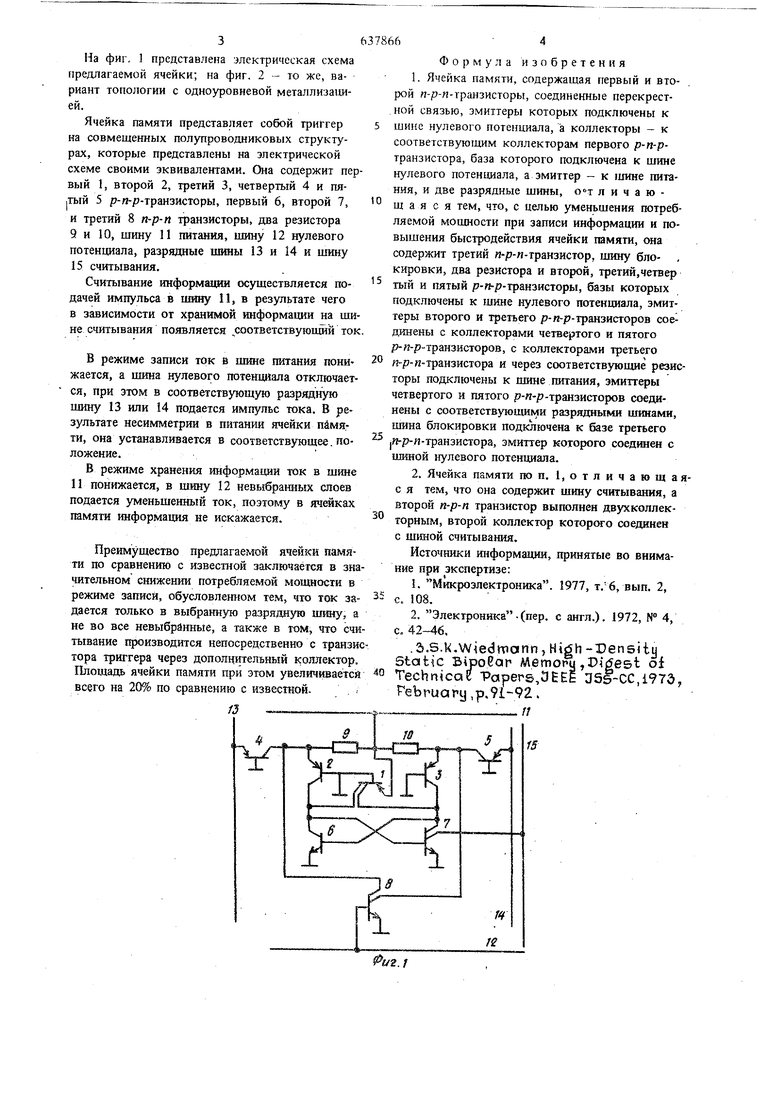

Изобретение относится к вычислительной .технике, в частности к полупроводниковым запоминающим устройствам. Известны иижекционные ячейки памяти в запо минающих устройствах с совмещенной структурой в диффузионных областях. Эти ячейки памЯти° построенные полностью на полупроводниковых структурах, обеспечивают высокую степень интеграции элементов, низкую потребляемую мощность и предназначены дпя построения запоминающих устройств с произвольной выборкой 1, 2. Из известных ячеек памяти наиболее близкой к изобретению по технической сущности является ячейка памяти, содержащая первый и второй п-р-и-транзисторы, соединенные перекрестной связью, эмиттеры которых подключены к шине нулевого потенциала, а коллекторы к соответствующим коллекторам первого р-п-р транзистора - к соответствующим коллекторам транзистора, база которого подключена к щине нулевого потенциала, а эмиттер к щине пита ния, и две разрядные щины 3. Эта известная ячейка памяти имеет относительно большую потребляемую мощность в режи ле згшиси и низкое быстродействие. Целью изобретения является уменьшение потребляемой мощности при записи информации и повыщение быстродействия,В предлагаемой ячейке памяти это достигается тем, что в нее введены третий п-р-п-траызкстор, щина блокировки, два резистора и второй,третий, четвертый и пятый р-и-р-транзисторы, базы которых подключены кшине нулевого потенциала, змиттеры второго и третьего р-и-р-транзисторов соединены с коллекторами четвертого и пятого р-и-ртранзисторов, с коллекторами третьего п-р-птранзистора и через соответствующие резисторы подключены к щине питания, змиттеры четвертого и пятого р-п-р-транзисторов соединены с соответствующими разрядными щинами, щина блокировки подключена к базе третьего п-р-птранзистора, эмиттер которого соединен с шиной нулевого потенциала. Кроме того, в ячейку памяти введены щина считывания, а второй и-р-л-транзистор выполнен двухколлекторным, второй коллектор которого соединен с шиной считывания. На фиг, 1 представлена электрическая схема предлагаемой ячейки; на фиг. 2 - то же, вариант топологии с одноуровневой металлизацией. Ячейка памяти представляет собой триггер на совмещенных полупроводниковых структурах, которые представлены на электрической схеме своими эквивалентами. Она содержит первый 1, второй 2, третий 3, четвертый 4 и пя|Тый 5 р-и-р-транзисторы, первый 6, второй 7, и третий 8 п-р-п транзисторы, два резистора 9 и 10, шину 11 гштания, шину 12 нулевого потенциала, разрядные шины 13 и 14 и шину 15 считывания. Считывание информации осушествляется подачей импульса в шйну 11, в результате чего в зависимости от хранимой информаш и на шине считывания появляется соответствуюищй ток В режиме записи ток в шине питания понижается, а шина нулевого потенциала отключается, при этом в соответствующую разрядную шину 13 или 14 подается импульс тока. В результате несимметрии в питании ячейки пймяти, она устанавливается в соответствующее. положение. В режиме хранения информации ток в шине 11 понижается, в шину 12 невыбраш1ых слоев подается зтиеньшенный ток, поэтому в ячейках памяти информация не искажается. Преимущество предлагаемой ячейки памяти по сравнению с известной заключается в зна чительном снижении потребляемой мощности в режиме записи, обусловлетюм тем, что ток задается только в выбранную разрядную шину, а не во все невыбранные, а также в том, что счи тывание производится непосредственно с транзи тора триггера через дополнительный коллектор. Площадь ячейки памяти при этом увеличиваетсй всего на 20% по сравнению с известной. . ; 6 64 Формула изобретения 1. Ячейка памяти, содержащая первый и второй и-р-«-транзисторы, соединенные перекрестной связью, эмиттеры которых подключены к шине нулевого потенциала, а коллекторы - к соответствующим коллекторам первого р-п-ртранзистора, база которого подключена к щине нулевого потенциала, а эмиттер - к 1лине питания, и две разрядные шины, л и ч а ю щ а я с я тем, что, с целью уменьшения потребляемой мощности при записи информации и повьп-цения быстродействия ячейки памяти, она содержит третий и-р-«-транзистор, шину блокировки, два резистора и второй, третий,четвер тый и пятый p- j-p-транзисторы, базы которых подключены к шине нулевого потенциала, эмиттеры второго и третьего р-и-р-транзисторов соединены с коллекторами четвертого и пятого р-п-р-транзисторов, с коллекторами третьего и-р-н-транзистора и через соответствующие резисторы подключены к шине питания, змигтеры четвертого и пятого р-и-р-транзисторов соединены с соответствующими разрядными шинами, шина блокировки подключена к базе третьего 1«-р-и-транзистора, эмиттер которого соединен с шиной нулевого потенциала. 2. Ячейка памяти по п. 1,отличающаяс я тем, что она содержит шину считывания, а второй п-р-п транзистор выполнен двухколлекторным, второй коллектор которого соединен с шиной считывания. Источники информации, принятые во внимание при экспертизе: 1. Микрозлектроника. 1977, т.6, вып. 2, с. 08. 2. Электроника -(пер. с англ.). 1972, N 4, с, 42-46. ,a.s.k.wiedtnann,High-I)ensitij Static БшоКар Memopu,Widest of Technicae Pcipers,3EEE aS5-CC,1973, ,p.9i-92. //

/3

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для регистра сдвига | 1979 |

|

SU851495A1 |

| Буферный логический элемент и @ л типа | 1981 |

|

SU980289A1 |

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Регистр сдвига | 1982 |

|

SU1136217A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU902243A1 |

| Ячейка памяти | 1974 |

|

SU546935A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU868840A1 |

| Устройство для хранения и выборки информации | 1975 |

|

SU553685A1 |

| Устройство для выборки координатных шин магнитного накопителя | 1983 |

|

SU1140177A1 |

Авторы

Даты

1978-12-15—Публикация

1977-07-05—Подача