Изобретение относится к полупроводниковым запоминающим устройствам. : Известна матрица элементов памяти, вы пояненная на основе инжекционного элемента памяти. Известный элемент памяти содержит бистабильную ячейку, образованную двумя п-р-п транзисторами и двух коллекторным р-п-р транзистором. Для записи-считывания информации служат дополнительные (вторые) коллекторы п-р-п транзисторов, подключенные к разрядным шинам {. Недостатком матрицы, выполн енной на основе описанного элемента памяти, является необходимость введеиия изоляции между отдельными строками матрицы, что связаио с недопустимостью электрической связи между ними и что значительно усложняет технологию изготовления больших интегральных схем памяти, содержащей эту матрицу. Известна также матрица инжекцнЬнных элементов памяти, которая может быть изготовлена без изоляции отдельных строк или рядов 2. Однако базовий элемент памяти данной матрицы содержит большое число дополнительных логических иижекционных вентилей -: 2 для выборки элемента памяти .в матрице и для управления им при запжи и считыйании информации. Это существенно увеличивает площадь элементов памяти и матрицы в целом и снижает ее быстродействие при считывании и записи. Наиболее близким техническим решением является полупроводниковое интегральное запоминающее устройство, содержащее элементы памяти, адресные игины и разрядные , щины записи и считывания. Каждый элемент памяти содержит бистабильнук) ячейку, образованную первым и вторым п-р-п транзисторами с перехрестно связанными базами и коллекторами и дчухколлекториым третьим транзистором р-п-р типа. Первый транзистор п-р-п типа имеет дополнительный коллектор для считывания информации. Эмиттер третьего р-п-р транзистора подключен к словарной шин€, а коллекторы - к базам первого и втброго транзисторов соответственно. Для записи информации служат четвертый и питый транзисторы р-п-р типа, эмиттеры которых подключены к разрядным шинам, а коллекторы к багзам норного и второго транзисторов. Пятым р-п-р транзистор имеет дополкительпый кол/юктор, содиненный со вторым коллектором первого -р-п транзистора. К этой же точке подклюен . коллектор шестого п-р-п транзистора, аза которого подключена к словарной шине. очка об-ьедйнения коллекторов подсседиена к базе выходного седьмого п-р-п транистора считывания, коллектор ко-горого подлючен к разрядной шине считывания. Базы все:х р-п-р транзисторов и эмиттеры всех п-р-п транзисторов соединены с общей точкой. В режиме хранения все р-п-р транзисоры эле MieHT а памяти открыты и бистабильная ячейка находится в одном из двух устойчивых состояний. Выборка строки матрицы производится снижением потенциала адресной шиш и быключениём третьего транзистора. При записи, одновременно с сигналом выборки, выключается один из р-п-р Транзисторов записи, а считывание осуществляется при подаче сигнала выборки. При этом закрывается шестой q-p-n транзистор и. снимается запрещающийсигнал с базы выходного транзистора, что приводит к его включению и снижению потенциала разрядной шины считывания до уровня логического «О, в случае, если элемент .памяти хранит его, т. е. если открыт второй п-р-п транзистор. . .

Недостатками матрицы подобных элементов памяти ЯВ.ТЯЮТСЯ введение для считывания информации двух инверторов на п-рП транзисторах, что вызывает заметное возрастание мощности.потребления, невысокое быстродействие при считывании информации, которое объясняется тем, что относительно большая паразитная емкость шины считывания перезаряжается с помощью ин-. RJepTopa,на выходном п-р-п транзисторе, базовый ток которого невелик (часть toKa хранения).....

Цель изобретения - повышение ее.быстродействия при считывании информации и уменьшение рассеиваемой мощности. ;

Указанная цель достигается тем, что в матрйч юе запоминающее устройство, содержащее группы ячеек памяти, каждая из которых выподнена т пяти транзисторах, первый и второй из Которых соединены ПО триггерной схеме, коллектор третьего и первый коллектор четвертого транзисторов соединены с коллектором первого транзйЬТбра, второй коллектор четвертого и коллектор пятого транзисторов соединены с коллектором второго транзистора, эмиттеры первого и второго транзисторов соединены с шиной нулевого потенциала и базами четвертого и пятого транзисторов, эмиттер третьего транз истора соединен с первой разрядной щиной, эииттёр четвертого транзистора тодклйчен к адресной шине, эмиттер пятого транзистора подсоединен ко второй разрядной шине, усилители считывания, каждый из которых выполнен на четырех транзисторах, базы шестого и седьмого из которых подключены

К шине нулевого потенциала и эмиттеру восьмого транзистора, эмиттер девятого транзистора соединен с базой шестого транзистора, информационную шину, шину питания, ширту разрёшеттия считывания и тину считывания, в нем вторые; коллекторы первых транзисторов каждой группы ячеек памяти подключены к информационной шине, к коллектору восьмого, базе девятого и коллектору шестого транзисторов, эмиттер шестого транзистора соединен с шиной питания, эмиттер седьмого транзистора соединен с шиной разрешения считывания, коллектор седьмого транзистора соединен с базой восьмого транзистора, коллектор девятого транзис.тора соединён с Шиной считывания.

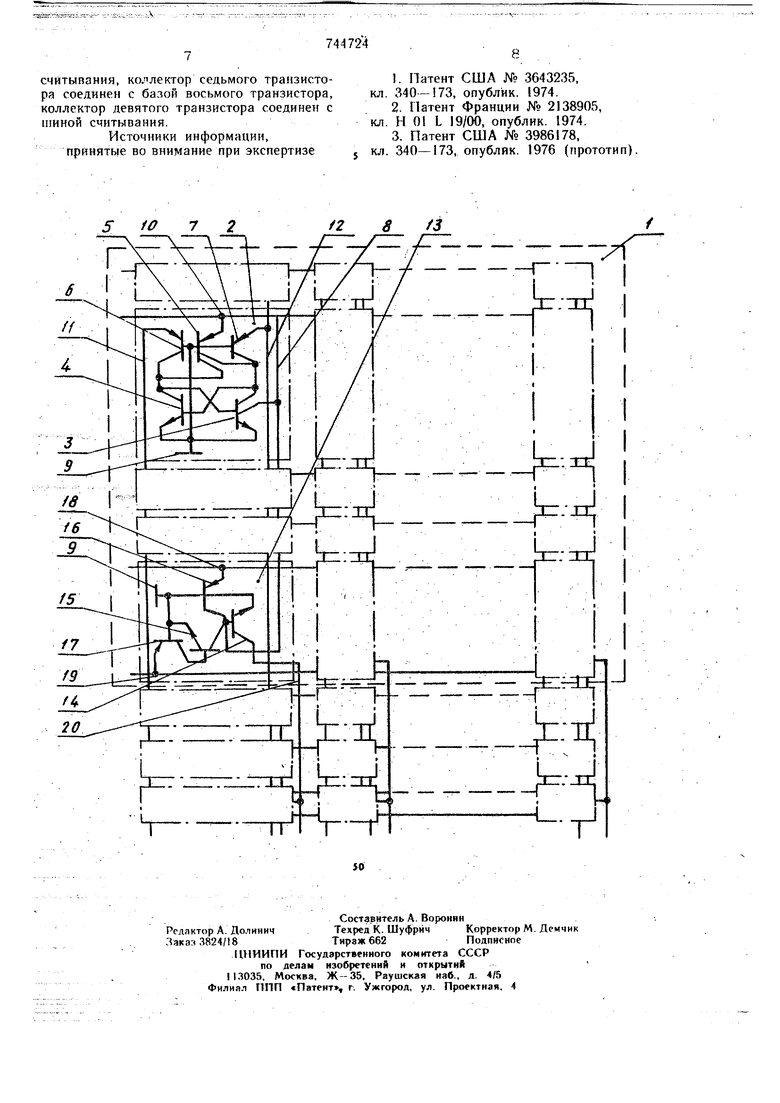

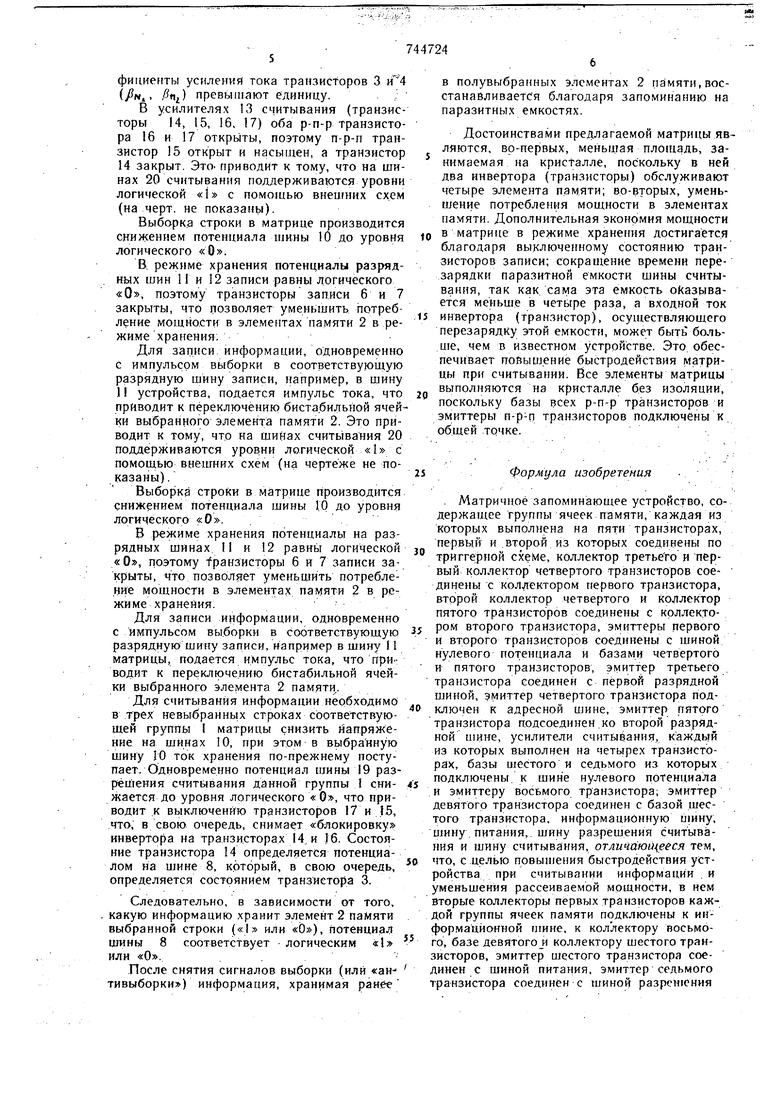

На чертеже представлен;з электрическая схема устройства,. ,

Матричное запоминающее устройство разбито на группы ячеек.памяти 1,по четыре строки в, каждо.й группе. Элемент 2 .памяти содержит бистабйльную ячейку, образован0 йую, например, п-р-п транзисторами 3 и 4, и р-п-р транзистОром 5. Цепи записи элемента 2 памяти образованы, например, р-п-р транзисторами 6 и 7. х . .

База и коллектор транзистора 4 соединены соответственно с одним из коллекторов и базой транзистора 3, второй Коллектор транзистора 3 соединен с информационной шиной 8. Первый и второй; коллекторы р-п-р транзистора 5 соединены .соответственно с коллекторами п-р-п транзисторов 3 и 4 и

O р-п-р транзисторов 7 и б. Базы р-п-р транзисторов 5, 6, 7 и эмитТерЫ п-р-п транзисторов 3 и 4 соединены, вместе и подключены к шине 9 нулевого потенциала. Эмиттер р-п-р транзистора 5 подключен к адресной шине 10, а эмиттеры р-п-р гранзисторов

6 и 7 подключены соотвётстбенио к разрядньш щинам П и 12. Элементы 2 памяТи каждого столбца одной группы 1 подключены к усилителю 13 считывания, состоящему, например, из п-р-п транзисторов 14

() и 15 и р-п-р транзисторов 16 и 17, причем : эМйттеры п-р ПТранзисторов 14 и 15 и п-базы р-п-р транзисторов 16 и 17 соединены вместе и подключены к. шине 9, эмиттер, р-п.-р транзистора 16 подключен к шине 18 питания, эмиттер р-п-р транзистора 17 под кл:ючен к шине 19 разрешения считывания, коллекторы транзисторов 15, 16 и база транзистора 14 соединены вместе и подключены к шине 8, а коллектор транзистора 14 подключен к шике 20 считывания.

.Устройство работает следущим образой. В режиме хранения в адресную шину Ю поступает ток от источника питания (на чертеже не показан), который распределяется между элементами 2 памяти, подключенны5 Ш К шине 10. Коллекторные токи транзистора 5 в первом приближении равны, поэтому элемент 2 памяти мОжет находиться в любом состоянии «О или «1, если коэффипиеиты усиления тока транзисторов 3 {fn, /Ц) превышают единицу.. , В усилителях 13 считывания (транзисторы 14, 15, 16, 17) оба р-п-р транзистора 16 и 17 открыты, поэтому п-р-п транзистор 15 открыт и насыщен, а транзистор 14 закрыт. Это. приводит к тому, что на шинах 20 считывания поддерживаются уровни логической «1 с помощью внешних схем (на черт, не показаны). Выборка строки в матрице производится снижением потенциала шины 10 до уровня логического «О -т В. режиме хранения потенциалы разрядных шин II и 12 записи равны логического «0, поэтому транзисторы записи б и 7 закрыты, что позволяет Уменьшить потребление мощности в элементах памяти 2 в режиме хранения Для записиинформации, одновременно с импульсом выборки в соответствующую разрядную шину записи, например, в шину 11 устройства, подается импульс тока, что приводит к переключению бистабильной ячейки выбранного элемента памяти 2. Это приводит к тому, что на шинах считывания 20 поддерживаются уровни логической «1 с помоц ью внешних схем (на чертеже не показаны). Выборка строки в матрице производится снижением потенциала шины 10 до уровня логического «О. В режиме хранения потенциалы на разрядных шинах II и 12 равны логической «0 поэтому fpaнзиcтopы 6 и 7 записи закрыты, что позволяет уменьшить потребление мощности в э.лементах памяти 2 в режиме хранения Для записи информации, одновременно с импульсом выборки в соответствующую разрядную шину записи, например в щинуП матриць, подается импульс тока, что приводит к переключению бистабильной ячейки выбранного элемента 2 памяти. Для считывания информации необходимо в трех невыбраиных строках соответствуюг . гJ щей группы I матрицы снизить напряжение на шинах 10, при этом в вь1браиную шину 10 ток хранения по-прежнему поступает. Одновременно потенциал шины 19 разрешения считывания данной группы 1 сни- жается до уровня логического «О, что приводит .к выключению транзисторов 17 и .15, что, в свою очередь, снимает «блокировку инвертора на транзисторах i4, и 16. Состояние транзистора 14 определяется потенциалом шине8, который, в свою очередь, м , определяется состоянием транзистора 3. Следовательно, в зависимости от того, какую информацию хранит элемент 2 памяти выбранной строки («I или «О), потенциал шины 8 соответствует логическим «I или «О... После снятия сигналов выборки (или «антивыборки) информация, хранимая ранее в полувыбранных элементах 2 памяти,восстанавливается благодаря запоминанию на паразитных емкостях. Достоинствами предлагаемой матрицы являются, во-первых, меньшая площадь, занимаемая на кpиctaллe, поскольку в ней два инвертора (транзисторы) обслуживают четыре элемента памяти; во-вторых, уменьшение потребления мошности в элементах памяти. Дополнительная экономия мошности в матрице в режиме хранения достигается благодаря выключенному состоянию транзисторов записи; со крашение времени перезарядки паразитной емкости шины считы ния, так как сама эта емкость оКазыва « . P . а входной ток инвертора (транзистор), осуществляющего перезарядку этой емкости, может быть бать е- в известном устройстве. Это. обеспечивает побыш.ение быстродействия матри«ьг при считывании. Все элементы матрицы выполняются на кристалле без изоляции, поскольку базы всех р-п-р транзисторов и эмиттеры п-р-п транзисторов подключены к общей точке. Формула изобретения . Матричное запоминающее устройство, содержащее группы ячеек памяти, каждая из которых выполнена на пяти транзисторах, Р «„второй из которых соединены по три/гернои схеме, коллектор третьего и первыи коллектор четвертого транзисторов соеД ол ектором первого транзистора, второй коллектор четвертого и коллектор транзисторов соединены с коллекторои второго транзистора, эмиттеры первого транзисторов соединены с шиной нулевого потенциала и базами четвертого ™° транзисторов, эмиттер третьего, транзистора соединен с первой разрядной четвертого транзистора подключей к адресной шине, эмитте р пятого транзистора подсоединен.ко второй разрядной шине, усилители считывания, каждый из которых выполнен на четырех транзисторах, базы шестого и седьмого из которых подключены, к шине нулевого потенциала и эмиттеру восьмого транзистора; эмиттер девятого транзистора соединен с базой шестого транзистора, информационную ижну, шину. питания,, шину разрешения считывания и шину считывания, отличающееся тем. . повышения быстродействия устройства при считывании информации . и уменьшения рассеиваемой мош.ности, в нем вторые коллекторы первых транзисторов кажой группы ячеек памяти подключены к инормационной П1ине, к коллектору восьмого, базе девятого и коллектору шестого транисторов, эмиттер шестого транзистора соеинен с шиной питания, эмиттер седьмого ранзистора соединен с шиной разрон ения

считывания, коллектор седьмого транзистора соединен с базой восьмого транзистора, коллектор девятого транзистора соединен с шиной считывания.

Источники информации, принятые во внимание при экспертизе

1.Патент США № 3643235, кл. 340-173, опублик. 1974.

2.Патент Франции № 2138905, кл. Н 01 L 19/00, опублик. 1974.

3.Патент США № 3986178,

кл. 340-173, опубляк. 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Ячейка памяти | 1974 |

|

SU546935A1 |

| Устройство управления записью-считыванием информации для полупроводникового запоминающего устройства | 1986 |

|

SU1367040A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| Усилитель записи-считывания | 1986 |

|

SU1437913A1 |

| Элемент памяти | 1989 |

|

SU1679552A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1575234A1 |

| Запоминающее устройство | 1975 |

|

SU613404A1 |

Авторы

Даты

1980-06-30—Публикация

1977-09-14—Подача