1

Изобретепие относится к вычислительной технике и, в частности, к адаптивным вычислительным устройствам, состоящим из многофункциональных элементов, в которых при появлении отказов автоматически производится перестройка структуры с целью восстановления правильного функционирования устройства. Оно может быть применено в адаптивных цифровых вычислительных машинах, имеющих высокую живучесть, при ограниченной надежности элементов.

Известно адаптивное вычислительное устройство 1, содержащее функционально устойчивую сеть на многофункциональных пороговых элементах, узел регулировки, схемы сравнения, регистр, и логические схемы.

Недостатком известного является возможность вынолИения только логических функций и значительной временной избыточности.

Известно адаптивное вычислительное устройство, содержащее многофункциональное логическое устройство, анализатор, селектор операций и вспомогательное оборудование 2.

Недостатком известного является функциональная ограниченность в выполнении только логических функций, выполняемых

многофункциональным логическим устройством.

Наиболее близким техническим решением к данному изобретению является адаптииное вычислительное устройство 3. содержащее многофункциональные модули, блок контроля, элементы И, ИЛИ-НЕ, НЕ, коммутаторы, кольцевые регистры, генератор тактовых импульсов.

Известное устройство обладает недостатком, заключающимся в его функциональной ограниченности параллельным выполнением только независимых между собой функций, возложенных на модули. В нем невозможна организация как последовательного, так и параллельно последовательного процесса вычисления функций в случае их зависимости, т. е. когда результат вычисления некоторых из них является входным воздействием для круглых функций. Кроме того, надежность известного адаптивного вычислительного устройства ограничена возможностью восстановления функционирования возложением функци) отказавшего модуля на соседний модуль.

Целью изобретения является расширение функциональных возможностей за счет увеличения числа реализуемых функций и повышения надежности устройства.

Для этого адаптивное вычислительное устройство содержит блоки памяти и регистр сдвига, при этом входы устройства соединены с информационными входами регистра сдвига, выходы которого через первый коммутатор соединены с первой группой входов второго коммутатора, вторая группа входов которого соединена с первой группой выходов первого бока памяти, настроечными входами многофункциональных модулей и с первой группой входов третьего коммутатора, выходы второго коммутатора через многофункциональные модули соединены со второй группой входов третьего коммутатора, выходы которого соедирюны с информационными входами регистра сдвига, тактирующий вход регистра сдвига соединен с выходом элемента ИЛИ-НЕ и с тактирующим входом первого кольцевого регистра, выходы которого через второй блок памяти подключены к нервой группе входов первого блока памяти, вторая группа входов которого соединена с первой группой входов третьего блока памяти, первый выход которого соединен с первым входом элемента И, второй вход которого подключен к выходу генератора тактовых импульсов, выход элемента И подключен к тактирующему входу второго кольцевого регистра и через элемент НЕ к управляющему входу первого блока памяти, выходы второго кольцевого регистра подключены ко второй группе входов третьего блока памяти, третьи группы входов первого и третьего блоков памяти соединены со входами элемента ИЛИ-НЕ и нервой группой входов блока контроля, вторая группа входов которого соединена с тестовыми выходами многофункциональных модулей, четвертая группа входов первого блока памяти соединена со второй группой выходов третьего блока памяти.

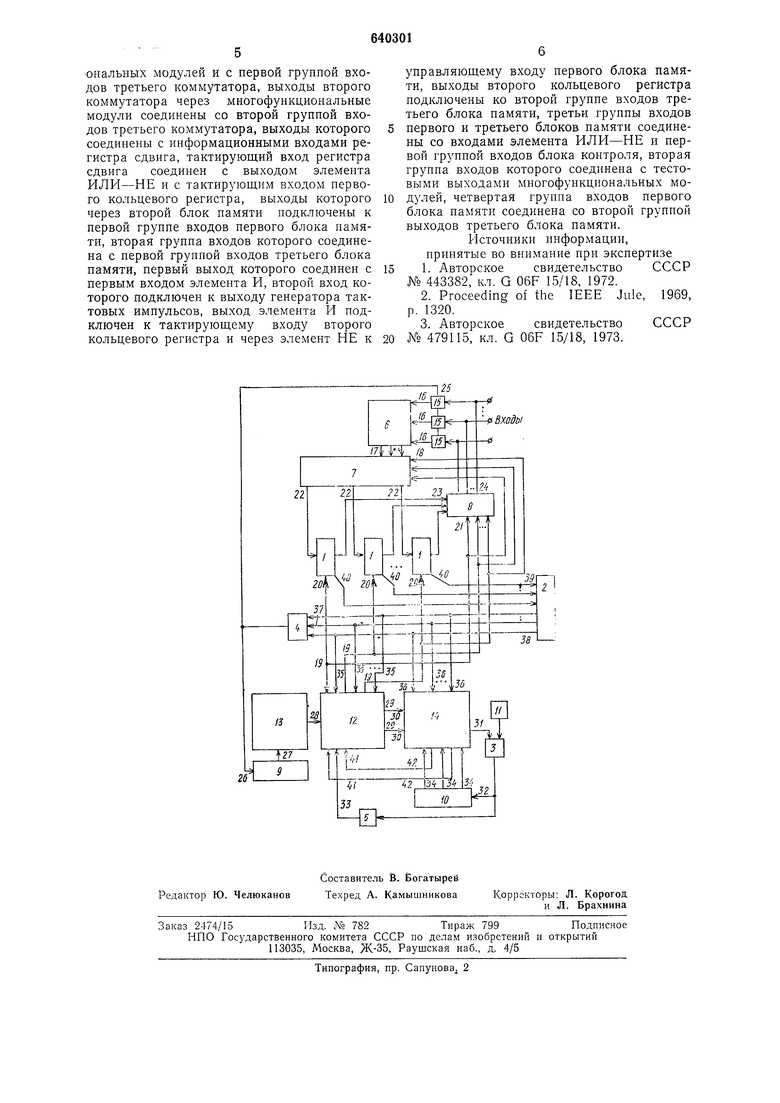

На чертеже представлена блок-схема предлагаемого устройства.

Адаптивное вычислительное устройство содержит многофункциональные модули 1, блок контроля 2, элементы И 3, ИЛИ-НЕ 4, НЕ 5, коммутаторы 6, 7, 8, кольцевые регистры 9, 10, генератор тактовых импульсов И, блоки памяти 12, 13, 14 и регистры сдвига 15, выходы регистра сдвига 16, первая группа коммутатора 17, вторая группа входов коммутатора 7-18, первая группа выходов блока памяти 12-19, настроечные входы 20, первая группа входов коммутатора 8-21, выходы коммутатора 7-22, вторая группа входов коммутатора 8-23, выходы коммутатора 8-23, тактирующий вход регистров 15-25, тактирующий вход кольцевого регистра 9-26, выходы кольцевого регистра 9-27, первая группа входов блока памяти 12-28, вторая группа выходов блока памяти 12-29, первая группа входов блока памяти 14-30, первый выход блока памяти 14-31, тактирующий вход

кольцевого регистра 10-32, второй вход блока памяти 12-33, вторая группа входов блока памяти 14-34, третьи группы входов 35, 36 первого 12 и третьего 4 блоков памяти, входы элемента ИЛИ-НЕ 4-37, группа выходов блока контроля 2-38, группа входов блока контроля 2-39, тестовые выходы многофункциональных модулей 1 - 40, четвертая группа входов блока памяти

12-41, вторая группа выходов третьего блока памяти 14-42.

Многофункциональные модули 1 способны настраиваться на вынолнение одной функции из некоторого множества {/ь ...,

fn}- При этом система многофункциональных модулей предназначена для выполпения некоторой функции {/i,..., /«}, составленной из множества функций {/i,..., fn} или его подмножества, причем некоторые

функции могут быть зависимы друг от друга, т. е. результат вычисления одних функций необходим для вычисления других. Таким образом некоторые составляющие функции могут быть вычислены параллельно, а некоторые только последовательно в определенном порядке, т. е. в общем случае, процесс вычисления функции F будет параллельно последовательным. В предлагаемом устройстве блок памяти

13 предназначен для задания функции , ..., fn}, возложенной на систему. Блок памяти 12 предназначен для настройки многофункциональных модулей 1 на реализацию функций, вычисляемых в текущем такте. Блок намяти 14 предназначен для хранения информации о способности многофункциональных модулей 1 выполнять функции /1, /2, .-., fn, теряемые в процессе эксплуатации. Посредством блоков памяти

12, 14, производящих логическую обработку хранимой в них информацией, осуществляется восстановление функционирования после отказа путем перераспределеиия функций, возложенных на многофункциональные модули 1.

Формула изобретения

Адаптивное вычислительное устройство,

содержащее многофункциональные модули, блок контроля, элементы И, ИЛИ-НЕ, НЕ, коммутаторы, кольцевые регистры, генератор тактовых импульсов, отличающееся тем, что, с целью расщирения функциональных возможностей за счет увеличения числа реализуемых функций и повышения надежности, устройство содержит блоки памяти и регистр сдвига, при этом входы устройства соединены с информационными

входами регистра сдвига, выходы которого через первый коммутатор соединены с нервой группой входов второго коммутатора, вторая группа входов которого соединена с первой группой выходов первого блока памяти, настроечными входами многофункци

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное вычислительное устройство | 1977 |

|

SU734679A1 |

| Адаптивное вычислительное устройство | 1976 |

|

SU694864A1 |

| Адаптивное вычислительное устройство | 1977 |

|

SU696446A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕРАСПРЕДЕЛЕНИЯ ЗАДАЧ МЕЖДУ ПРОЦЕССОРАМИ | 1991 |

|

RU2023292C1 |

| Адаптивное вычислительное устройство | 1984 |

|

SU1203506A1 |

| ЦИФРОВОЙ ГРУППОВОЙ ПРИЕМНИК СИГНАЛОВ УПРАВЛЕНИЯ И ВЗАИМОДЕЙСТВИЯ С АДАПТИВНОЙ ДИФФЕРЕНЦИАЛЬНОЙ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1993 |

|

RU2103840C1 |

| Адаптивное вычислительное устройство | 1980 |

|

SU957214A1 |

| Адаптивное вычислительное устройство | 1983 |

|

SU1187170A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1982 |

|

SU1072036A1 |

| Универсальный вычислительный автомат | 1983 |

|

SU1196844A1 |

Авторы

Даты

1978-12-30—Публикация

1976-08-04—Подача