1

Изобретение относится к радиосвязи и может использоваться в синхронизации двоичных сигналов в телеграфии, системах передачи даиных и системах автоматизированного управления.

По основному авт. св. № 403096 известно устройство для синхронизации двончпых сигналов, содержащее генератор, подключенный через каскады вычитания н добавления импульсов к входу делителя частоты, выходы когорого соединены с первыми входами трех фазовых дискрнмина10ров, вторые входы двух фазовых дискриминаторов подключены к выходу каскада формирования фронтов сигнала, первые выходы двух фазовых дискриминаторов соединены со вторым входом третьего фазового дискриминатора, а вторые выходы соедииепы с включенными последовательно реверсивным счетчиком и блоком переменного коррекционного эффекта, выходы которого подключены к каскадам вычитания и добавления импульсов параллельно выходам третьего фазового дискриминатора.

Однако данное устройство имеет большое время вхождения в синхронизм.

Цель изобретения - сокращение времени вхождения в синхронизм и повыщение помехоустойчивости.

2

Для этого в ycTpuiiCTBO для сипхроиизации двоичных сигналов, содержащее геператор, подключенный через каскады вычнlariiiH и дооавлення импульсов к входу делитсля частоты, выходы которого соедппепы с первыми входами трех фазовых днскрпминаюрОБ, вторые входы двух фазовых дискри.минаторов подключены к выходу каскада формнрования фронгов сигнала, нервые выходы двух фазовых дискриминаторов соеди11ены со вторым входом третьего фазового дискрнынпагора, а вторые выходы соединены с включепныл последовательно реверс11вныл1 счетчиком и блоком неременного коррекционного эффекта, вььчоды коюрого подключены к каскадам вычитания и добавления импульсов параллельпо выходам третьего фазового дискрпмпнатора, введены анализатор фазы входного сигнала и

олок сравнения фаз, ири этом вход каскада формнрования фронтов сигнала соединен с одним из входов анализатора фазы входного сигиала, к другим входам которого подключены соответственно входы реверспвного счетчика и выходы третьего фазового дискриминатора, а выходы анализатора фазы входного сигнала подключены соответственно к дополнительным входам блока переменного коррекциониого эффекта и реверсивного счетчика и к одним из входов блока сравнения фаз, к другим входам которого подключены соответственно выходы двух фазовых дискриминаторов, а выходы блока сравнения фаз подключены к дополнительным входам каскадов вычитания и добавления импульсов, причем соответствующий выход делителя частоты подключен к сиихронизирующему входу каскада формирования фронтов сигнала.

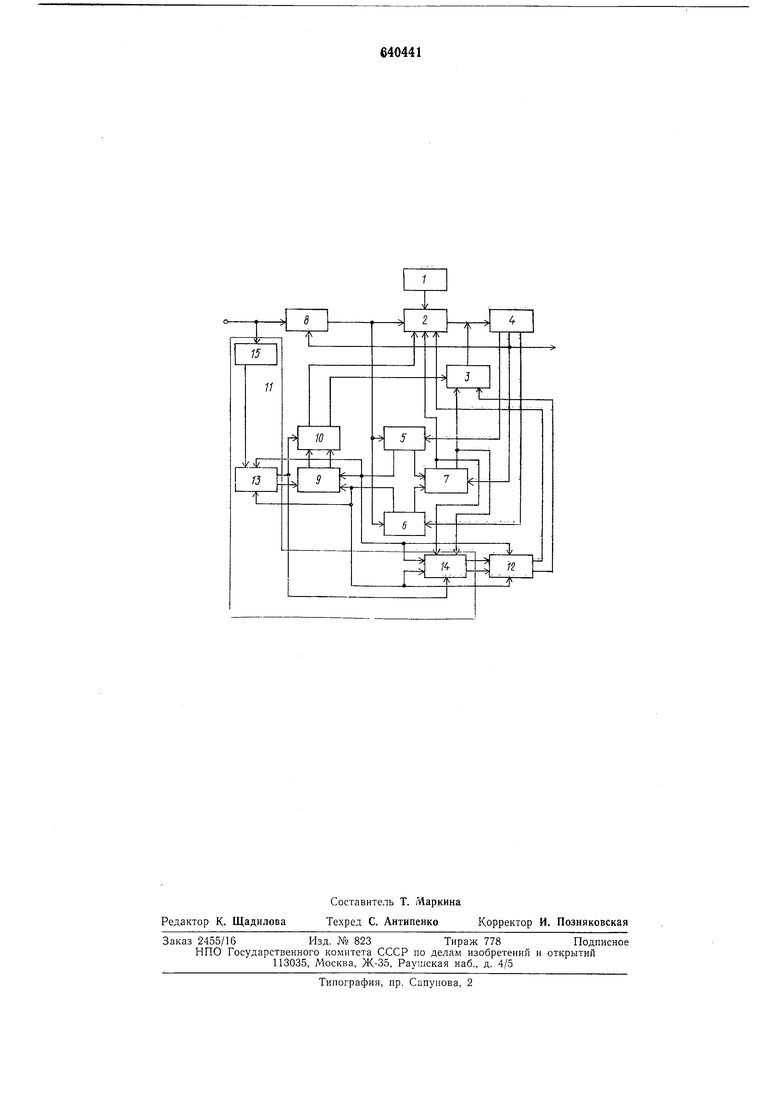

На чертеже изображена структурная электрическая схема предложенного устройства.

Устройство для синхронизации двоичных сигналов содержит генератор 1, подключенный через каскады вычитания 2 и добавления 6 импульсов к входу делителя 4 частоты, выходы которого соединены с нервыми входами трех фазовых дискримииаторов 5-7, вторые входы двух фазовых дискриминаторов б и 6 подключены к выходу каскада формирования 8 фронтов сигнала, первые выходы двух фазовых дискриминаторов 5 и 6 соединены со вторым входом третьего фазового дискриминатора 7, а вторые выходы соединены с включенными иоследовательно реверсивным счетчиком 9 и блоком 10 иеременного коррекционного эффекта, выходы которого подключены к каскадам вычитания 2 н добавления 3 импульсов параллельно выходам третьего фазового дискримииатора 7, а также анализатор 11 фазы входного сигнала и блок 12 сравнения фаз, нрн этом вход каскада формирования

8фронтов сигнала соединен с одним из входов анализатора il фазы входного сигнала, к другим входам которого подключены соответственно входы реверсивного счетчика

9и выходы третьего фазового дискриминатора 7, а выходы анализатора И фазы входного сигнала подключены соответственно к дополнительным входам блока 10 переменного коррекционного эффекта и реверсивного счетчика 9 и к одним из входов блока 12 сравнения фаз, к другим входам которого подключены соответственно выходы двух фазовых дискриминаторов 5 н 6, а выходы блока 12 сравнения фаз подключены к донолнительным входам каскадов вычитания 2 и добавления 3 импульсов, причем соответствующий выход делителя 4 частоты подключен к синхронизирующему входу каскада формирования 8 фронтов сигиала.

Устройство работает следующим образом.

Импульсы с каскада формирования 8, соответствующие границам или срединам между элементами сигнала, поступают на фазовые дискриминаторы 5 и 6. Если временное рассогласование между этими импульсами и импульсами на выходе делителя 4 превышает величину выбранного временного интервала Д/, то с фазовых дискриминаторов 5 или 6 в зависимости от знака рассогласования постунают нмпульсы на реверсивный счетчик 9, в блок 13 унравления,

блок 14 определения математического ожидания фазы и блок 12 сравнения. Одновременно с этим в блоке 15 измерения параметров канала связи определяется качество канала связи. Результат измерения поступает на блок 13 управления. В блоке 14 определения математического ожидания фазы онределяется математическое ожидание фазы синхросигнала. При хорощем качестве канала связи, когда коэффициент передачи канала связи находится в заданных пределах, с выхода блока 13 управления на реверсивный счетчик 9 поступает сигнал на уменьшение емкости счетчика.

Импульсы с реверсивного счетчика 9 иоступают на блок 10 переменного коррекционного эффекта и далее на каскады вычитания 2 или добавлеиия 3. При достаточно большом фазовом рассогласованни, превышающсм А/, и хорошем качестве канала связи работают эти цепи, тем самым обеспечивается быстрое вхождение в снихронизм. При плохом качестве канала связи и большом фазовом рассогласовании, т. е. при

наличии сильных сосредоточенных помех, способных вывести систему на синхронизма, с блока 13 управления на блок 10 переменного коррекционного эфф&к-а ноступает сигиал, запрещающий его работу. Коррекция фазы по данной цени прекращается. Этот же сигнал, поступая на блок 14 определения математического ожидания фазы, осуществляет съем математического ожидания фазы синхросигнала. При этом математическое ожидание фазы синхросигнала определяется величиной рассогласования - сигналами с выходов фазовых дискриминаторов 5 или 6. В блоке 12 сравнения осуществляется сравнение математического ожиДания фазы синхросигнала с действительным значением фазы в данный момент - имиульсами с выходов фазовых дискриминаторов 5 или 6. Сигналы коррекции с выходов блока 12

сравиения поступают на каскады вычитания 2 или добавления 3 импульсов.

Таким образом, на время «ненадежности канала связи коррекция фазы синхросигнала осуществляется по ее математическому

ожиданию, определенному на предыдущем этапе. Тем самым исключается выход системы из синхронизма на время действия сильных сосредоточенных помех, увеличивается точность синхронизации и помехоустойчивость приема сигналов за счет исключения ошибок синхронизации.

Если фазовое рассогласование мало (меньше А), то с фазовых дискриминаторов 5 или 6 импульсы поступают на фазовый дискриминатор 7, где их положение сопоставляется с временем появления импульсов с делителя 4. В зависимости от. знака рассогласования с фазового дискриминатора 7 поступают управляющие импульсы на

каскады вычитаиия 2 или добавления 3. Эти

же импульсы поступают на блок 14 определения математического ожидания фазы синхросигнала.

В установившемся режиме при малом фазовом рассогласовании значительно смещенные во времени единичные импульсы с выхода каскада формирования 8 не оказывают влияния на работу устройства. В этом режиме весьма мала вероятность того, что с выхода реверсивного счетчика 9 подается импульс на блок 10 переменного коррекционного эффекта.

Таким образом, ввиду того, что на работу устройства не влияют одиночные сильно смещенные элементы входного сигнала, точность его работы повышается.

В установившемся режиме при появлении сильной сосредоточенной помехи прекращается работа блока 10 переменного коррекцлонного эффекта, осуществляется съем математического ожидания фазы синхросигнала, начинает работать блок 12 сравнения.

В этом режиме математическое ожидание фазы синхросигнала определяется в основном импульсами с выхода фазового дискриминатора 7. Подстройка фазы синхросигнала осуществляется по результатам сравнения этого математического ожидания с импульсами с выходов фазовых дискриминаторов 5 и 6.

Таким образом, в установившемся режиме при действии сильных сосредоточенных помех подстройка фазы синхросигнала осуществляется по результатам сравнения математического ожидания фазы, вычисленного в отсутствии помех, с расстройкой фазы, вызванной помехами. Тем самым исключается или сводится к минимуму действие сильных сосредоточенных помех на устройство синхронизации, исключается выход системы из синхронизма на время действия помех, увеличивается точность синхронизации и помехоустойчивость приемосигналов за счет исключения ошибок синхронизации.

Формула изобретения

Устройство для синхронизации двоичных сигналов по авт. св. № 403096, отличающееся тем, что, с целью сокращения времени вхождения в синхронизм и повышения

номехоустойчивости, в него введены анализатор фазы входного сигнала и блок сравнения фаз, при этом вход каскада формирования фронтов сигнала соединен с одним из входов анализатора фазы входного

сигиала, к другим входам которого подключены соответственно входы реверсивного счетчика и выходы третьего фазового дискриминатора, а выходы анализатора фазы входного сигиала подключены соответственно к дополнительным входам блока переменного коррекционного эффекта и реверсивного счетчика и к одним из входов блока сравнения фаз, к другим входам которого подключены соответственно выходы двух

фазовых дискриминаторов, а выходы блока сравнения фаз подключены к дополнительным входам каскадов вычитания и добавления импульсов, причем соответствующий выход делителя частоты подключен к синхронизирующему входу каскада формирования фронтов сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1980 |

|

SU886290A1 |

| Устройство синхронизации | 1977 |

|

SU658762A1 |

| Устройство синхронизации | 1981 |

|

SU1003376A1 |

| Устройство фазирования | 1976 |

|

SU604172A2 |

| Двухступенчатый регенератор | 1978 |

|

SU726668A1 |

| Устройство для синхронизации двоичных сигналов | 1975 |

|

SU544162A1 |

| Двухступенчатый регенератор | 1983 |

|

SU1197117A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU938419A1 |

| Устройство фазовой автоподстройки тактовой частоты | 1989 |

|

SU1721834A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

Авторы

Даты

1978-12-30—Публикация

1976-12-10—Подача