Изобретение относится к радиотехнике и может использоваться в системах связи, предназначенных для передачи дискретных сообщений, в телеграфии и в системах с им пульсно-кодовой модуляцией. Одно из известных устройств для синхр низации двоичных сигналов содержит делитель с добавлением с исключением импульсов, фазовый дискриминатор, выделитель фронтов, накопительное устройство на базе реверсивного счетчика для повышения точности фазирования, и устройство переменного коррекционного эффекта для уменьшения времени вхождения в фазу l. Однако в известном устройстве накопителг чое устройство и коррекционное устрой ство управляются выходом фазового дискриминатора, определяющим только знак фа зового рассогласования без указания на его точное значение, что снижает быстродействие таких устройств. Наиболее близким техническим решением является устройство для двоичных сигналов, содержашее задающий генератор, вы ход которого подключен к одному из входов делителя, к другому входу которого подключен вход выделителя фронтов сигнала 2. Однако это устройство не обладает достаточной точностью и быстродействием фазирования. Цель изобретения - повышение точности и быстродействия фазирования. Для этого в устройство для синхронизаации двоичных сигналов, содержашее задающий генератор, выход которого подключен к одному из входов делителя и к другому входу которого подключен вход выделителя фронтов сигнала, введены сумматор, счетчик на вычитание, счетчик на сложение и дополнительный выделитель фронтов, при этом выходы К разрядов делителя подключены к (k + m + 2 ) входам сумматора, выход последнего разряда которого подключен к управляющему входу делителя, а (k +1) выходы - к соответствующим входам счетчика на вычитание, к управляющему входу которого подключен выход счетчика на сложение, а выход счетчика на вычитание через выделитель фронтов сигнала подключен к входу обнулениесумматора, управляющий вход которого соединен со входом счетчика на сложение и с выходом дополнительного выделителя фронтов сигнала.

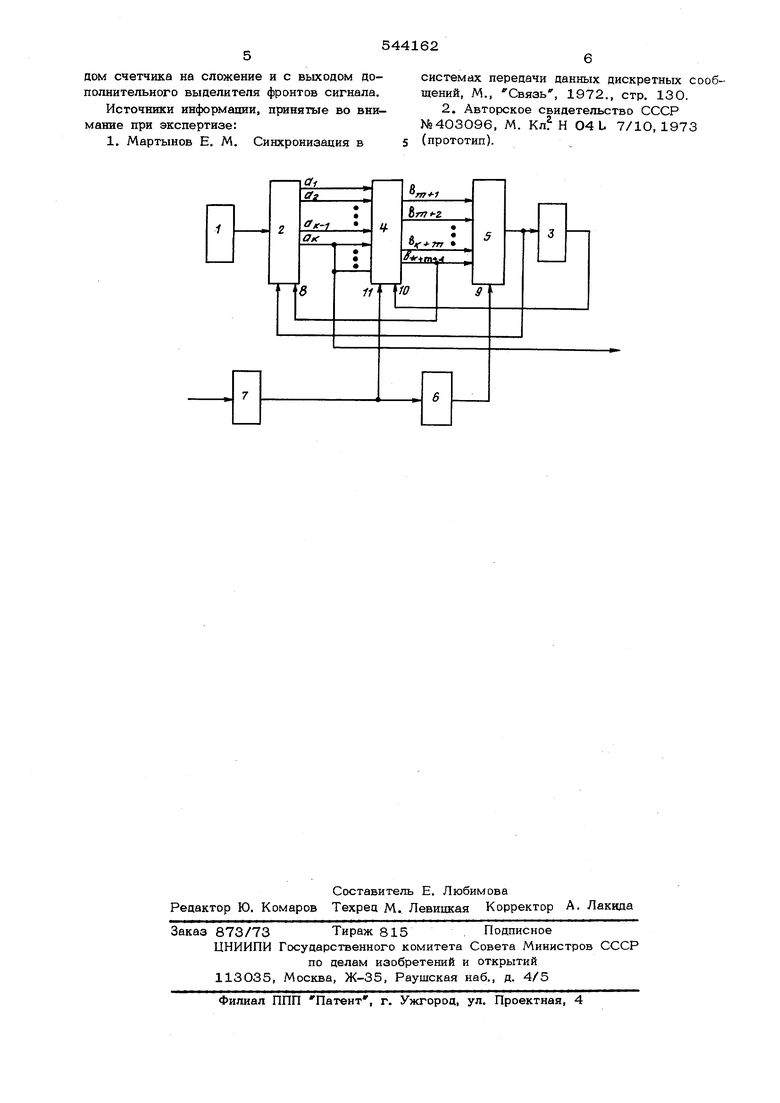

На чертеже представлена структурная

электрическая схема устройства для синхронизации двоичных сигналов.

Устройство содержит задающий генератор 1, выход которого подключен к одному из входов делителя 2, к другому входу которого подключен вход выделителя фронтов 3 сигнала, сумматор 4, счетчик на вычитание 5, счетчик на сложение 6, и дополнительный выделитель фронтов 7, при этом выходы ( ) К разрядов делителя 2 подключены + г1) входам сумматора 4, выход(Ь последнего разряда которого подключен к упрляющему входу 8 делителя 2, а (К-)--{ ) выходы (Ь В|(. VK соответствующим входам счетчика на вычитание 5, к управляющему входу 9 которого подключен выход счетчика на сложение 6, а выход счетчика на вычитание 5 через выделитель фронтов 3 сигнала подключен к входу обнуление 10 сумматора 4, управляющий вход 11 которого соединен со входом счетчика на сложение бис выходом дополнительного выделителя фронтов 7 сигнала.

Устройство работает следующим образом Последовательность высокочастотных импульсов с задающего генератора 1 поступает на счетный вход делителя 2 с коэффициентом деления 2 .

С входа устройства на вход дополнительного выделителя фронтов 7 поступает сигна данных. Сигнал на выходе дополнительного выделителя фронтов 7 длительностью в один период высокочастотного колебания задающего генератора 1, определяющий значащи момент сигнала данных,поступает на вход счечика на сложение 6 и на управляющий вход 11 сумматора 4. Производится считывание двоичного состояния делителя 2 и сложение модифицированного обратного кода этого

состояния с содержимым сумматора 4.

В исходном состоянии цикла накопленияусреднения содержимое сумматора 4 равно нулю. Счетчик на сложение 6 с емкостью 2 производит сложение поступающих на него импульсов с выхода дополнительного выделителя фронтов 7, При переполнении счетчика на сложение бимпульс с его выхода поступает на управляющий вход 9 счет чика на вычитание 5, и производит запись числа, равного усредненному значению фазового рассогласования за цикл накопления, Счетчик на вычитание 5 имеет единственное устойчивое состояние - нулевое.

При записи в него любого числа, отличного о нуля, он автоматически переходит в режим счета на вычитание. Длительность этого режима в периодах импульса высокой частоты равна величине усредненного фазового рассогласования за цикл накопления.

Сигнал такой длительности с выхода счетчика на вычитание 5 поступает на вход делителя 2, переводит делитель 2 в режим управляемое деление.

Сигнал с выхода (k +tti+ i ) -го разряда сумматора 4 поступает на управляющий вход 8 делителя 2 и определяет вид управляемого деления.

Сигнал с выхода счетчика на вычитание 5 одновременно поступает на вход выделителя фронтов 3, с выхода которого сигнал поступает на вход обнуление 10 сумматора 4 и производит обнуление т. е. установку сумматора 4 в исходное состояние для следующего цикла накопления. Фаза выходного сигнала, снимаемого с выхода К-го разряда делителя 2 с точностью до одного импульса высокой частоты осуществляет слежение за усредненной фазой значащих моментов входного сигнала данных.

Усреднение фазы в течение достаточно длительного цикла накопления дает фазу математического ожидания значащего момента слежение за усредненной фазой дает снижение динамической погрещности фазирования и, соответственно, повыщение исправляющей способности устройства фазирования.

Формула изобретения

Устройство для синхронизации двоичных сигналов, содержащее задающий генератор, выход которого подключен к одному из входов делителя, и к другому входу которого подключен вход выделителя фронтов сигнала, отличающееся тем, что, с целью повыщения точности и быстродействия фазирования, введены сумматор, счетчик на вычитание, счетчик на сложение и дополнительный выделитель фронтов, при этом выходы К разрядов делителя подключены к ( k + (ti + ) входам сумматора, выход последнего разряда которого подключен к управляющему входу делителя, а ( k + 4 ) выходы - к соответствующим входам счетчика на вычитание, к управляющему входу которого подключен выход счетчика на сложение, а выход счетчика на вычитание через выделитель фронтов сигнала подключен к входу Обнуление сумматора, управляющий вход которого соединен со входом счетчика на сложение и с выходом дополнительного выделителя фронтов сигнала,

Источники информации, принятые во внимание при экспертизе:

1. Мартынов Е. М, Синхронизация в

системах передачи данных дискретных сообщений, М., Связь, 1972., стр. 130.

2. Авторское свидетельство СССР №403096, М. Кл Н O4L 7/10,1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации двоичных сигналов | 1976 |

|

SU636813A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Устройство фазовой автоподстройки частоты | 1987 |

|

SU1469553A1 |

| Устройство синхронизации с М-последовательностью | 1985 |

|

SU1312750A2 |

| Устройство тактовой синхронизации | 1980 |

|

SU965005A2 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| Устройство синхронизации | 1990 |

|

SU1781835A1 |

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

| Устройство фазовой автоподстройки тактовой частоты | 1989 |

|

SU1721834A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU938419A1 |

Ог

ак

в

ГГИ-1

11 W

Авторы

Даты

1977-01-25—Публикация

1975-09-11—Подача