;(54) УСТРОЙСТВО СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1980 |

|

SU906016A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU978378A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU938419A1 |

| Усредняющее устройство с блокировкой | 1981 |

|

SU978380A1 |

| Устройство фазовой автоподстройки тактовой частоты | 1989 |

|

SU1721834A1 |

| Устройство тактовой синхронизации | 1981 |

|

SU970717A1 |

| Устройство поэлементной синхронизации | 1987 |

|

SU1517142A1 |

| Устройство для синхронизации приемника телеграфных сигналов | 1980 |

|

SU970715A1 |

| Устройство тактовой синхронизации | 1989 |

|

SU1720162A1 |

изобретение относится к передаче дискретной информации и может использоваться для вьщеления тактовой частоты из принимаемого сигнала.

Известно устройство тактовой синхронизации с дискретным управлением, в котором для уменьшения времени вхождения в синфазность используется дополнительный дискриминатор ложной синхронизации с элементами ИЛИ и ключом, а УСТОЙЧИВОСТЬ устройства к помехам достигается применением усред- някщего блока ГИ.

Недостатком данного устройства является то, что процесс выхода из состояния ложной синхронизации в нем может затянуться, вследствие его зависимости от характера принятого сигнала. Это приводит к тому, что фаза выходных тактовых импульсов будет корректироваться в основном дискриминатором ложной синхронизации, что ведет к снижению точности синхрониз ции.

Известно устройство синхронизации, содержащее реверсивный счетчик, блок определения фронтов посылок, выход которого подключен к первым входам основного и дополнительного фаэовьас дискриминаторов, к вторым входам

которых подключен вьлход управляемого генератора, к входам.которого через блоки вычитания и добавления импульсов подключены выходы задающего генератора, при этом выходы основного фазового дискриминатора через блок усреднения подключены к вторым входам блоков вычитания и добавления импульсов 2.

10

Однако в известном устройстве не исключено воздействие сильно смещенных (искаженных помех.ами} импульсов, что ухудшает точность фазирования. Их влияние уменьшается увеличением

15 емкости реверсивного счетчика, приводящее в свою очередь к увеличению времени вхояэдения в синхронизм.

Цель изобретения - повышение точности фазирования и уменьшение вре20мени вхождения в синхронизм.

Для достижения поставленной цели В устройство синхронизации, содержащее реверсивный счетчик, блок определения фронтов посылок, выход ко25 торого подключен к первым входам основного и дополнительного фазовых , дискриминаторов, к вторым входам которых подключен выход управляемого генератора, к входам которого 30 через блоки вычитания и добавления

импульсов подключены выходы задаюего генератора, при этом,выходы основного фазового дискриминатора чеез блок усреднения подключены к вторым входам блоков вычитания и добавления импульсов, введены последо- 5 вательно соединенные счетчик времени блокировки и триггер разрешения счета, а также последовательно соединенные регенератор, блок анализа цикловой синхронизации, пороговый блок Ю и коммутатор, к третьему входу которого, а также к входу счетчика ремени блокировки подключен выход триггера разрешения счета, а выходы оммутатора подключены к третьим 15 входам блоков вычитания и добавления импульсов, при этом выходы дополнительного фазового дискриминатора подключен:. к второму и третьему входам порогового блока, третий и 20 етвертый выходы .которого че1эез реверсивный счетчик подключены к второму входу триггера разрешения счета, причем вЕлход управляемого генератора подключен к первому входу ре- 25 генератора, второй вход которого объединен с входом блока определения фронтов посылок и является входом устройства, выходом которого является выход управляемого генератора.-JQ

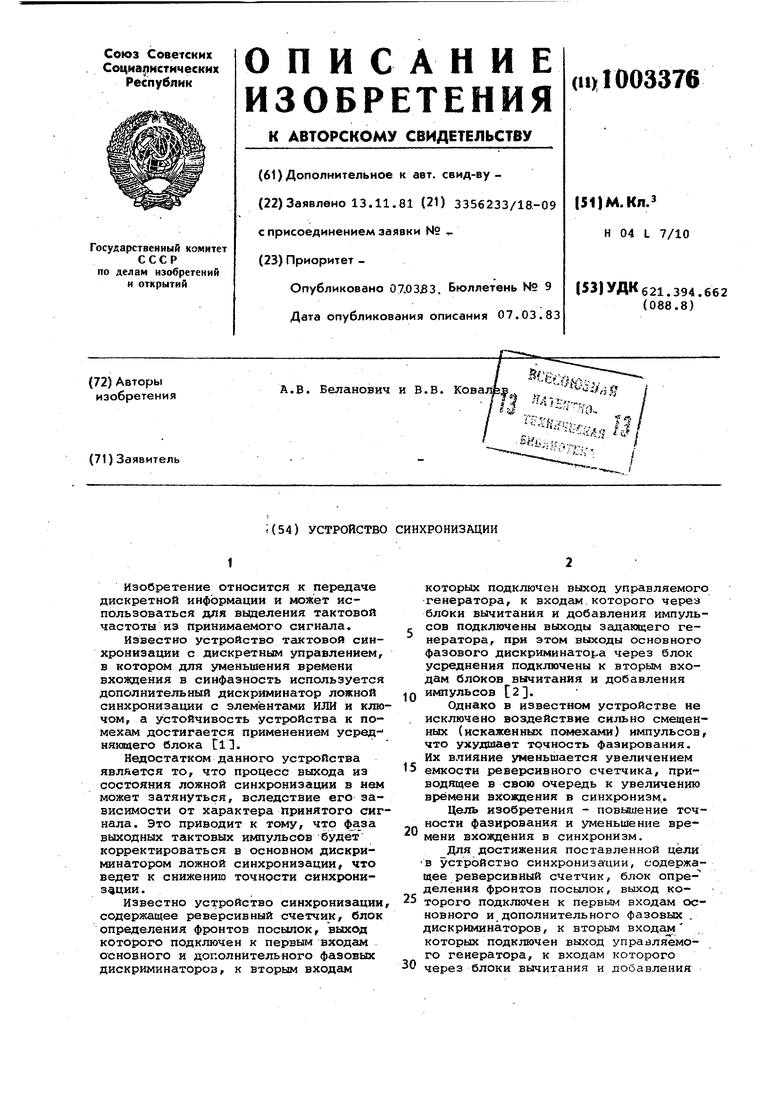

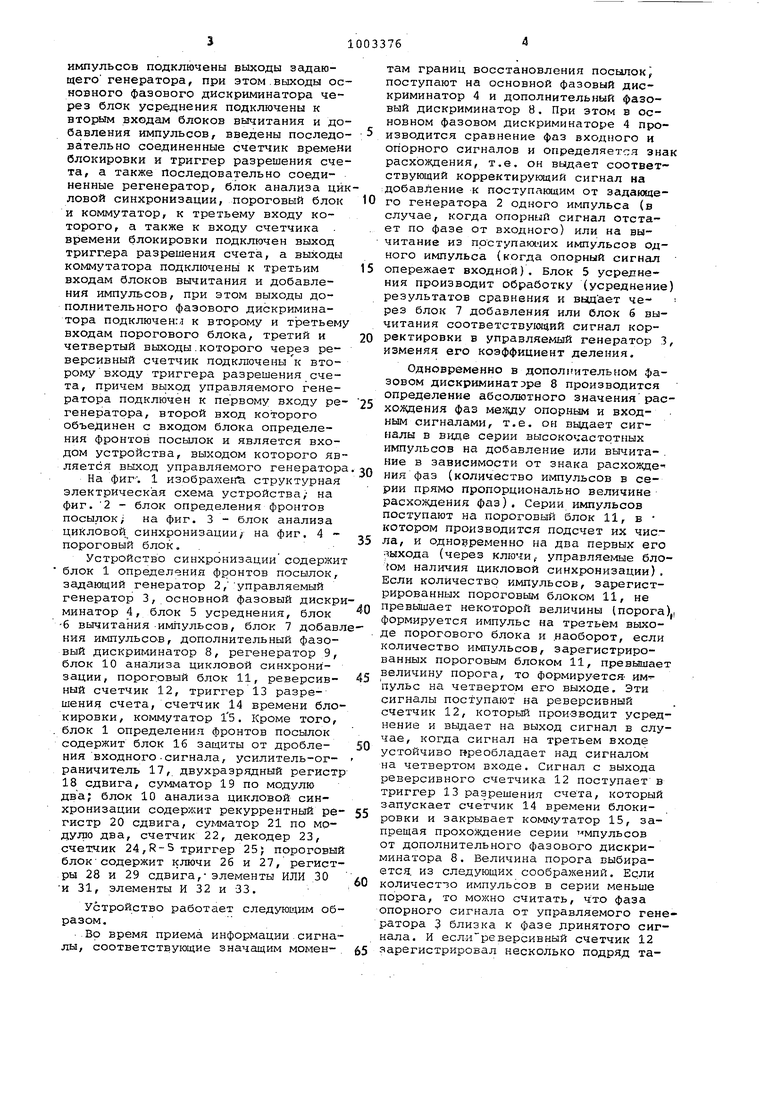

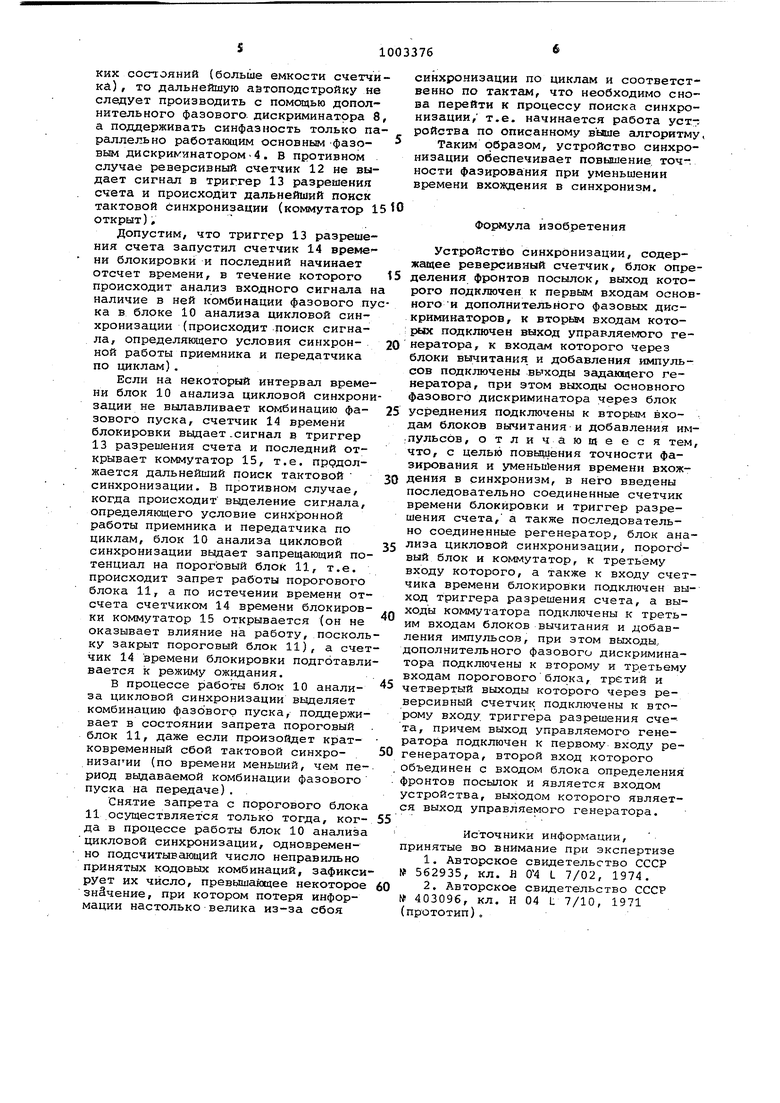

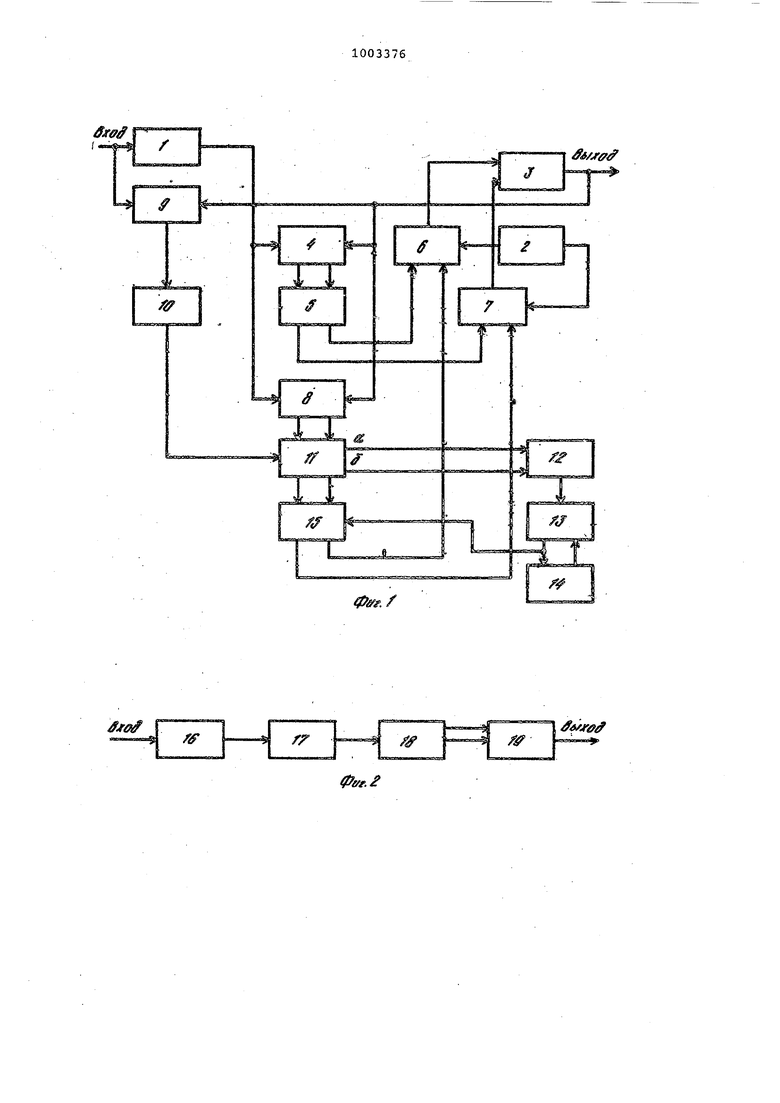

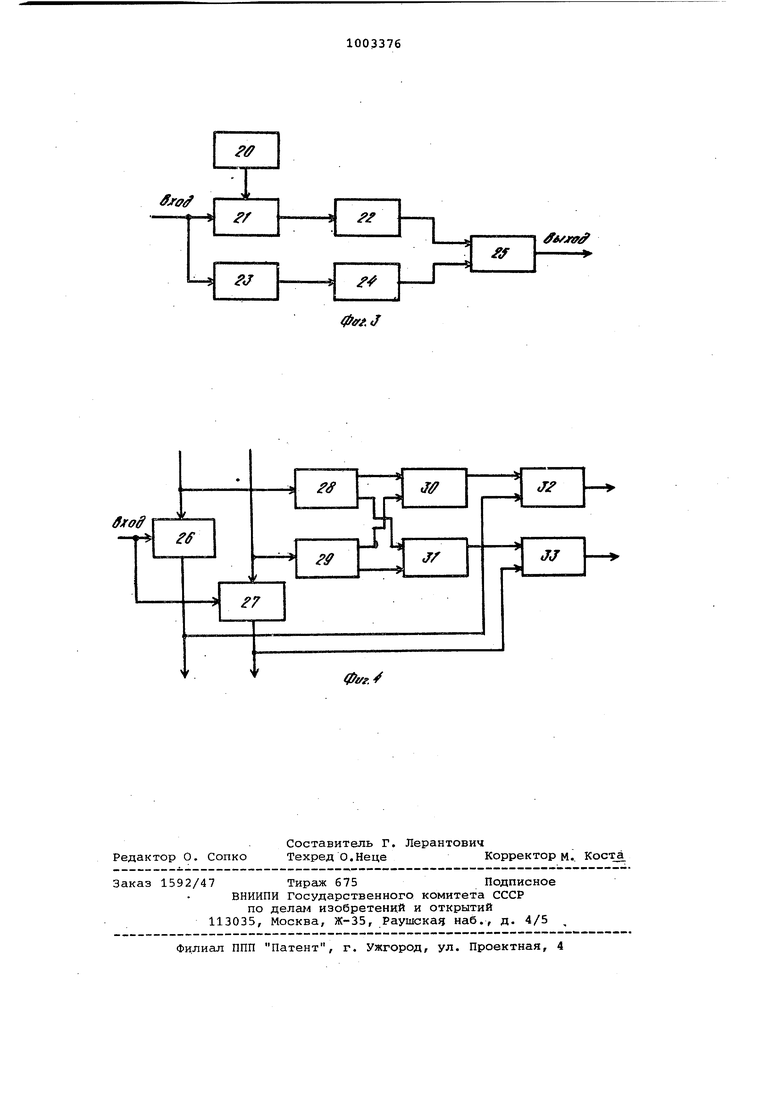

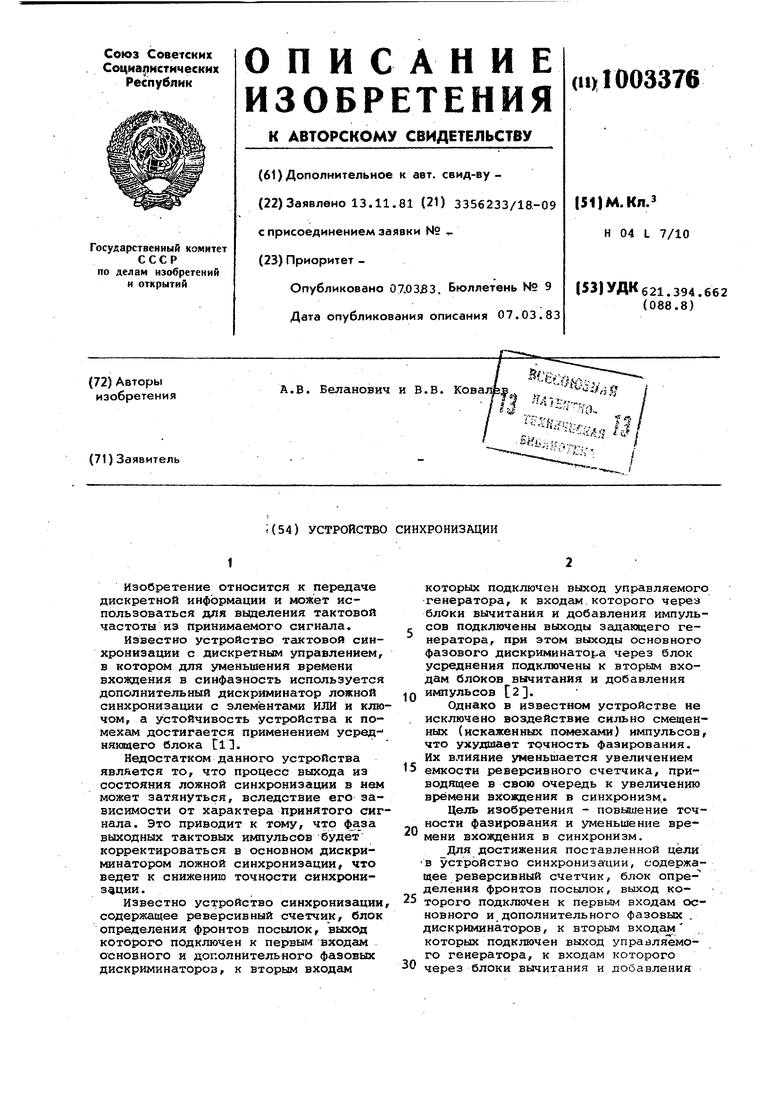

На фиг-; 1 изображен структурная электрическая схема устройства, на фиг. 2 - блок определения фронтов ПОСЫЛОК; на фиг. 3 - блок анализа цикловой синхронизации/ на фиг. 4 эс пороговый блок, .

Устройство синхронизации содержит блок 1 определения фронтов посылок, задающий генератор 2,управляемый генератор 3, основной фазовый дискриминатор 4, блок 5 усреднения, блок 6 вычитания-импульсов, блок 7 добавления импульсо-в, дополнительный фазовый дискриминатор 8, регенератор 9, блок 10 анализа цикловой синхронизации, пороговый блок 11, реверсив- 45 ный счетчик 12, триггер 13 разрешения счета, счетчик 14 времени блокировки, коммутатор Г5. Кроме того, блок 1 определения фронтов посылок содержит блок 16 защиты от дробле- 50 ниявходного-сигнала, усилитель-ограничитель 17, двухразрядный регистр 18 сдвига, сумматор 19 по модулю два; блок 10 анализа цикловой синхронизации содерлсит рекуррентный ре- 55 гистр 20 сдвига, суглматор 21 по модулю два, счетчик 22, декодер 23, счетчик 24,R-5 триггер 25; пороговый блоксодержит ключи 26 и 27, регистры 28 и 29 сдвига, элементы ИЛИ 30 и 31, элементы И 32 и 33.

Устройство работает следующим образом.

-.Во время приема информации.сигналы, соответствующие значащим момен-. 65

там границ восстановления посылок поступают на основной фазовый дискриминатор 4 и дополнительный фазовый дискриминатор 8. При этом в основном фазовом дискриминаторе 4 прюизводится сравнение фаз входного и опорного сигналов и определяется зна расхождения, т.е. он выдает соответствующий корректирукадий сигнал на добавление к поступающим от задающего генератора 2 одного импульса (в случае, когда опорный сигнал отстает по фазе от входного) или на вычитание из прступакхдих импульсов одного импульса (когда опорный сигнал опережает входной). Блок 5 усреднения производит обработку (усреднение результатов сравнения и выдает через блок 7 добавления или блок б вычитания соответствующий сигнал корректировки в управляемый генератор 3 изменяя его коэффициент деления.

Одновременно в дополнительном фазовом дискриминаторе 8 производится определение абсолютного значениярасхоадения фаз меяуду опорным и входным сигналами, т.е. он выдает сигналы в виде серии высок.очастотных импульсов на добавление или вычита-. ние в зависимости от знака расхождения фаз (количество импульсов в серии прямо пропорционально величине расхождения фаз). Серии импульсов поступают на пороговый блок 11, в котором производится подсчет их чис.ла, и одновременно на два первых его выхода (через ключи, управляемые блоЧом наличия цикловой синхронизации), Если количество импульсов, зарегистрированных пороговым блоком 11, не превышает некоторой величины (порога формируется импульс на третьем выходе порогового блока и .наоборот, если количество импульсов, зарегистрированных пороговым блоком 11, превышае величину порога, то формируется импульс на четвертом его выходе. Эти сигналы поступают на реверсивный счетчик 12, который прои-зводит усреднение и выдает на выход сигнал в случае, когда сигнал на третьем входе устойчиво иреобладает над сигналом на четвертом входе. Сигнал с выхода реверсивного счетчика 12 поступает в триггер 13 разрешения счета, который запускает счетчик 14 времени блокировки и закрывает коммутатор 15, запрещая прохождение серии мпульсов от дополнительного фазового дискриминатора 8. Величина порога выбирается, из следующих соображений. ЕСЛИ количество импульсов в серии меньше порога, то можно считать, что фаза опорного сигнала от управляемого генратора 3 близка к фазе принятого сигнала. И если реверсивный счетчик 12 зарегистрировал несколько подряд таних сосггояний (больше емкости счетчи ка) , то дальнейшую айтоподстройку не следует производить с помощью дополнительного фазового дискриминатора 8 а поддерживать синфаэность только па ргшлельно работающим основным -фазовым дискриминатором-4, В противном случае реверсивный счетчик 12 не выдает сигнал в триггер 13 разрешения счета и происходит дальнейший поиск тактовой синхронизации (коммутатор 1 открыт), Допустим, что триггер 13 разрешения счета запустил счетчик 14 време ни блокировки и последний начинает отсчет времени, в течение которого происходит анализ входного сигнала н наличие в ней комбинации фазового пу ка в блоке 10 анализа цикловой синхронизации (происходит поиск сигнала, определяющего условия синхронной работы приемника и передатчика по циклам). Если на некоторый интервал времени блок 10 анализа цикловой синхрони зации не вылавливает комбинацию фазового пуска, счетчик 14 времени блокировки выдает.сигнал в триггер 13 разрешения счета и последний открывает коммутатор 15, т.е. пррдолжается дальнейший поиск тактовой синхронизации. В противном случае, когда происходит вьщеление сигнала, определяющего условие синхронной работы приемника и передатчика по циклам, блок 10 анализа цикловой синхронизации вьщает запрещающий потенциал на пороговый блок 11, т.е. происходит запрет работы порогового блока 11, а по истечении времени отсчета счетчиком 14 времени блокировки коммутатор 15 открывается (он не оказывает влияние на работу, посколь ку закрыт пороговый блок 11), а счет чик 14 времени блокировки подготавли вается к режиму ожидания. В процессе работы блок 10 анализа цикловой синхронизации выделяет комбинацию фазового пуска, поддерживает в состоянии запрета пороговый блок 11, даже если произойдет кратковременный сбой тактовой синхронизагии (по времени меньший, чем период выдаваемой комбинации фазового пуска на передаче). Снятие запрета с порогового блока 11 осуществляется только тогда, когда в процессе работы блок 10 анализа цикловой синхронизации, одновременно подсчитывающий число неправильно принятых кодовых комбинаций, зафикси рует их число, превышайхцее некоторое значение, при котором потеря информации настолько велика из-за сбоя синхронизации по циклам и соответственно по тактам, что необходимо снова перюйти к процессу поиска синхронизации, т.е. начинается работа устг ройства по описанному выше алгоритму, Таким образом, устройство синхронизации обеспечивает повышение, точ-. ности фазирования при уменьшении времени вхождения в синхронизм. Формула изобретения Устройстйо синхронизации, содержащее реверсивный счетчик, блок определения фронтов посылок, выход которого подключен к первым входам основного и дополнительного фазовых дискриминаторов/ к вторьм входам которьк подключен выход управляемого генератора, к входам которого через блоки вычитания и добавления импульсов подключены выходы задающего генератора, при этом выходы основного фазового дискриминатора через блок усреднения подключены к вторым входам блоков вычитания и добавления им: пульсов, отличающееся тем, что, с целью повышения точности фазирования и уменьшения времени вхождения в синхронизм, в него введены последовательно соединенные счетчик времени блокировки и триггер разрешения счета, а также последовательно соединенные регенератор, блок анализа цикловой синхронизации, пороговый блок и коммутатор, к третьему входу которого, а также к входу счетчика времени блокировки подключен выход триггера разрешения счета, а выходы коммутатора подключены к третьим входам блоков вычитания и добавления импульсов, при этом выходы, дополнительного фазового дискриминатора подключены к второму и третьему входам порогового блока, третий и четвертый выходы которого через реверсивный счетчик подключены к второму входу триггера разрешения счета, причем выход управляемого генератора подключен к первому входу регенератора, второй вход которого объединен с входом блока определения фронтов посылок и является входом устройства, выходом которого является выход управляемого генератора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 562935, кл. и 04 L 7/02, 1974. 2.Авторское свидетельство СССР № 403096, кл. Н 04 L 7/10, 1971 (прототип), 0fff.f A/jrffa

SfO/

/2f

JTff

/

г

Т

ffjO f

0ff.J

Й/г/

Авторы

Даты

1983-03-07—Публикация

1981-11-13—Подача