I

1Изобретенйе относится к области вь числитедьной техники и может быть иопользовано в микропрограммных устройствах управления с жесткой логикой, например, в устройствах управления быстродействующих специализированных ЭВМ.

Известно устройство, содержащее блок памяти микропрограмм, соединенный с адресным регистром и регистром микрокоманды, который подключен через дещифратор поля к одним входам блока управления длительностью микропрограммного такта, другие входы которого соединены с выходами секционной линии задержки, вход которой через элемент НЕ подключен к выходу блока управления длительностью микропрограммного такта и ко входу адресного регистра flj.

Недостатком известного устройства является сложность схемы и ограниченные функциональные возможности. Так, во-пе{ вых, на линии задержки практически очень трудно организовать такты переменной длительности, отличающиеся по времени

в 5О-100 раз, BD-вторых, линии задержки на время более 1-2 мкс имеют большие размеры, в третьих, число выходов линии задержки равняется числу микроопераций различной длительности, причем время задержки каждого выхода относительно входа должно равняться максимальному времени выполнения каждой конкрет ной микрокоманды, что препятствует использованию стандартных линий задержки и требует их специального изготовления.

Известно устройство, которое содержит схему анализа типа управляющего слова и управляемый генератор импульсов, выполненный в виде набора генераторов,

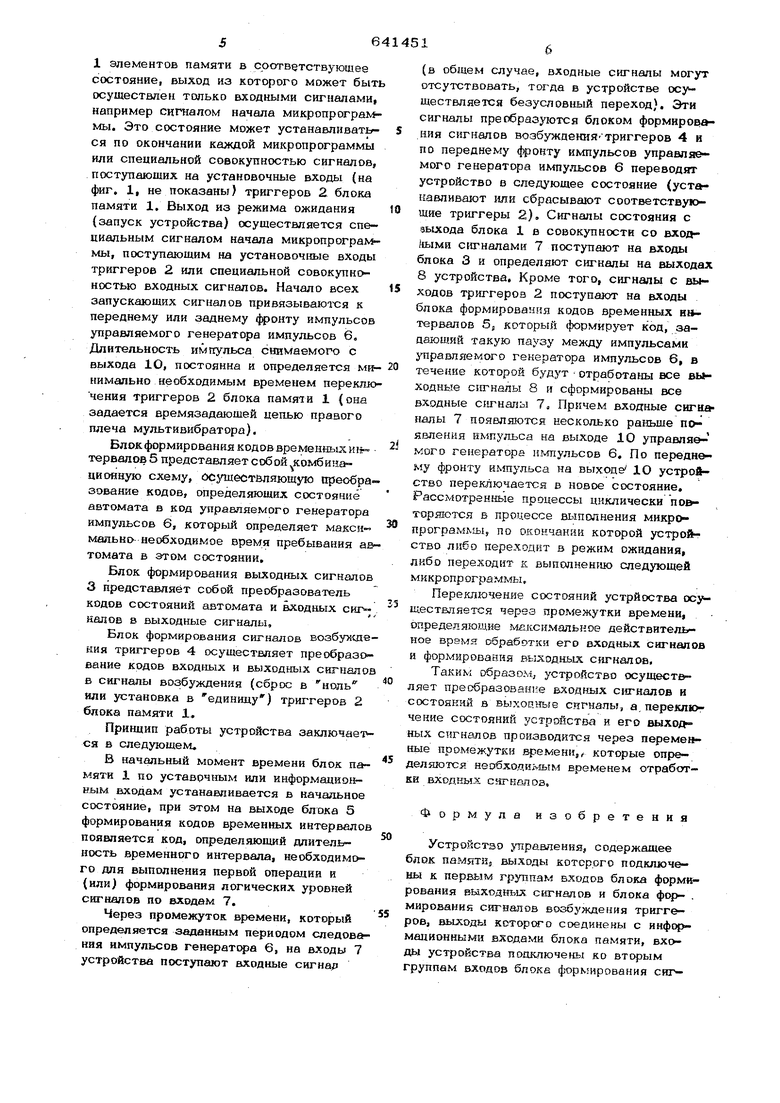

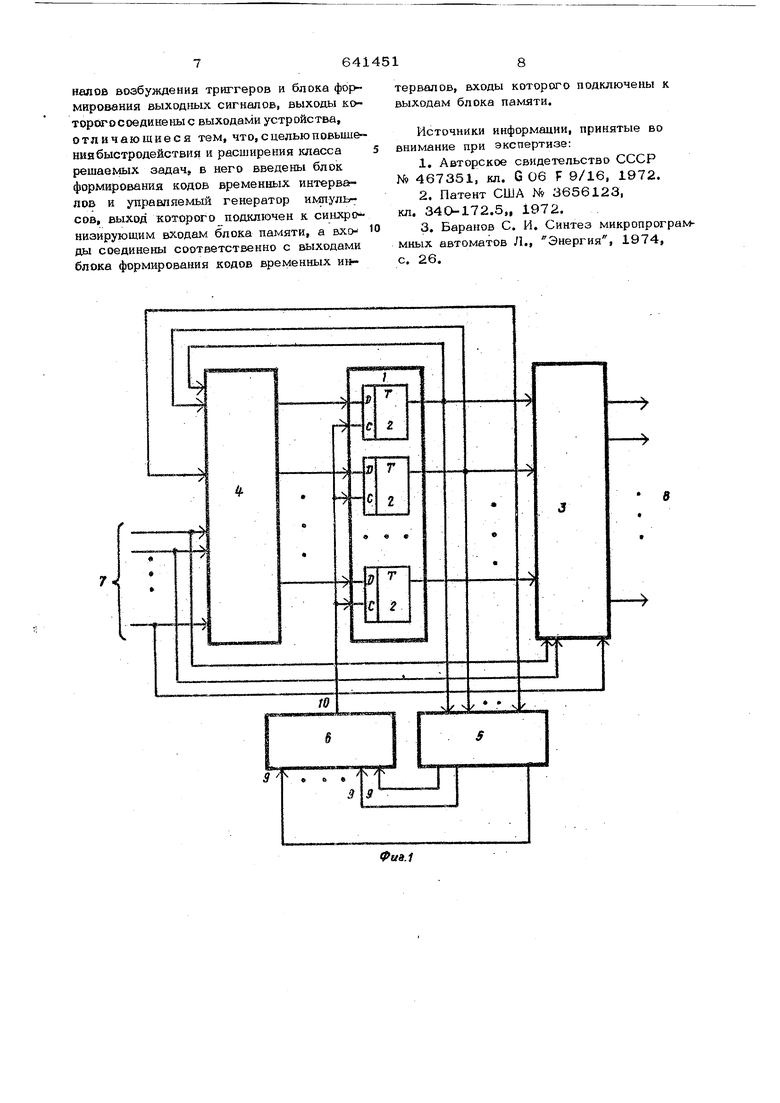

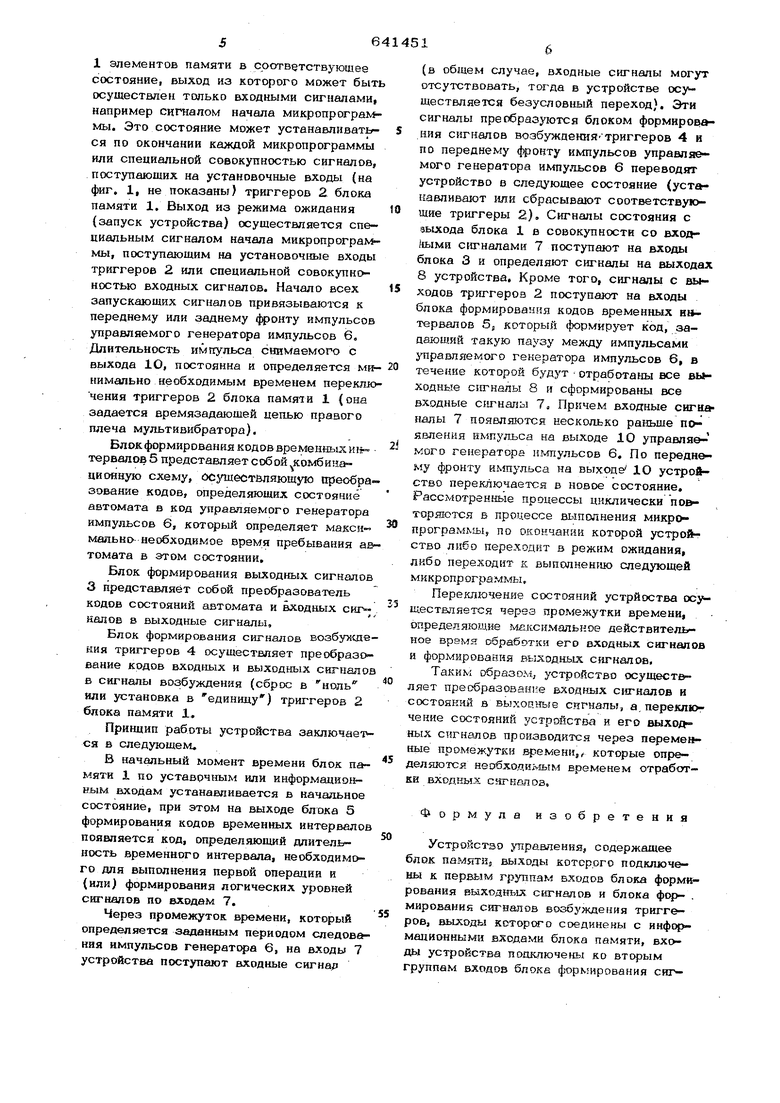

Это устройство обеспечивает переменную длительность машинногю цикла, но не обеспечивает переменной длительнооти .машинного такта (элементарный такт работы машины), т.к. невозможно обеспв чить синхронное переключение набора генераторов в пределах одного тактового сигнала (одного периода следования их импульсов). В рассмотренном устройстве такое переключение осуществляется за половину периода следования импульсов управляема го генератора, При наличии большого количества цик-лов различной длительности изёестное ус-рройство усложняется, Кроме того, в нем необходим синхронизирующий узел для устранения взаимного наложения импульсов генераторов. Из известных устройств наиболее блиэ КИМ по технической сущности к изобретению является устройство, которое содержит блок памяти, выходы которого подклюсены к группам входов блока формирования выходных, сигналов и блока формирования сигналов возбуждения триггеров, выходыкоторого соединены с информационными входами блока памяти, входы устройства подключены ко вторым группам входов блока формирования сигна лов возбуждения триггеров и блока форми рования выходных сигналов выходы которого соединены с выходами устройства Выходные сигналы этого устройства зависят от входных сигналов и от его состояния в данный момент времени. Состояние устройства определяется входными сигналами и состоянием в предыдущий мо меит времени. Переключение состояний устройства и его выходных сигналов осуществляется через постоянный интервал времени, В случае применения его в микропрограммных устройствах управления (при жестком способе построения) время через которое осуществляется переключение состояний, должно Определяться временем выполнения самой длинной операции, которую инициируют выходные сигналы устройства. Разница во времени выпол нения коротких и длинных операций может иметь существенное значение, особенно в том случае, когда выходные сигналы инициируют выполнение, например, электро ных и механических действий. Выбор постоянной длительности такта переключени состояний, который определяется временем выполнения самой длинной операции, значительно снижает быстродействие авто мата и класс решаемь1х им задач. Целью изс ретения является повышение быстродействия и р ;щирение класса решаемых задач. Поставленная цель достигается тем, что в устройство введены блок формирования кодов временных интервалов и управляемый генератор импульсов, выход котоого подключен к синхронизирующему вхоу блока памяти, а входы соединены соответственно с выходом блока формирования кодов временных интервалов, входы которого подключены к выходам блока амяти. На фиг. 1 изображена структурная хема устройства; на фиг. 2 - один из вариантов схемы управляемого генератора, импульсов. Устройство содержит: блок памяти 1, выполненный, например, на D -триггерах 2, выходы которого подключены ко входам блока формирования выходных сигналов 3, блока формирования сигналов возбуждения триггеров 4 и блока формирования кодов временных интервалов 5, Выходы блока формирования кодов временных интервалов 5 подключен ко входам управляемого генератора импульсов 6, выход которого подключен к синхронизирующим входам блока памяти 1, И«формационные входы блока 1 памяти { 3) входы D - триггеров 2) подключены к выходам блока формирования сигналов возбуждения триггеров 4. Входы 7 устройства подсоединены к блоку формирования сигналов возбуждения триггеров 4 и ко входам блока формирования выходных сигналов 3, выходы 8 устройства подключены к блоку формирования выход й1Х сигналов 3, Управляемый генератор импульсов 6 может быть выполнен, например, на базе управляемого мультивибратора, схема которого, приведенная HJ фиг, 2, содержит входы 9,, выход 1О, ксялекторные резисторы 11, базовые времяяадаюшие резистоды 12, времязадающие конденсаторы левого плеча мультивибратора 13, времязадак щий конденсатор правсго плеча мультиви&ратора 14, транзисторы 15, зарядные диоды 16, разряд,ные диоды 17, Принцип его работы заключается в наменешк паузы между импульсами, снимаемыми с выхода Юс помощью изменения парамет ров времязадающей цепи левого 1шеча мультивибратора путем коммутации времязадающих конденсаторов 13 по входам И, Разряд конденсаторов 13 происходит через разрядные диоды 17, Время разряда определяет длительность паузы между импульсами на выходе 1О, В режиме ожиданий на всех вЬ1ходах блока 5 формирования кодов временных интервалов устанавливаются сигналы, соответствующие максимальной частоте работы управляемого генератора 6 импульсов, это осуществляется путем установки. т эиггеров 2 блока

1 элементов памяти в соответствующее состояние, выход из которого может быть осуществлен только входными сигналами, например сигналом начала микропрограммы. Это состояние может устанавливатьгся по окончании каждой микропрограммы или специальной совокупностью сигналов, поступающих на установочные входы {на фиг, 1, не показаны) триггеров 2 блока памяти 1. Выход из режима ожидания (запуск устройства) осуществляется специальным сигналом начала микропрограммы, поступающим на установоч1а.1е входы триггеров 2 или специальной совокупноностью входных сигналов. Начало всех запускающих сигналов привязываюачзя к переднему или заднему импульсов управляемого генератора импульсов 6, Длительность импульса снимаемого с выхода 1О, постоянна и определяется MFTнимально необходимым временем переключения триггеров 2 блока памяти 1 {она задается времязадаюшей цепью правого плеча мультивибратора).

Блок, формирования кодоввременных И1 тервал ОБ 5 представляет с об ой комб инационную схему, осушестытяющую преобразование кодов, определяющих состояние автомата в код управляемого генератора импульсов 6, который определяет максимально необходимое время пребывания автомата в этом состоянии.

Блок формирования выходных сигналов 3 представляет собой преобразователь кодов состояний автомата и входных сипкалов в выходные сигналы.

Блок формирования сигналов Бозбукшения триггеров 4 осуществляет преобразование кодов входных и выходных сигналов в сигналы возбуждения {сброс в ноль или установка в единицу) триггеров 2 блока памяти 1.

Принцип работы устройства заключается в следующем

В начальный момент времени блок памяти 1 по уставочным или информационным входам устанавливается в начальное состояние, при этом на выходе блока 5 формирования кодов временных интервалов появляется код, определяющий длительность временного интервала, необходимого для выполнения первой операции и {или) формирования логических уровней сигналов по входам 7.

Через промежуток времени, который определяется заданным периодом следования импульсов генератора 6, на входы 7 устройства поступают входные сигна/j

{в общем случае, входные сигналы могут отсутствовать, тогда в устройстве осу шествляется безусловный переход). Эти сигналы преобразуются блоком формирования сигналов возбуждениятриггеров 4 и по переднему (|ронту импульсов управляемого генератора илтульсов 6 переводят устройство в следующее состояние (устанавливают или сбрасывают соответствующие триггеры 2), Сигналы состояния с зыхода блока 1 в совокупности со входIttiMH сигналами 7 поступают на входы блока 3 и определяют сигналы на выходах 8 устройства. Кроме того, сигналы с выходов триггеров 2 поступают на входы блока формированЕ я кодов временных и тервалов 5, который формирует код, задающий такую паузу мелсду импульсами управляемого генератора импульсов 6, в течекне которой будут отработаны все выходные сигналы 8 н сформированы все входные сигнаг;ы 1, Причем входные сигнаналы 7 появляются несколько раныде появления импульса на выходе 10 управляеммого генератора И1 тульсов 6, По переднему фронту импуяьса на выходе Ю устройство переключается в новое состояние, Рассмотрен Ые процессы циклически повторяются в процессе выпа1нения микропрограммы, по окончании которой устройнство либо переходит в режим ожидания, либо переходит к выполнению следующей микропрограммы.

Переключение состояний устрйоства осущестБляетхгя через промежутки времени, определяющие .максимальное действительное врзмя обработки его входных сигналов и формирования выход й.1х Сигналов,

Таким образом, устройство осуществляет преобразование входных сигналов и состояний в выхопные сигналы, а, переклюг чение состояний устройства и его выхо/: ных сигналов производится через переменные промежутки времени, которые определяются необходи; 1ым временем отработки входных сигнал OS,

Формула изобретения

Устройство ртравпенняг содержащее блок па.мятй. выходы которого подключены к первым группам входов блока формирования выходных сигналов и блока фор- . мировання сигналов возбуждения триггеров, выходы которого соединены с инфс)мационными входами блока памяти, вхсиды устройства подключены ко вторым группам входов блока форынрования сиг-

налов возбуждения триггеров и блока формирования выходных сигналов, выходы которсмгосоединеныс выходами устройства, отличающиеся тем, что, с целью повышения быстродействия и расширения класса решаемых задач в него введены блок формирования кодов временных интервалов и управляемый генератор икшуль сов, выход которого подключен к. синхро низирующим входам блока памяти, а входы соединены соответственно с выходами блока формирования кодов временных и тервалов, входы которого подключены к выходам блока памяти.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР N9 467351, кл. G 06 F 9/16, 1972.

2.Патент США № 3656123, кл. 34О-172.5,, 1972.

3.Баранов С. И. Синтез микропрограмных автоматов Л., Энергия, 1974,

с. 26.

ff

/3

14

Ч

17

fZ

/4фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1976 |

|

SU616629A1 |

| Устройство для отображения информации | 1978 |

|

SU746629A1 |

| Устройство для отображения информации | 1979 |

|

SU868822A2 |

| Устройство для отображения информации | 1985 |

|

SU1316028A2 |

| Многоканальный микропрограммный счетчик | 1985 |

|

SU1280598A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Микропрограммное устройство управления | 1980 |

|

SU955058A1 |

| Устройство для моделирования алгоритма деятельности человека-оператора | 1989 |

|

SU1621042A1 |

| Устройство микропрограммного управления | 1989 |

|

SU1786486A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1005170A1 |

Авторы

Даты

1979-01-05—Публикация

1976-07-12—Подача