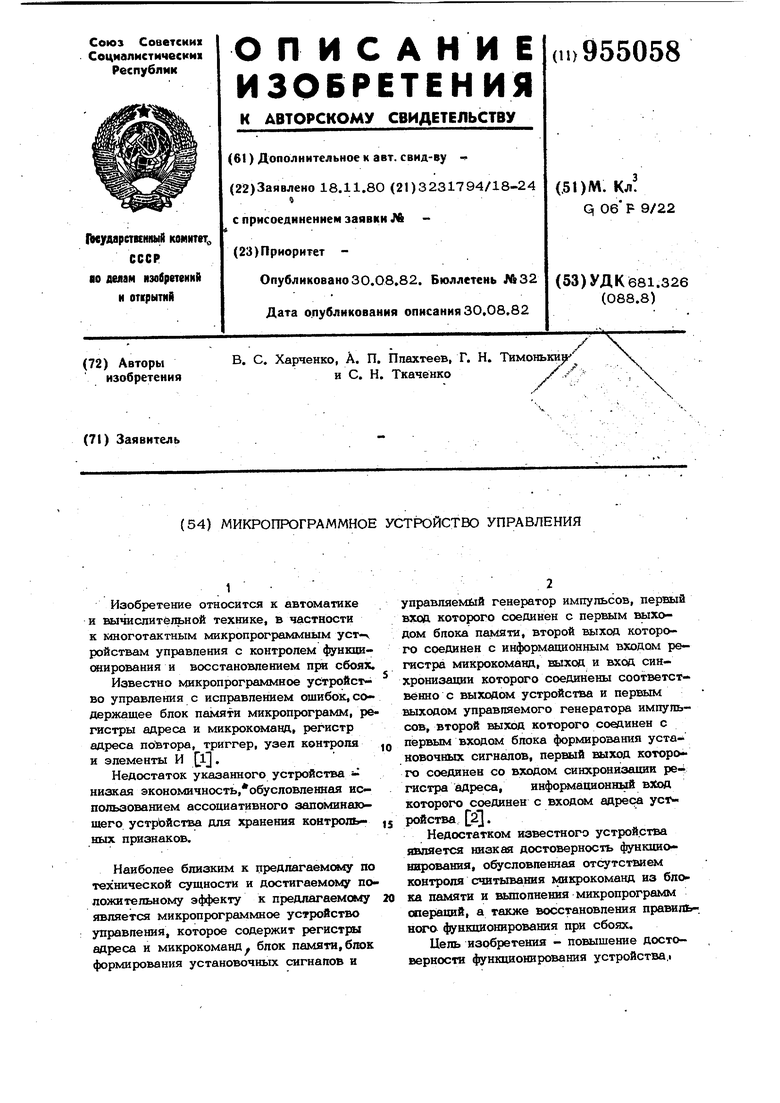

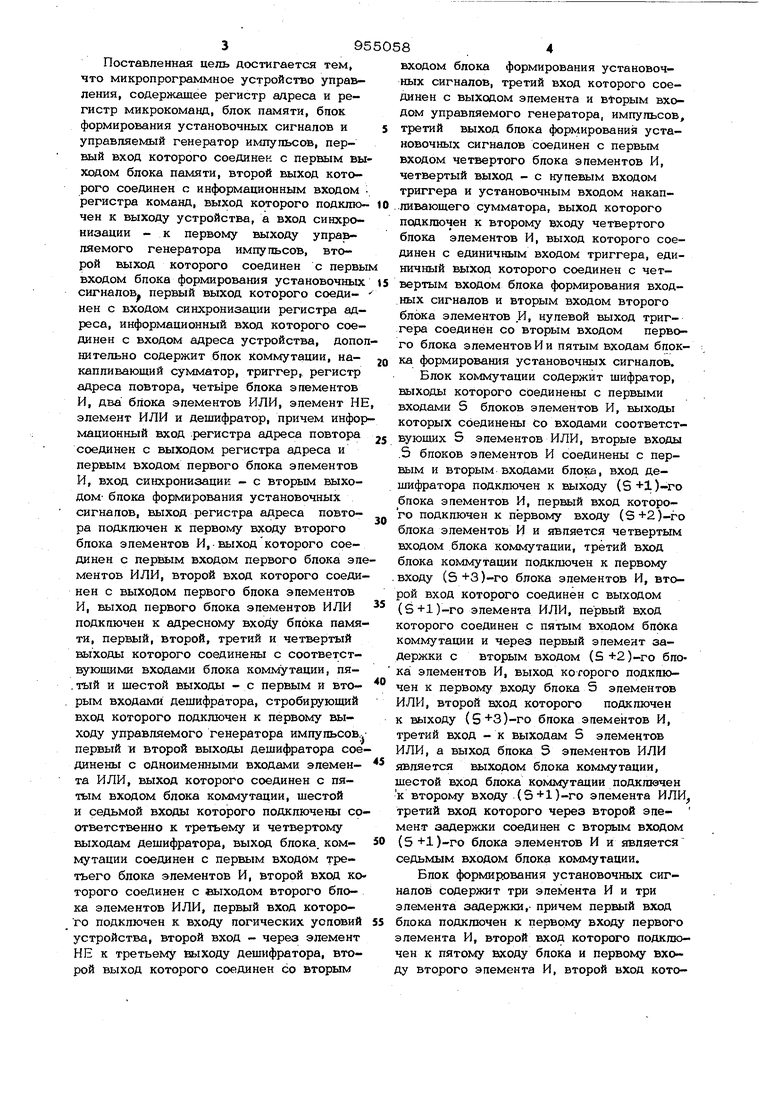

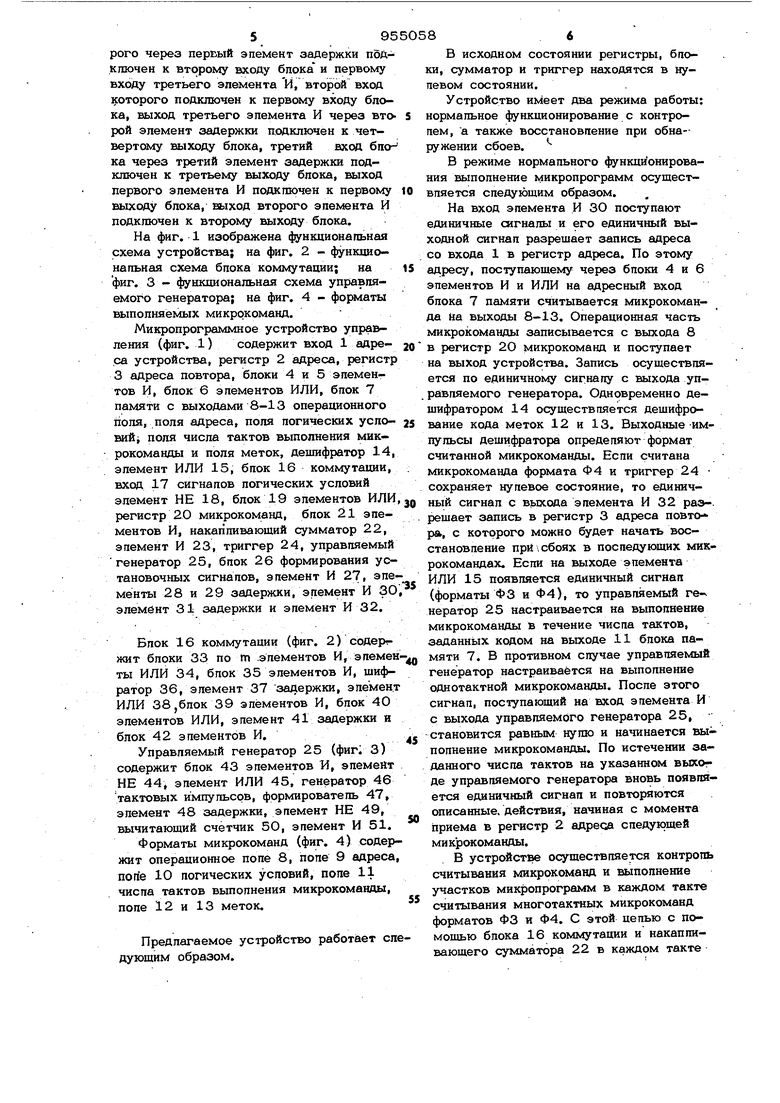

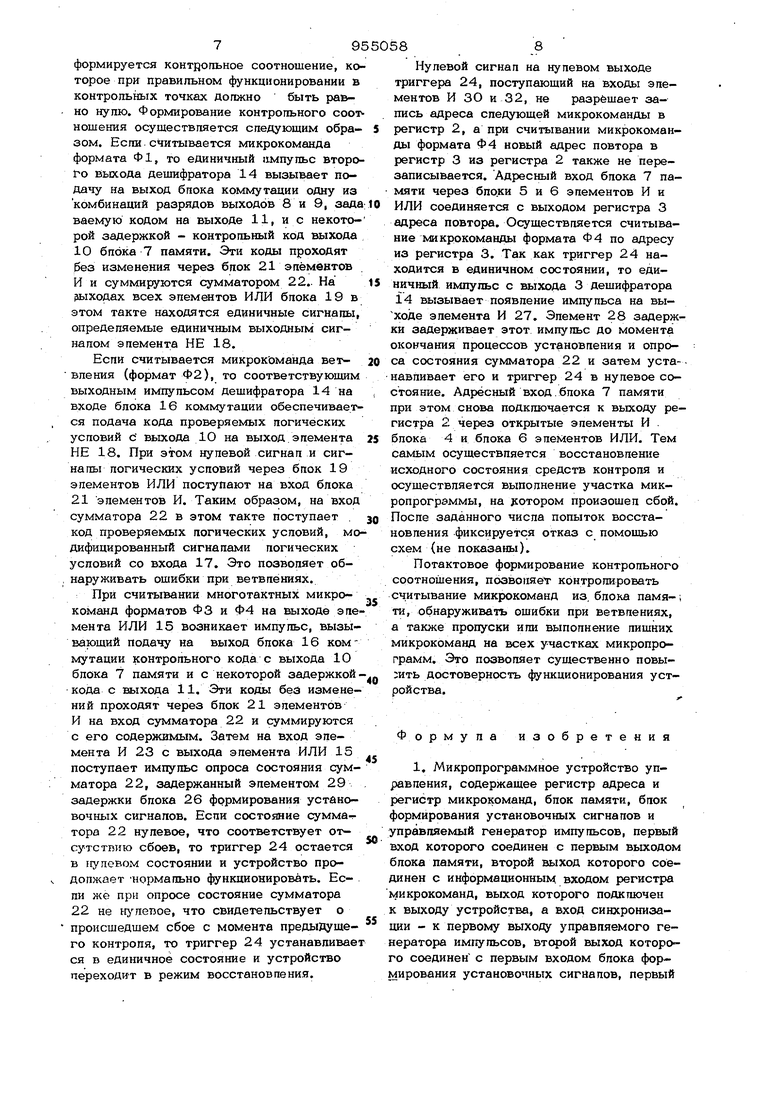

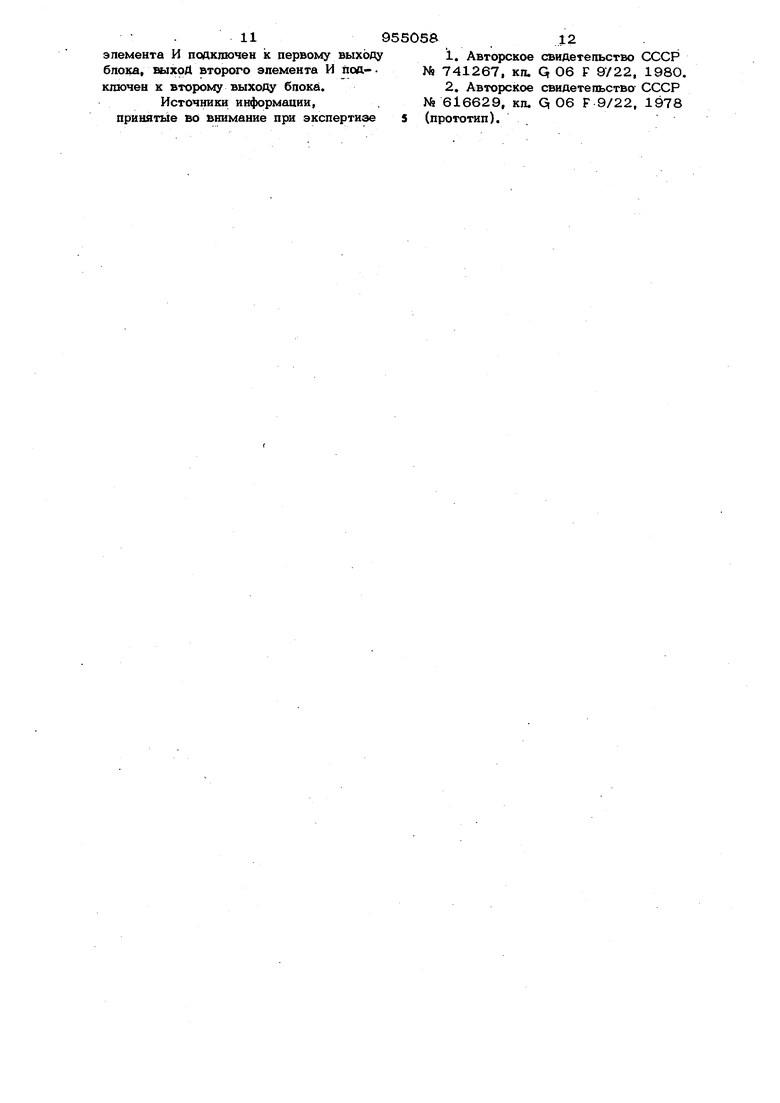

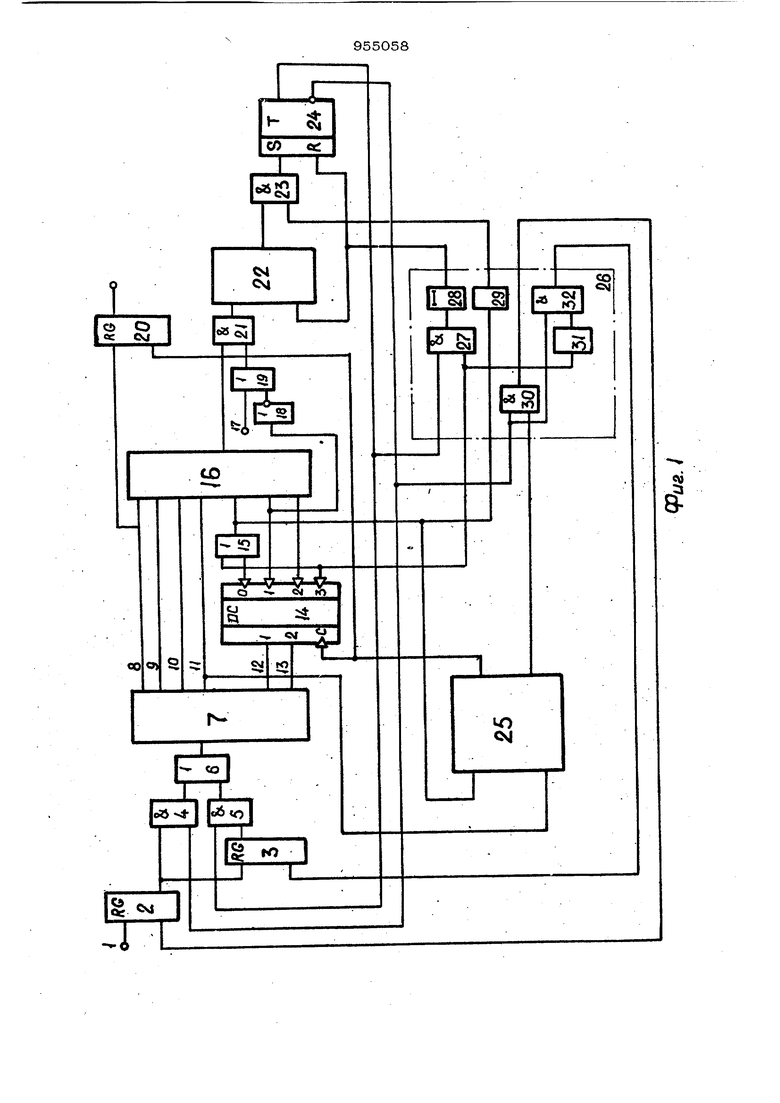

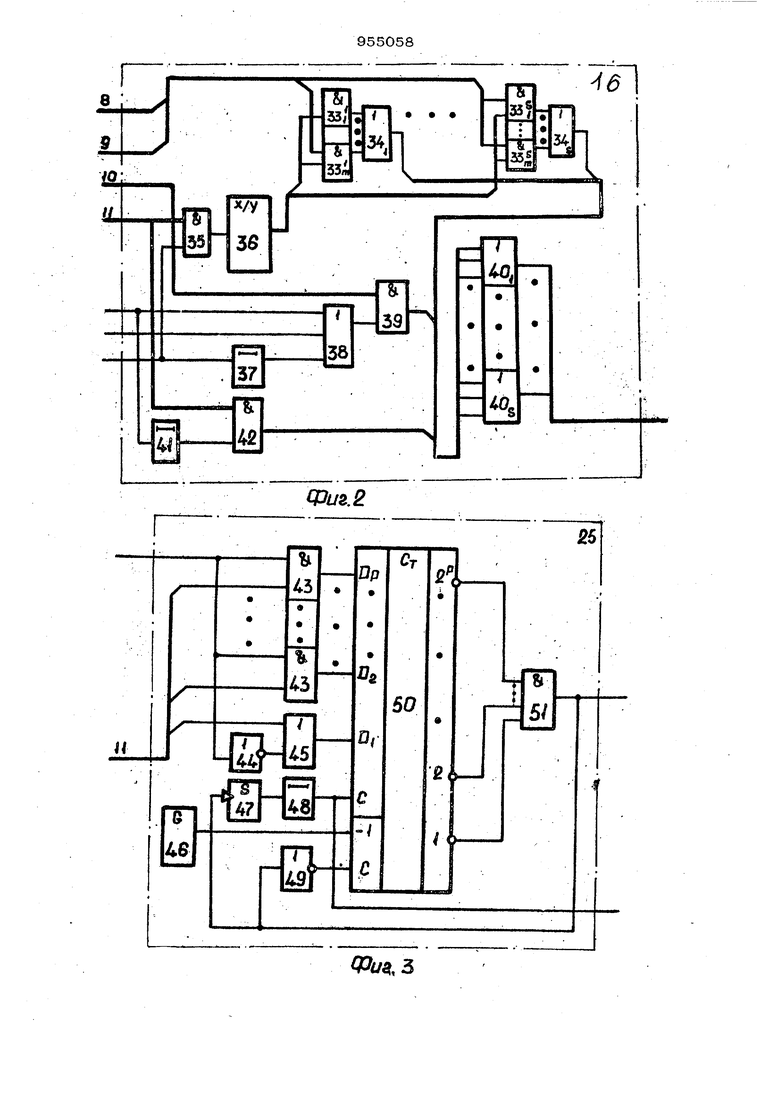

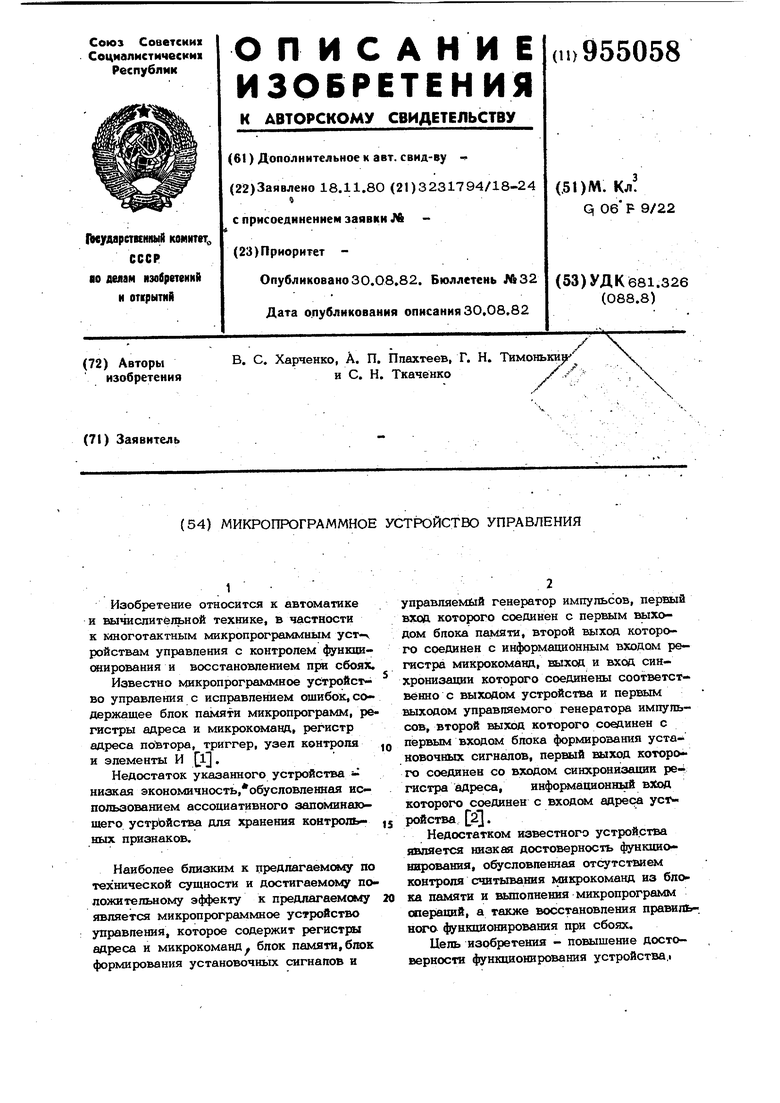

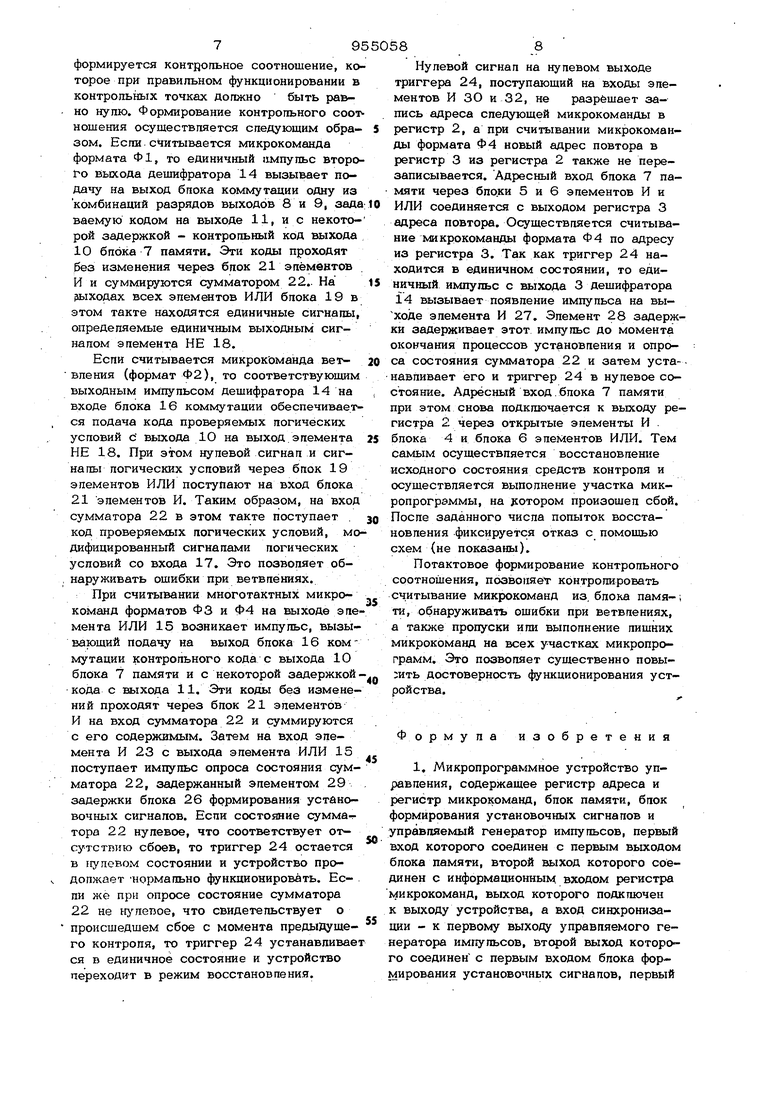

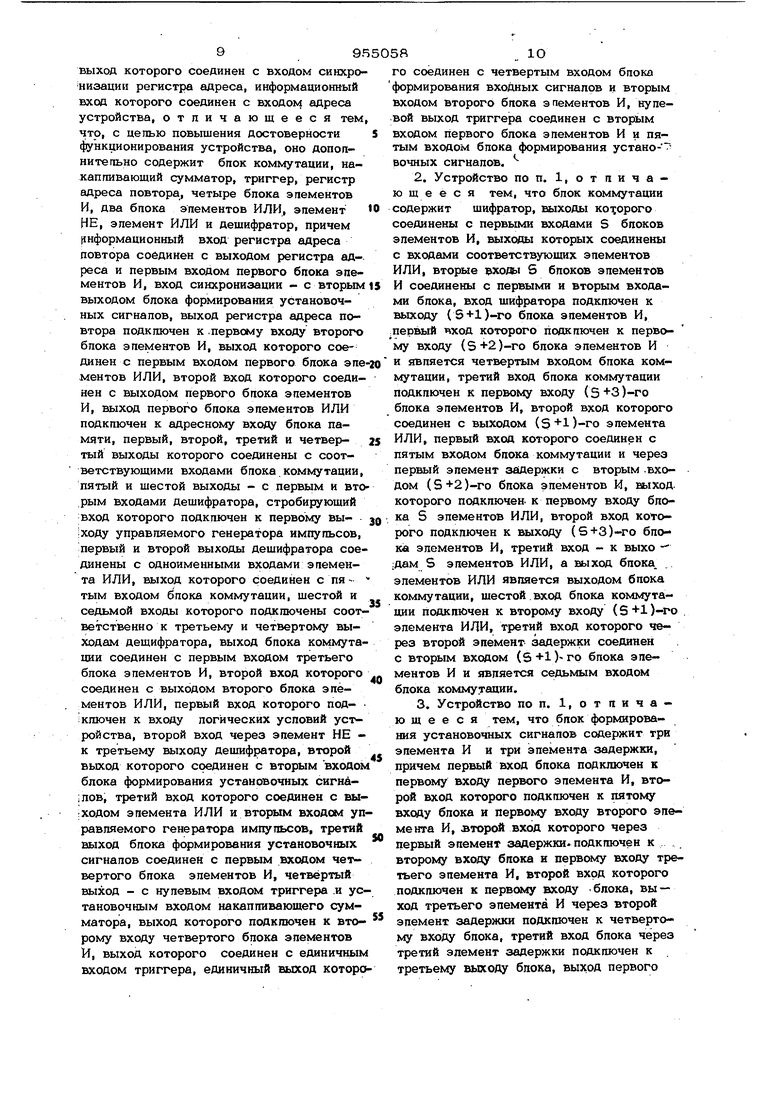

1 Изобретение относится к автоматике и вычислительной технике, в частности к многотактным микропрограммным уст-г ройствам управления с контролем « ункцисширования и восстановлением при сбоях. Известно микропрограммное устройство управления с исправлением ошибок, содержащее блок памяти микропрограмм, ре гистры адреса и микрокоманд, регистр адреса повтора, триггер, узел контроля и элементы И l. Недостаток указанного устройства низкая экономичность, обусловленная использованием ассоциативного запомина1ошего устрЬйства для хранения контрольных признаков. Наиболее близким к преппйгаемому по технической сущности и достигаемому положительному эффекту к предлагаемому является микропрограммное устройство управпения, которое содержит регистры адреса и микрокоманд блок памяти,блок формирования установочных сигналов и управляемый генератор импульсов, первый вход которого соединен с первым исходом блока памяти, второй выход которого соединен с информационным входом регистра микрокоманд, выход и вход синхронизации которого соединены соответственно с выходом устройства и первым выходом управпяемого генератора импульсов, второй выход которого соединен с первым входом блока формирования установочных сигналов, первый выход которого соединен со входом синхронизации ре4 гистра адреса, информационный вход которого соединен с входом адреса устройства 2Q. Недостатком известного устройства является низкая достоверность функционирования, обусловленная отсутствием контроля считывания микрокоманд из бло на памяти и выполнения микропрограмм операций, а также восстановления правиль-. кого функционирования при сбоях. Цель изобретения - повышение достоверности функционирования устройства.1 Поставпенная цель достигается тем, что микропрограммное устройство управления, содержащее регистр адреса и регистр микрокоманд, блок памяти, блок формирования установочных сигналов и управляемый генератор ил-шульсов, первый вход которого соединен с первым вы ходом блока памяти, второй выход которого соединен с информационным входом регистра команд, выход ксторого подключен к выходу устройства, а вход синхронизации - к первому выходу управляемого генератора импульсов, второй выход которого соединен с первы входом блока формирования установочных сигналов, первый выход которого соединен с входом синхронизации регистра адреса, информационный вход которого соединен с входом адреса устройства, допо нительно содержит блок коммутации, накапливающий сумматор, триггер, регистр адреса повтора, четыре блока элементов И, два блока элементов ИЛИ, элемент НЕ элемент ИЛИ и дешифратор, причем инфор мационный вход .регистра адреса повтора соединен с выходом регистра адреса и первым входом первого блока элементов И, вход синхронизации - с вторым выходом- блока формирования установочных сигналов, выход регистра адреса повтора подключен к первому входу второго блока элементов И, выход которого соединен с первым входом первого блока эл ментов ИЛИ, второй вход которого соеди нен с выходом первого блока элементов И, выход первого блока элементов ИЛИ подключен к адресному входу блока памя ти, первый, второй, третий и четвертый выходы которого соединены с соответствующими входами блока коммутации, пя.тый и шестой выходы - с первым и вторым входами дешифратора, стробирующий вход которого подключен к первому выходу управляемого генератора импупьсов.у первый и второй выходы дешифратора сое динены с одноименными входами элемента ИЛИ, выход которого соединен с пятым входом блока коммутации, шестой и седьмой входы которого подключены со ответственно к третьему и четвертому выходам дешифратора, выход блока, коммутации соединен с первым входом третьего блока элементов И, второй вход ко торого соединен с выходом второго блока элементов ИЛИ, первый вход которого подключен к входу логических условий устройства, второй вход - через элемент НЕ к третьему выходу дешифратора, второй выход которого соединен со вторым входом блока формирования установочных сигналов, третий вход которого соединен с выходом элемента и входом управляемого генератора, импульсов, третий выход блока формирования установочных сигналов соединен с первым входом четвертого блока элементов И, четвертый выход - с нулевым входом триггера и установочным входом накап.ливающего сумматора, выход которого подключен к второму входу четвертого блока элементов И, выход которого соединен с единичным входом триггера, единичный выход которого соединен с четвертым входом блока формирования входных сигналов и вторым входом второго блока элементов И, нулевой выход триггера соединен со вторым входом первого блока элементов И и пятым входам бпокка формирования установочных сигналов. Блок коммутации содержит шифратор, выходы которого соединены с первыми входами S блоков элементов И, выходы которых соединены со входами соответствующих 5 элементов ИЛИ, вторые входы .5 блоков элементов И соединены с первым и вторым входами блока, вход дешифратора подключен к выходу {S+l)-ro блока элементов И, первый вход которого подключен к первому входу (S+2)-ro блока элементов И и является четвертым входом блока коммутации, третий вход блока коммутации подключен к первому входу (5+3)-го блока элементов И, второй вход которого соединен с выходом (S+1 )-го элемента ИЛИ, первый вход которого соединен с пятым входом блбка коммутации и через первый элемент задержки с вторым входом (5+2)-го блока элементов И, выход которого подключен к первому входу блока 5 элементов ИЛИ, второй вход которого подключен к выходу (53)-го блока элементов И, третий вход - к выходам S элементов ИЛИ, а выход блока 5 элементов ИЛИ является выходом блока коммутации, шестой вход блока коммутации подключен к второму входу (S+l)-ro элемента ИЛИ третий вход которого через второй элемент задержки соединен с вторым входом (5 +1)-го блока элементов И и 51вляется седьмым входом блока коммутации. Блок формирования установочных сигналой содержит три элемента И и три элемента задержки,- причем первый вход блока подключен к первому ъхору первого элемента И, второй вход которого подключен к пятому входу блока и первому входу второго элемента И, второй вход которого через первый эпемент задержки подключен к второму входу блока и первому входу третьего элемента И, вто)рой вход которого подключен к первому входу блока, выход третьего элемента И через второй эпемент задержки подключен к четвертому выходу блока, третий вход бпсн ка через третий элемент задержки подключен к третьему выходу блока, выход первого элемента И подключен к первому выходу блока, выход второго элемента И подключен к второму выходу блока. На фиг. 1 изображена функциональная схема устройства; на фиг. 2 - функциональная схема блока коммутации; на фиг. 3 - функциональная схема управляемого генератора; на фиг. 4 - форллаты выполняемых микрокоманд. Микропрограммное устройство упра&ления (фиг. 1) содержит вход 1 адре,са устройства, регистр 2 адреса, регистр 3 адреса повтора, блоки 4 и 5 элементов И, блок 6 элементов ИЛИ, блок 7 памяти с выходами 8-13 операционного поля, поля адреса, поля логических уеловий, поля числа тактов выполнения микрокоманды и поля меток, дешифратор 14, элемент ИЛИ 15, блок 16 коммутации, вход 17 сигналов логических условий элемент НЕ 18, блок 19 элементов ИЛИ, регистр 20 микрокоманд, блок 21 элементов И, накапливающий сумматор 22, элемент И 23, триггер 24, управляемый генератор 25, блок 26 формирования установочных сигналов, элемент И 27, эпементы 28 и 29 задержки, элемент И 30, элемент 31 задержки и элемент И 32. Блок 16 коммутации (фиг. 2) содергжкт блоки 33 по m .элементов И, элементы ИЛИ 34, блок 35 элементов И, шифратор 36, элемент 37 задержки, элемент ИЛИ 38,блок 39 элементов И, блок 40 элементов ИЛИ, элемент 41 задержки и блок 42 элементов И. Управляемый генератор 25 (фиг; 3) содержит блок 43 элементов И, элемейт НЕ 44, элемент ИЛИ 45, генератор 46 тактовых импульсов, формирователь 47, элемент 48 задержки, элемент НЕ 49, вычитающий счетчик 50, элемент И 51. Форматы микрокоманд (фиг. 4) содержит операционное поле 8, поле 9 адреса попе 10 логических условий, попе 11 числа тактов выполнения микрокоманды, поле 12 и 13 меток. Предлагаемое устройство работает сл дующим образом. В исходном состоянии регистры, блоки, сумматор и триггер находятся в нулевом состоянии. Устройство имеет два режима работы: нормальное функционирование с контролем, а также восстановление при обнаружении сбоев. В режиме нормального функционирования выполнение микропрограмм осуществляется следующим образом, На вход элемента И ЗО поступают единичные сигналы и его единичный выходной сигнал разрешает запись адреса со входа 1 в регистр адреса. По этому адресу, поступающему через блоки 4 и 6 элементов И и ИЛИ на адресный вход блока 7 памяти считывается микрокоманда на выходы 8-13. Операционная часть микрокоманды записывается с выхода 8 в регистр 20 микрокоманд и поступает „а выход устройства. Запись осуществля я по единичному сигналу с выхода управляемого генератора. Одновременно дешифратором 14 осуществляется дешифрование кода меток 12 и 13. Выходные импульсы дешифратора определяют формат считанной микрокоманды. Если считана микрокоманда формата Ф4 и триггер 24 сохраняет нулевое состояние, то единич„ый сигнал с вьпсода элемента И 32 раз-, решает запись в регистр 3 адреса повторл, с которого можно будет начать восстановление при сбоях в последующих микрокомандах. Если на выходе элемента ИЛИ 15 появляется единичный сигнал ,, ,.и.,..„.„ мп..„...«.„ „. „.. (форматы ФЗ и Ф4), то управляемый ге- нератор 25 настраивается на выполнение микрокоманды в течение числа тактов. заданных кодом на выходе 11 блока памяти 7. В противном случае управляемый генератор настраивается на выполнение однотактной микрокоманды. После этого сигнал, поступающий на вход элемента И с выхода управляемого генератора 25, становится равным нулю и начинается выполнение микрокоманды. По истечении заданного числа тактов на указанном выхог де управляемого генератора вновь появляется единичный сигнал и повторяются описанные, действия, начиная с момента приема в регистр 2 адреса следующей микрокоманды. В устройстве осуществляется контроль считывания микрокоманд и выполнение участков микропрограмм в каждом такте считывания многотактных микрокоманд форматов ФЗ и Ф4. С этой целью с помошью блока 16 коммутации и накапливающего сумматора 22 в каждом такте

формируется KoHTjjoribHoe соотношение, которое при правильном функционировании в контрольных точках должно быть равно нулю. Формирование контрольного соот ношения осуществляется следующим образом. Если считывается микрокоманда формата Ф1, то единичный 1мпушьс второго выхода дешифратора 14 вызывает подачу на выход блока коммутации одну из комбинаций разрядов выходов 8 и 9, зада ваемую кодом на выходе 11, и с некоторой задержкой - контрольный код выхода 1О блока 7 памяти. Эти коды проходят без изменения через блок 21 элементов И и суммируются сумматором 22.. На ЭЬ1Ходах всех элементов ИЛИ блока 19 в этом такте находятся единичные сигналы, определяемые единичным выходным сигналом элемента НЕ 18.

Если считывается микрокоманда ветвления (формат Ф2), то соответствующим выходным импульсом дешифратора 14 на входе блока 16 коммутации обеспечивается подача кода проверяемых логических условий с выхода 10 на выход. элемента НЕ 18. При этом нулевой сигнал и сигналы логических условий через блок 19 элементов ИЛИ поступают на вход блока

21элементов И. Таким образом, на вход сумматора 22 в этом такте поступает . код проверяемых логических условий, модифицированный сигналами логических условий со входа 17. Это позволяет обнаруживать ошибки при ветвлениях.

При считывании многотактных микрокоманд форматов ФЗ и Ф4 на выходе элемента ИЛИ 15 возникает импульс, вызывающий подачу на выход блока 16 коммутации контрольного кода с выхода 10 блока 7 памяти и с некоторой задержкойкода с выхода 11. Эти коды без изменений проходят через блок 21 элементов И на вход сумматора 22 и суммируются с его содержимым. Затем на вход элемента И 23 с выхода элемента ИЛИ 15 поступает импульс опроса состояния сумматора 22, задержанный элементом 29 задержки блока 26 формирования установочных сигналов. Если состояние сумма-г тора 22 нулевое, что соответствует отсутствию сбоев, то триггер 24 остается в нулевом состоянии и устройство продопхшет Нормально функционировать. Если же при опросе состояние сумматора

22не ьгуяевое, что свидетельствует о происшедшем сбое с момента прет11Дущего контроля, то триггер 24 устанавливает ся в единичное состояние и устройство переходи-т в режим восстановления.

Нулевой сигнал на нулевом выходе триггера 24, поступающий на входы элементов И ЗО и 32, не разрешает запись адреса следующей микрокоманды в регистр 2, а при считывании микрокоманды формата Ф4 новый адрес повтора в регистр 3 из регистра 2 также не перезаписывается. Адресный вход блока 7 памяти через блоки 5 и 6 элементов И и ИЛИ соединяется с выходом регистра 3 адреса повтора. Осуществляется считывание микрокоманды формата Ф4 по адресу из регистра 3. Так как триггер 24 находится в единичном состоянии, то единичный импупьс с выхода 3 дешифратора 14 вызывает появление импульса на выходе элемента И 27. Элемент 28 задержки задерживает этот импульс до момента окончания процессов установления и опроса состояния сумматора 22 и затем устанавливает его и триггер 24 в нулевое состояние. Адресный вход.блока 7 памяти при этом снова подключается к выходу регистра 2. через открытые элементы И . блока 4 и блока 6 элементов ИЛИ. Тем самым осуществляется восстановление исходного состояния средств контроля и осуществляется выполнение участка микропрограммы, на котором произошел сбой. После заданного числа попыток восстановления фиксируется отказ с помощью схем {не показаны).

Потактовое формирование контрольного соотношения, позволяет контролировать считывание микрокоманд из. блока памяти, обнаруживать ошибки при ветвлениях, а также пропуски или выполнение лишних микрокоманд на всех участках микропрограмм. Это позволяет существенно повысить достоверность функционирования устройства.

Формула изобретения

1. Микропрограммное устройство управления, содержащее регистр адреса и регистр микрокоманд, блок памяти, блок формирования установочных сигналов и управляемый генератор импульсов, первый вход которого соединен с первым выходом блока памяти, второй выход которого соединен с информационным, входом регистра микрокоманд, выход которого подключен к выходу устройства, а вход синхронизации - к первому выходу управляемого генератора импульсов, второй выход которого соединен с первым входом блока формирования установочных сигналов, первый выход которого соединен с входом синхро ниэации регистра адреса, информационный вход которого соединен с входолл адреса устройства, отличающееся тем что, с цепью повышения достоверности функционирования устройства, оно допопнитепьно содержит бпок коммутации, накапгшвающий сумматор, триггер, регистр адреса повтора, четыре блока элементов И, два блока элементов ИЛИ, элемент НЕ, элемент ИЛИ и дешифратор, причем информационный вход регистра адреса повтора соединен с выходом регистра ад-, реса и первым входом первого блока элементов И, вход синхронизации - с вторым выходом блока формирования установочных сигналов, выход регистра адреса повтора подключен к .первому входу второго блока элементов И, выход которого соединен с первым входом первого блока эле ментов ИЛИ, второй вход которого соединен с выходом первого блока элементов И, выход первого блока элементов ИЛИ подключен к адресному входу блока памяти, первый, второй, третий и четвертый выходы которого соединены с соответствующими входами блока коммутации, пятый и шестой выходы - с первым и вто рым входами дешифратора, стробируюший вход которого подключен к первому вы|Ходу управляемого генератора импульсов, первый и второй выходы дешифратора соединены с одноименными входами элемента ИЛИ, выход которого соединен с пя тым входом блока коммутации, шестой и седьмой входы которого подключены соответственно к третьему и четвертому выходам дешифратора, выход блока коммутации соединен с первым входом третьего блока элементов И, второй вход которого соединен с выходом второго блока элементов ИЛИ, первый вход которого подвключен к входу логических условий устройства, второй вход через элемент НЕ к третьему выходу дешифратора, второй вьгход которого соединен с вторым входом блока формирования установочных сигна:пов, третий вход которого соединен с вы:ходом элемента ИЛИ и вторым входом уп равляемого генератора импульсов, третий выход блока формирования установочных сигналов соединен с первым входом четвертого блока элементов И, четвёртый выход - с нулевым входом триггера .и установочным входом накапливающего сумматора, выход которого подключен к второму входу четвертого блока элементов И, выход которого соединен с единичнь1м входом триггера, единичный выход которо 95 В„ 1О го соединен с четвертым входом блока формирования входных сигналов и вторым входом второго блока элементов И, нулевой выход триггера соединен с вторым входом первого блока элементов И и пятым входом блока формирования устано- вочных сигналов. 2.Устройство по п. 1, отличающее с я тем, что блок коммутации содержит шифратор, выходы ко орого соединены с первыми входами S блоков элементов И, выходы которых соединены с входами соответствующих элементов ИЛИ, вторые входы 5 блоков элементов И соединены с первыми и вторым входами блока, вход шифратора подключен к выходу (S+l)-ro блока элементов И, первый чход которого подключен к первому входу (S+2)-ro блока элементов И и является четвертым входом блока коммутации, третий вход блока коммутации подключен к первому входу (5 +3 )-го блока элементов И, второй вход которого соединен с выходом ()-ro элемента ИЛИ, первый вход которого соединен с пятым входом блока коммутации и через первый элемент задержки с вторым .входом (5+2)-го блока элементов И, выход которого подключен, к первому входу блока S элементов ИЛИ, второй вход которого подключен к выходу (S+3)-ro блока элементов И, третий вход - к выхо :дам S элементов ИЛИ, а выход блока, элементов ИЛИ является выходом блока коммутации, шестой вход блока коммутации подключен к второму входу (5 +1 )-го элемента ИЛИ, третий вход которого через второй элемент задержки соединен с вторым входом (5+1)-го блока элементов И и $тляется седьмым входом блока коммутации. 3.Устройство по п. 1, отличающее с я тем, что блок формирования установочных сигналов содержит три элемента И и три элемента задержки, причем первый вход блока подключен к первому входу первого элемента И, второй вход которого подключен к пятому входу блока и первому входу второго элемента И, второй вход которого через первый элемент задержки, подключен к второму входу блока и первому входу третьего элемента И, второй вход которого подключен к первому входу блока, выход третьего элемента И через второй элемент задержки подключен к четвертому входу блока, третий вход блока через третий элемент задержки подключен к третьему выходу блока, выход первого

1195505812

элемента И подключен к первому выходу1. Авторское свидетепьство СССР

блока, выход второго элемента И под-.№ 741267, кп. Q 06 F 9722, 1980.

ключей к второму выходу блока.2. Авторское свидетельства СССР

Источники информации,.№ 616629, кл. Q 06 F 9/22, 1978

принятые во внимание при экспертизе s (прототип).

б

ПП 35

г

т

№,3

Ф(/«.4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1275442A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

| Микропрограммное устройство управления | 1980 |

|

SU935960A1 |

| Микропрограммное устройство управления | 1981 |

|

SU985790A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968814A1 |

| Микропрограммное устройство управления | 1980 |

|

SU943728A1 |

Авторы

Даты

1982-08-30—Публикация

1980-11-18—Подача