ел С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Устройство для обмена информацией | 1989 |

|

SU1702378A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1188736A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1381506A1 |

| Многотактное микропрограммное устройство управления | 1986 |

|

SU1332318A1 |

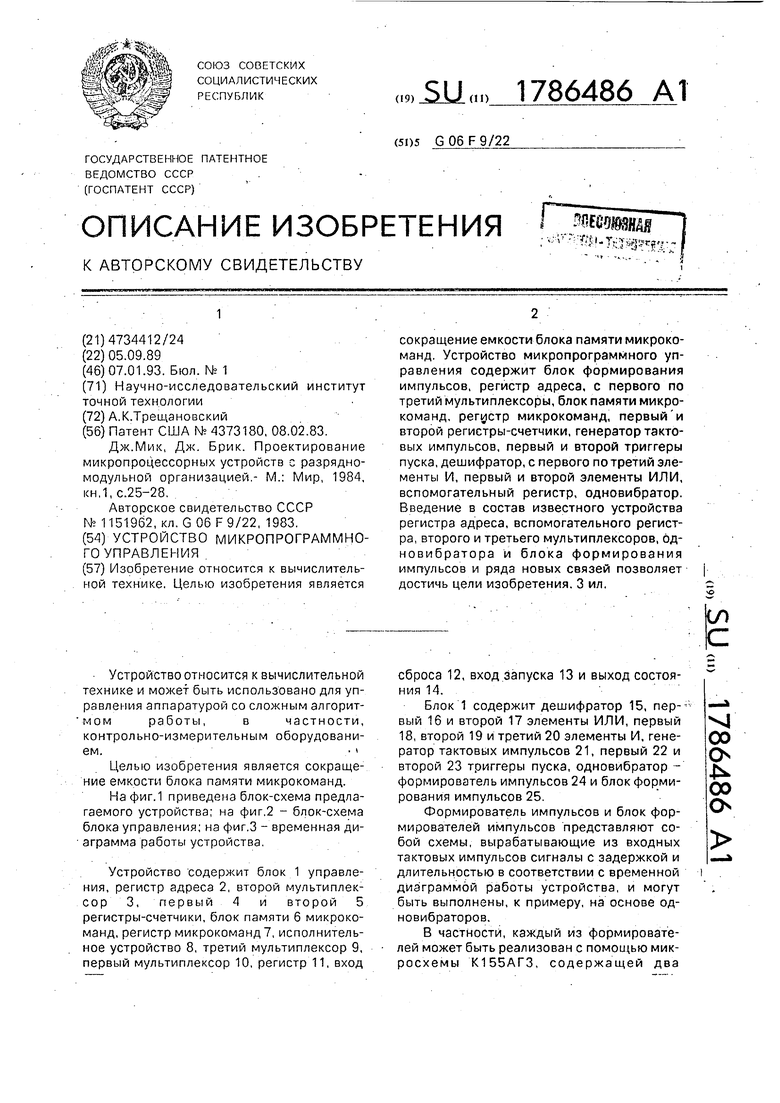

Изобретение относится к вычислительной технике. Целью изобретения является 2 сокращение емкости блока памяти микрокоманд. Устройство микропрограммного управления содержит блок формирования импульсов, регистр адреса, с первого по третий мультиплексоры, блок памяти микрокоманд, регистр микрокоманд, первый и второй регистры-счетчики, генератор тактовых импульсов, первый и второй триггеры пуска, дешифратор, с первого по третий элементы И, первый и второй элементы ИЛИ, вспомогательный регистр, одновибратор. Введение в состав известного устройства регистра адреса, вспомогательного регистра, второго и третьего мультиплексоров, 6д- новибратора и блока формирования импульсов и ряда новых связей позволяет достичь цели изобретения. 3 ил.

Устройство относится к вычислительной технике и может быть использовано для управления аппаратурой со сложным алгоритмомработы, в частности, контрольно-измерительным оборудованием.

Целью изобретения является сокращение емкости блока памяти микрокоманд.

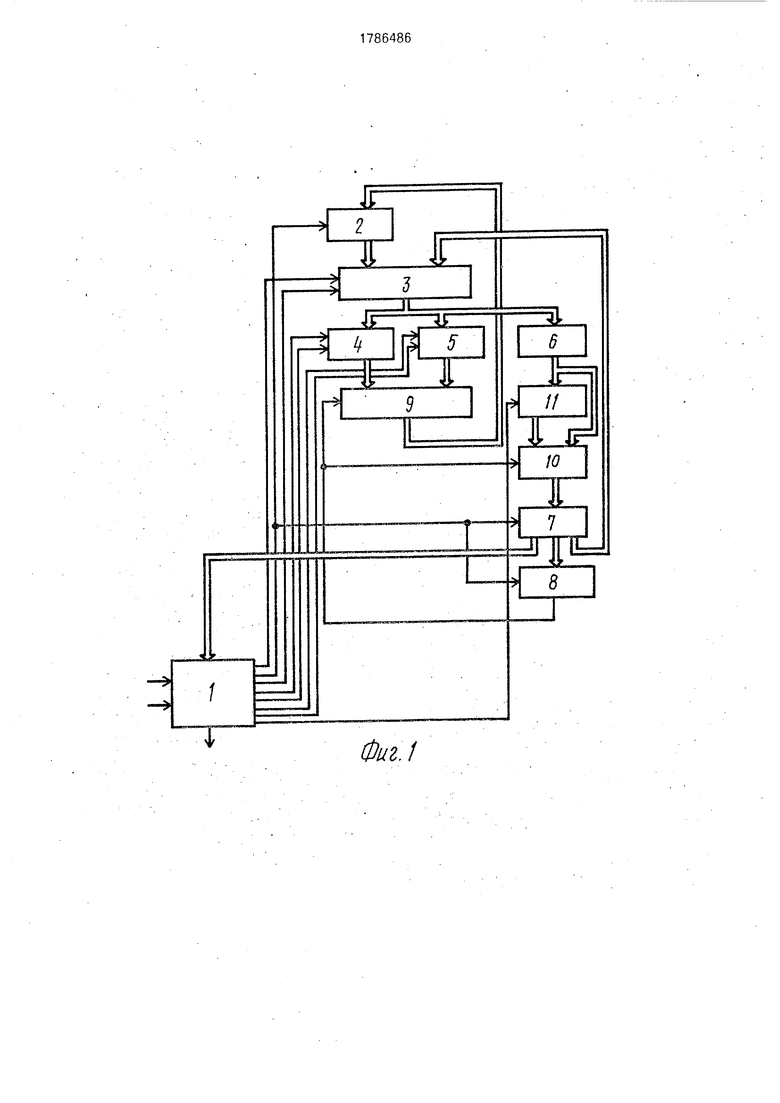

На фиг.1 приведена блок-схема предлагаемого устройства; на фиг,2 - блок-схема блока управления; на фиг.З - временная диаграмма работы устройства.

Устройство содержит блок 1 управления, регистр адреса 2, второй мультиплексор 3, первый 4 и второй 5 регистры-счетчики, блок памяти 6 микрокоманд, регистр микрокоманд 7, исполнительное устройство 8, третий мультиплексор 9, первый мультиплексор 10, регистр 11, вход

сброса 12, вход запуска 13 и выход состояния 14.

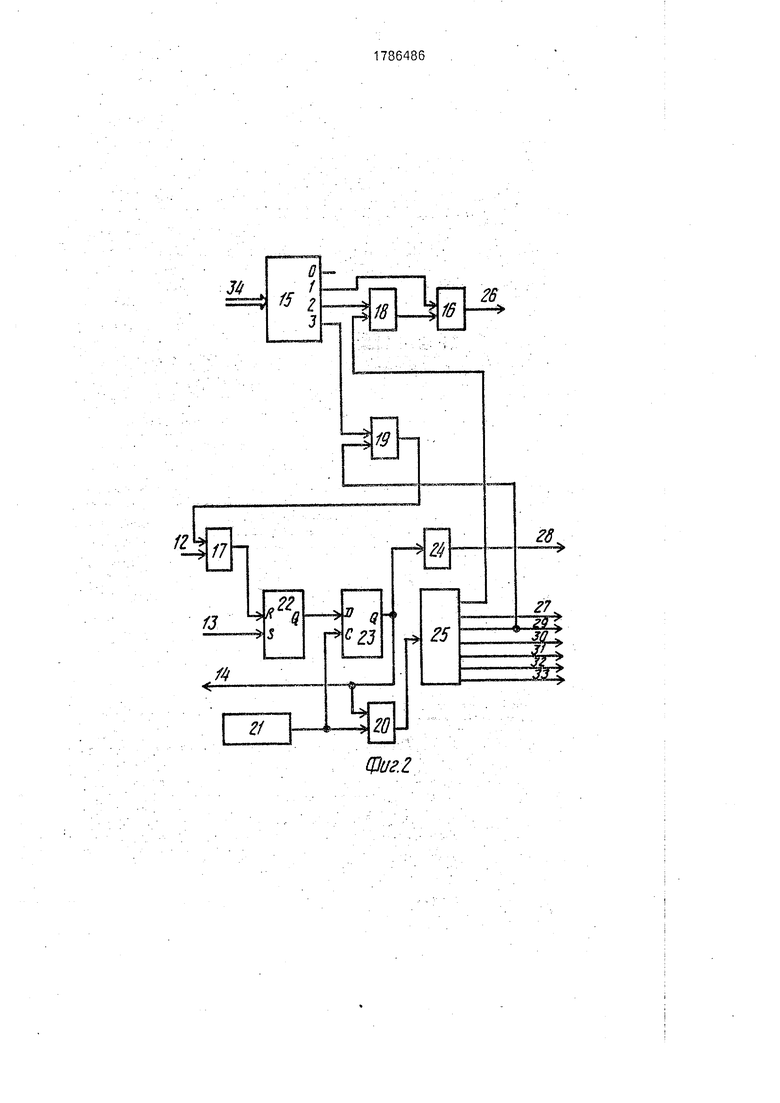

Блок 1 содержит дешифратор 15, пер- вый 16 и второй 17 элементы ИЛИ, первый 18, второй 19 и третий 20 элементы И, генератор тактовых импульсов 21, первый 22 и второй 23 триггеры пуска, одновибратор - формирователь импульсов 24 и блок формирования импульсов 25.

Формирователь импульсов и блок формирователей импульсов представляют собой схемы, вырабатывающие из входных тактовых импульсов сигналы с задержкой и длительностью в соответствии с временной диаграммой работы устройства, и могут быть выполнены, к примеру, на основе од- новибраторов.

В частности, каждый из формирователей может быть реализован с помощью микросхемы К155АГЗ, содержащей два

vj со

О

4

00 О

одновибратора. При последовательном включении одновибраторов первый из них обеспечивает формирование задержки относительно входного импульса, а второй элемент формирует длительность выходного импульса.

Все остальные блоки устройства могут быть непосредственно реализованы соответствующими цифровыми интегральными микросхемами,

Под исполнительным устройством подразумевается некоторое устройство, работающее под микропрограммным управлением и имеющее, как минимум, перечисленные выше входы и выход. Подобным устройством могут быть различные АЛУ, операционные устройства, микропроцессорные секции и т.п. При этом управляющие входы служат для задания кода микрокоманды, вход синхронизации - для временной синхронизации работы исполнительного устройства в увязке с работой устройства в „Целом, например, для фиксации результата выполнения микрокоманды во внутренних регистрах, аккумулятора и пр. Выход сЬйтрййи я индицирует результат выполнения микрокоманды.

Устройство работает следующим образом. , , . ./ ... .;.... ........

Управление работой устройства осуществляется путем лодачи сигналов извне на входы 12,13 и анализа сигнала на выходе 14 блока управления 1 любым из известных способов, числе с помощью ЭВМ при наличии соответствующего контроллера. Установка устройства в исходное состояние производится подачей импульса на вход 1.2 блока управления 1. Проходя через элемент ИЛИ 17 на вход сброса первого триггера 22, сигнал ycfaHавливаетИа его выходе уровень логического нуля, который подается на информационный вход второго триггера 23 и проходит на его выход после поступления на вход синхронизации триггера 23 очередного импульса с выхода генератора 21, что индицируется на выходе 14 и препятствует прохождению тактовых импульсов с выхода генератора 21 через третий элемент И 20 на вход блока 25. В результате этого устройство находится в исходном (неработающем) состоянии. ..- . ..

Запуск работьГустройства осуществляется подачей импульса на вход 13 (вход установки первого триггера 22). При этом первый триггер 22 взводится в единичное состояние, что по аналогии с описанным выше приводит к появлению логической единицы на выходе второго триггера 23.

Сигнал с выхода триггера 23 поступает на выход 14, указывая на работу устройства,

и разрешает прохождение тактовых импульсов через третий элемент И 20 на блока формирователей импульсов 25, на в л- ходах которого начинается генерация ий-.

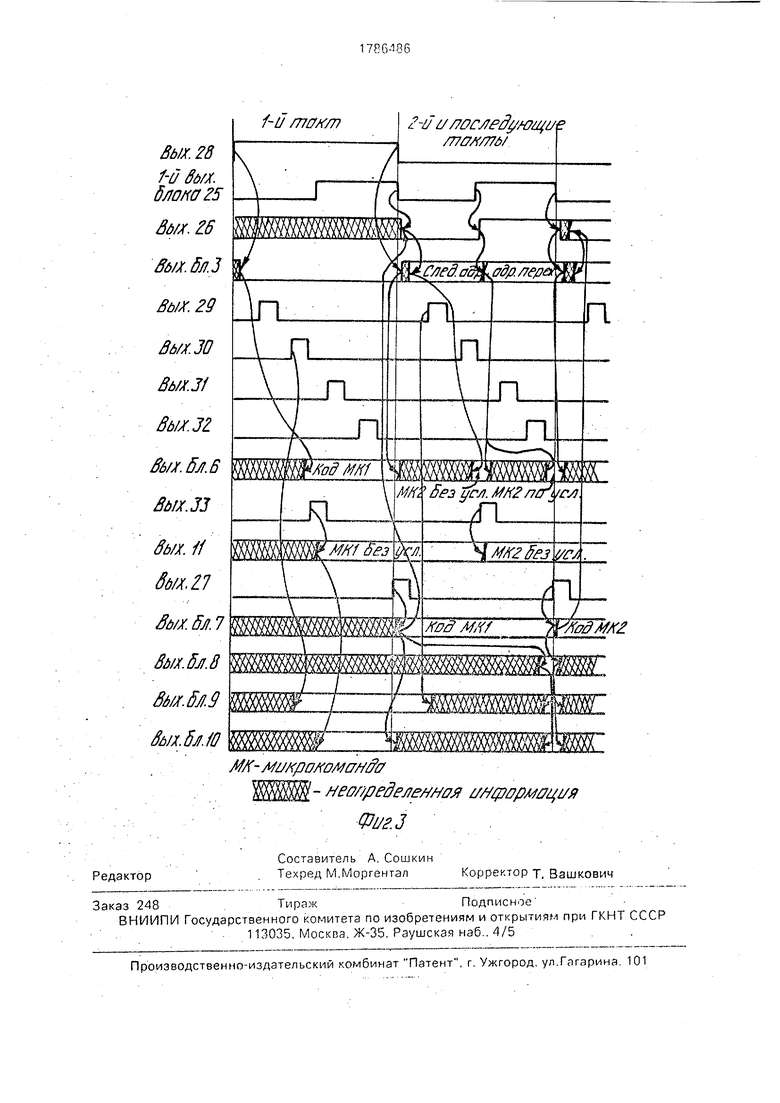

пульсов в соответствии с временной диаграммой фиг.3. : i

Кроме того, по фронту сигнала на вы(о- де триггера 23 первый формирователь 24 обеспечивает появление на третьем 28 в ыходе блока управления 1 импульса с д/|и- тельностью, равной такту работы устройства. Поступая на вход разрешения мультиплексора 3, этот импульс запрещает его работу, устанавливая на его выходах код

нуля, поступающий далее на адресные управляющей памяти 6 и на входы первого 4 и второго 5 регистров-счетчикфв.

Этим обеспечивается принудительная $ыборка микрокоманды по нулевому адресу в

первом такте работы устройства, В каждом следующем такте работы выборка кода che- дующей микрокоманды из управляющей Памяти 6 на входы регистра 7 буДет выполняться по адресу, определяемому текущим кодом на вторых выходах регистра 7, содержимым регистра 2 и состоянием исполнительного устройства 8..

В зависимости от кода на вторых выходах регистра 7 устройство реализует сле|ду ющиевиды -управления последовательностью:

О - безусловный переход к следующей микрокоманде;

1 - безусловный переход по адресу, ука- занному на первых выходах регистра 7;

2 - переход по адресу регистра 7 При выполнении условия или переход к следующей микрокоманде при невыполнении условия, причем условием служит определенное состояние устройства 8;

3 -останов по концу микропрограмМы. В начале такта работы устройства проводится дешифрация кода микрокоманды, поступающего со вторых выходов регистра

7 через первые входы 34 блока 1 на деи|иф- ратор 15. В результате дешифрации микрокоманд 1, 2 или 3 появляется сигна на одном из соответствующих выходов деЦмф- ратора 15. .

Рассмотрим выполнение микроко ан- ды 2. Сигнал с первого выхода блокф 25 управляет прохождением сигнала со второго выхода дешифратора 15 через элеме -пг И 18 на второй вход элемент ИЛИ 16 и д злее

через выход 26 блока 1 на вход управления мультиплексора 3. При этом, как показано на фиг.З, в первомлотгутактепрохождение сигнала разрешено, а во втором - но. Это обеспечивает подачу на выводе

мультиплексора 3 в первом полутакт информации с выхода регистра 2, хранящего адрес следующей микрокоманды, а во втором полутакте - информации с первых выходов регистра 7, указывающих адрес перехода. По окончании переходных прб- цессов на выходе мультиплексора 3 происходит запись информации в регистр-счетчик 4 по сигналу с выхода 29 блока 1 и наращивание содержимого регистра-счетчика 4 по сигналу с выхода 30 блока 1. Тем самым в регистре-счетчике 4 устанавливается адрес следующей микрокоманды по отношению к микрокоманде, подлежащей выполнению в следующем такте, для случая последовательной выборки, т.е. при невыполнении условия. Одновременно по адресу, определяемому содержимым регистра 2, из управляющей памяти 6 проводится выборка следующей микрокоманды, код которой записывается в регистр 11 с помощью импульса, поступающего с выхода 33 блока 1 в конце первого полутакта. Аналогично во втором полутакте в регистре - счетчике 5 устанавливается адрес следующей микрокоманды для случая перехода по условию. При этом используются импульсы загрузки и наращивания, подаваемые на входы регистра-счетчика 5 соответственно с выходов 31 и 32 блока 1. Адрес выбираемый микрокоманды для случая перехода по условию подается во втором полутакте с первых выходов регистра 7 через мультиплексор 3 на адресные входы управляющей памяти 6. Таким образом, к концу такта на первых входах мультиплексора Юс выходов памяти 6 установлен код следующей микрокоманды для случая перехода по уславию, а с выходов регистра 11 на вторые входы мультиплексора 10 поступает код микрокоманды для случая невыполнения условия.

В это же время исполнительное устройство 8 проводит выполнение текуа(ей микрокоманды в соответствии с состоянием третьих выходов регистра микрокоманд 7. С выхода состояния устройства 8 результат выполнения микрокоманды в конце такта поступает на входы управления мультиплексоров 9 и 10. При наличии логической единицы на выходе состояния устройства 8 (условие выполнено) мультиплексор 9 обеспечивает прохождение на его выходы информации со второго 5 регистра-счетчика, в результате чего на входы регистра 2 поступает адрес следующей микрокоманды относительно выполняемой в следующем такте микрокоманды для случая выполнения условия в текущем такте. В противном случае на входы регистра 2 поступит информация с выходов первого 4 регистра-счетчика, что соответствует переходу к следующей микрокоманде при невыполненном условии. После установления информации на выхо- дах мультиплексора 9 она может быть записана в регистр 2,

5Аналогично описанному сигнал с выхода состояния устройства 8 управляет мультиплексором 10, обеспечивая к концу такта появление на его выходах одного из двух возможных (в зависимости от выполнения

0 условия) кодов следующей микрокоманды. Импульс, поступающий с выхода 27 блока 1 в конце такта, обеспечивает запись правильной информации в регистры 2 и 7. В следующем такте работы устройство готово

5 выполнять аналогичные действия.

В отличие от микрокоманды 2 при выполнении микрокоманды 0 на выходе 26 блока 1 в течение всего такта поддерживается нулевой уровень, а при выполнении

0 микрокоманды 1 - единичный уровень благодаря наличию единичного сигнала на пер вом выходе дешифратора 15. Тем самым обеспечивается соответственно безусловный переход к следующей микрокоманде и

5 безусловный переход по заданному адресу. В первом случае мультиплексор 3 обеспечивает прохождение на свои выходы и дал ее на другие блоки устройства информации с выходов регистра 2, а во втором случае - с

0 первых выходов регистра 7. Поскольку состояния входов мультиплексоров 9 и 10 к концу такта попарно неразличимы, то сигнал на выходе состояния устройства 8 не влияет на работу схемы.

0 результате дешифрации которой сигнал с третьего выхода дешифратора 15 поступает на первый вход элемента И 19, стробируе- мого импульсом со. второго выхода блока 25, и далее через элемент ИЛ И 17 на входсбро5 са первого 22 триггера. Это приводит к установке логического нуля на выходе второго 23 триггера после прихода на его вход синхронизации очередного импульса с выхода генератора 21, что индицируется на выходе

0 14 устройства и препятствует прохождению тактовых импульсов через первый элемент И 20 на другие блоки устройства. Формула изобретения Устройство микропрограммного управ5 леиия, содержащее блок памяти микрокоманд, регистр микрокоманд, первый и второй регистры-счетчики, первый мультиплексор, генератор тактовых импульсов, первый и второй триггеры пуска, дешифратор, с первого по третий элементы И, первый и второй элементы ИЛИ, причем выход блока памяти микрокоманд соединен с первым информационным входом первого мультиплексора, выход которого соединен с информационным входом регистра микро- команд, выход поля переходов которого соединен с входом дешифратора, с первого по третий выходы которого соединены с первыми входами первого элемента ИЛИ, первого и второго элементов И, выход первого элемента И соединен с вторым входом первого элемента ИЛИ, выход второго элемента И соединен с первым входом второго элемента ИЛИ, выход которого соединен с входом установки в О первого триггера пуска, выход которого соединен с информационным входом второго триггера пуска, выход генератора тактовых импульсов соединен с первым входом третьего элемента И и с входом синхронизации второго триг- гера пуска, входы сброса и пуска устройства соединены соответственное вторым входом второго элемента ИЛИ и с входом установки в 1 второго триггера пуска, отличающееся тем, что, с целью сокращения емкости блока памяти микрокоманд, оно содержит регистр адреса, вспомогательный регистр, второй и третий мультиплексоры, одновибратор, блок формирования импульсов, причем выход поля адреса регистра микрокоманд соединен с первым информационным входом второго мультиплексора, выход которого соединен с информационными входам первого и второго счетчиков и адресным входом блока памяти микроко- манд, выход которого соединен с информационным входом вспбмогательногд регистра, выход которого соединен с вторым информационным входом первого мультиплексора, выходы первого и второго регистров-счетчиков соединены соответс|- венно с первым и вторым информационнь - ми входами третьего мультиплексора, выход которого соединен с информационным входом регистра адреса, выход которого соединен с вторым информационным входим второго мультиплексора, выход поля операций регистра микрокоманд подключен куЬ- равляющему выходу устройства, вход логических условий устройства подключен; к управляющим входам первого и третьего мультиплексоров, выход третьего элемента И соединен с входом запуска блока формирования импульсов, первый выход которого соединен с вторым входом первого элемента И. второй выход блока формирования импульсов соединен с входами запи си регистров адреса и микрокоманд, третий выход блока формирования импульсов cbe- динен с вторым входом второго элементу И и с входом записи первого регистра-счетчика, с четвертого по седьмой выходы блрка формирования импульсов соединены сфт- ветственно с входом прибавления единицы первого регистра-счётчика, с входами заЬи- си и прибавления единицы второго регистра-счетчика и с входом записи вспомогательного регистра, выход второго триггера пуска соединен с выходом состояния устройства, с вторым входом третьего элемента И и с входом одновибратора, выход которого соединен с входом стробйро- вания второго мультиплексора, ,вы;ход первого элемента ИЛИ соединен с управляющим входом второго мультиплексора.

Т

Фиг.

Фиг.1

| Патент США № 4373180, 08.02.83 | |||

| Дж.Мик, Дж | |||

| Брик | |||

| Проектирование микропроцессорных устройств с разрядно- модульной организацией.- М.: Мир, 1984, КН.1.С.25-28 | |||

| Микропрограммное устройство управления | 1983 |

|

SU1151962A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-01-07—Публикация

1989-09-05—Подача