кстремума производной сигнала ошиби подключен к входу усилителя и ерез первый коммутатор к одному из воих входов, выход дифференциатора; сигнала ошибки соединенс одним из входов блока вьаделения экстремума производной сигнала смиибки, а выход огического блока подключен к одному из входов первого и второго комутаторов.

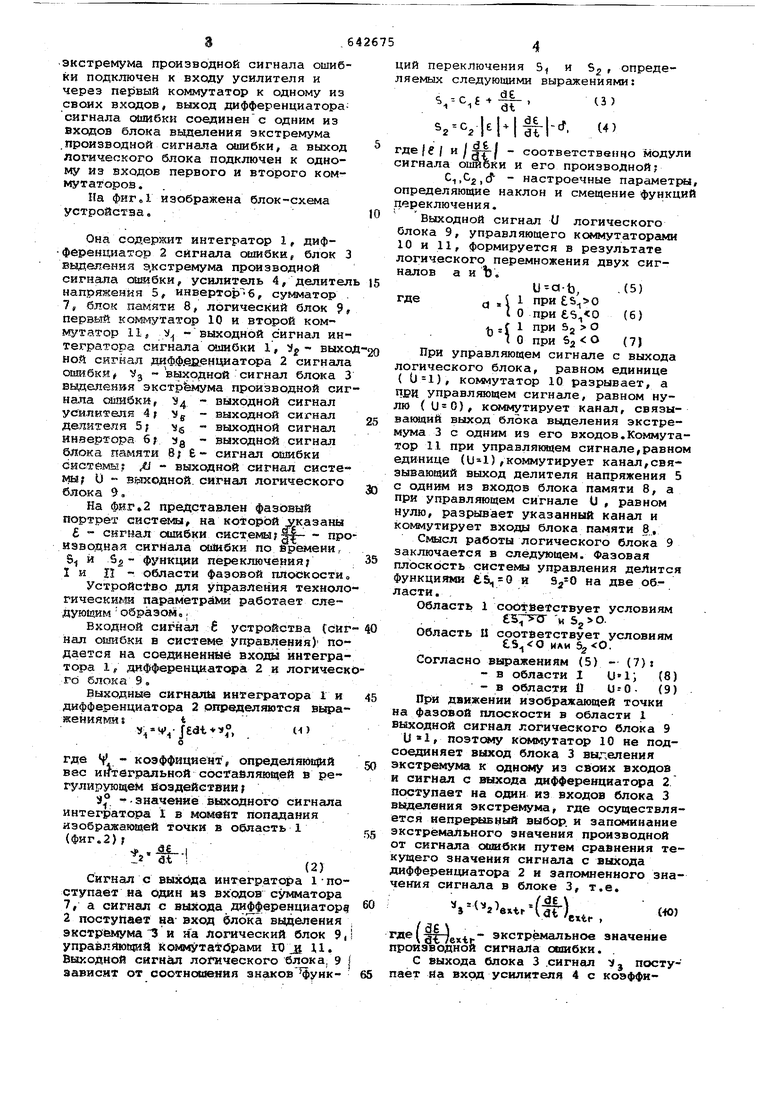

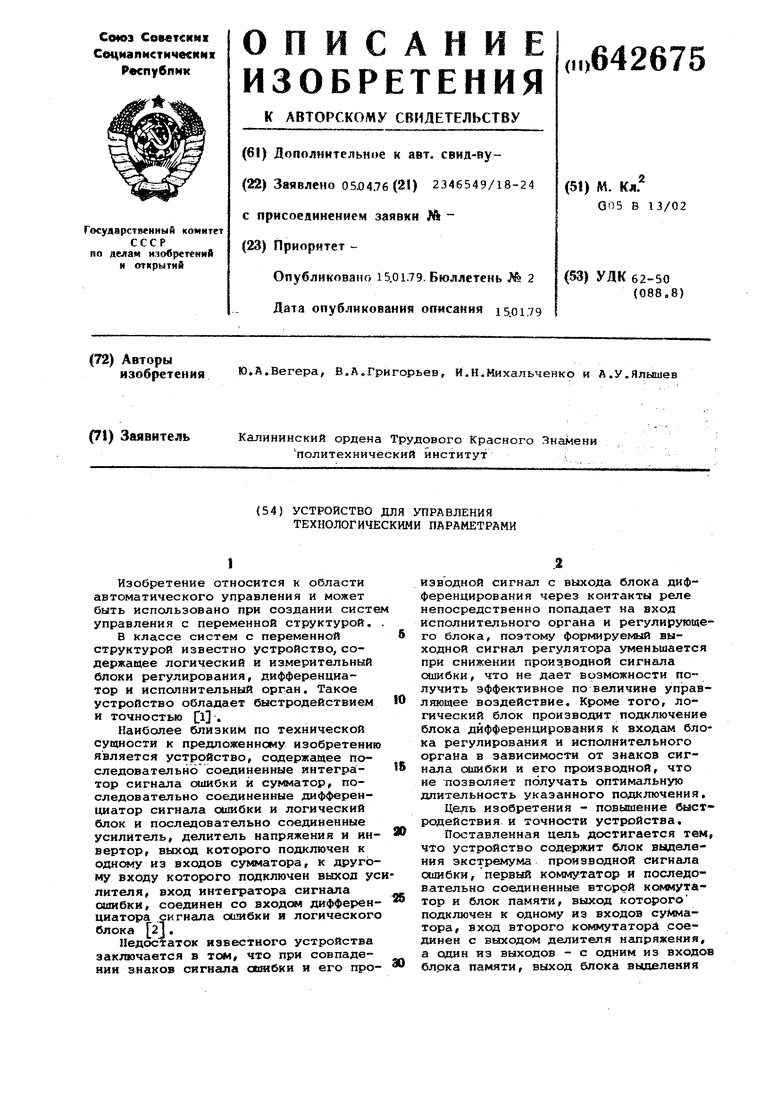

На фиг,1 изображена блок-схема устройстзае10

Она содержит интегратор 1, диферещдаатор 2 сигнала ошибки, блок 3 ыделения э,кстремума производной игнала сшшбки, усилитель 4, делитель is напряжения 5, инвертор 6, сумматор . 7, блок памяти 8, логический блок 9, первый коммутатор 10 и второй коммутатор 11, к -выходной сигнал интегратора сигнала оашбки 1, У - выхо1Д-2о ной сигнал дифф1еЕен1з атора 2 сигнала ошибки Vg - выходной сигнал блока 3 вьвделензя экстремума производной сигнала слйибки, 4 выходной сигнал усилителя 4 Vg - выходной сигнал gs делителя 5 j б выходной сигнал инвертора 6; Зд - выходной сигнал блока памяти 8 - сигнал ошибки систезиш; Д} - выходной сигнал систе мы; и вдогодной сигнал логического блока 9,

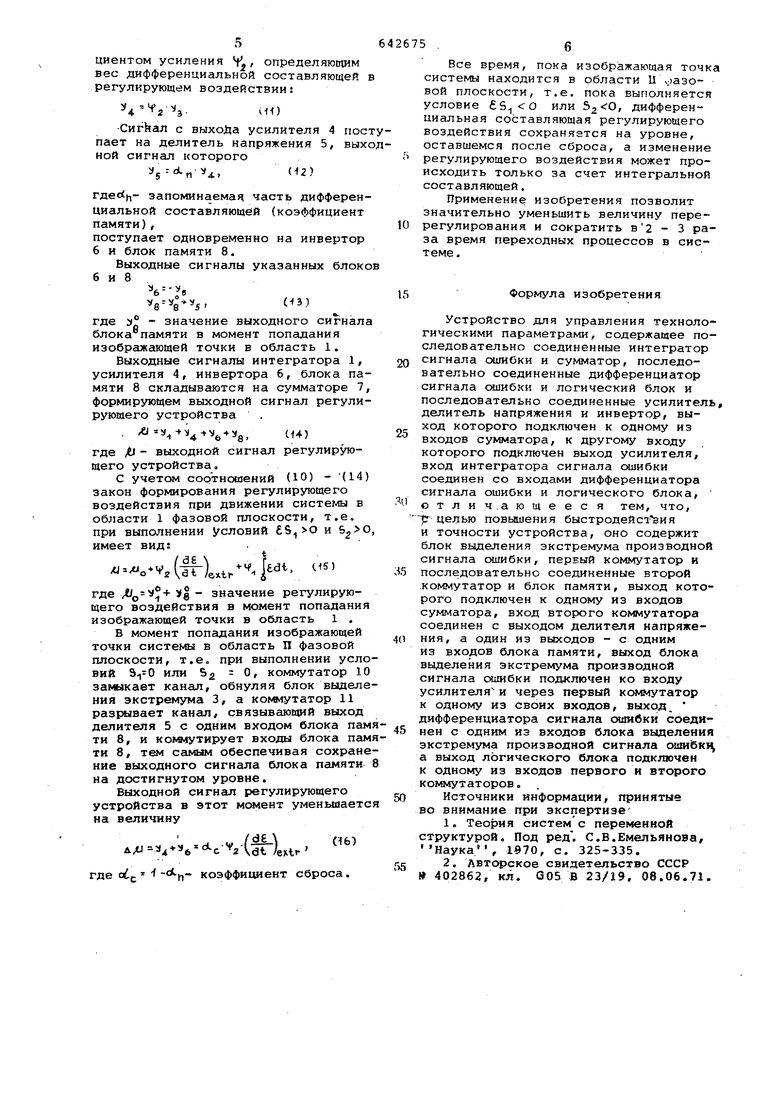

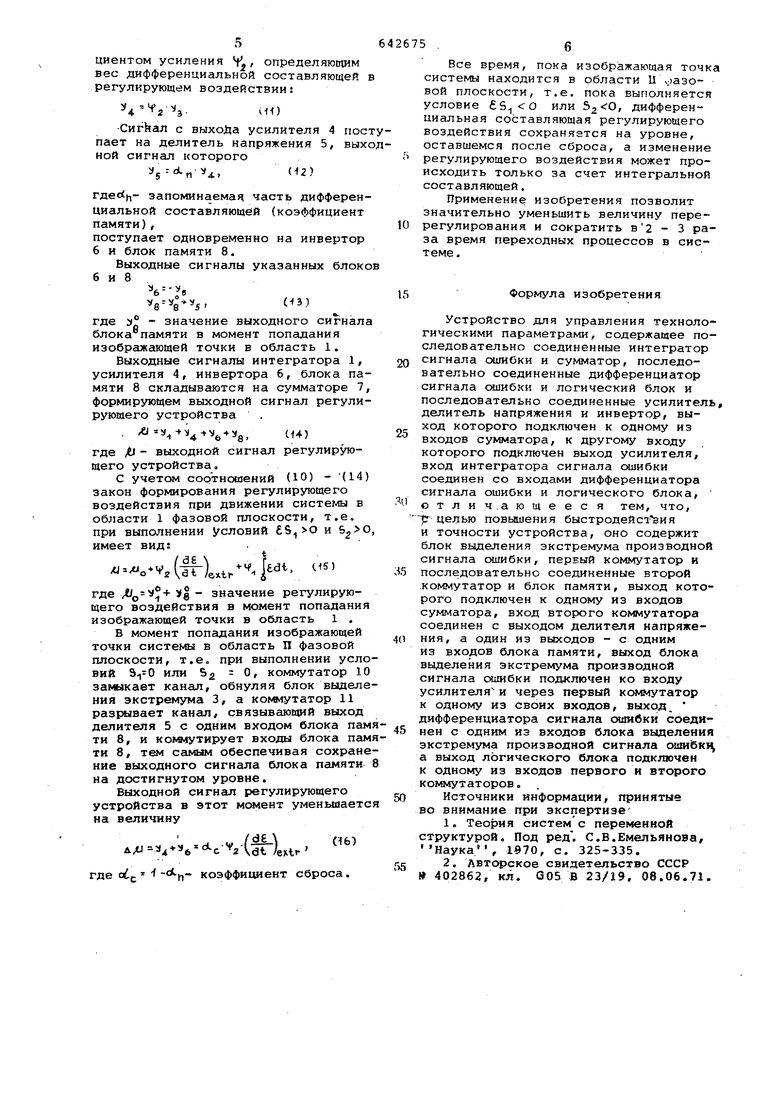

На представлен фазовый портрет система, на которой указаны

- снгнал ошибки оистеки; производная сигнала оьШбки по времени, 9 и функции переключения; 3S

1и II - области фазовой шюскости.

Устройство для управления технологически№з параметрами работает следую1ггим образом,.

Входной сигнал 6 устройства (сиг- 40 нал ошибки в системе управления) подается на соеднненныё входы интегратора If дифференциатора 2 и логическО;Го блока 9 в

Выходные сигнаЛй1 интегратора 1 и 45 дифференциатора 2 рпрвделяются ввд ажениямн t „

v:,«v -jeai T f,to

огде V - коэффициент, определя1д1ций д вес интегральной составляющей в регулирующем боэдействии;

S°. -значение выходного сигнала HHTerpiaTOpa I в момейт попадания иэображакнйей точки в область 1,.,

(фиг.2); .

J , Я5 .1

a;a.t (2)

Сигнал с выхода интегратора 1-поступает на один из входов сумматора 7, а сигнал с выхода дифференциатору 60

2поступает на вход ввделения . экстремума 3 и яа логический блок 9«1 управляющий Коммутаторами ГОЛ Ц. Выходной сигнал логического блока, 9 | зависит от соотнсяоеяяя знеисов 65

ций переключения 5 и S г определяе1чых следующими выражениями: ае

(3 )

л-

г .1ЧЧ1гН-

/дт/ соответственно модули сигнала оишбки и его производной;

Ci,C.2,cf - настроечные параметр определяющие наклон и смещение функци переключения.

Выходной сигнал U логического блока 9, управляющего коммутаторами 10 и 11, формируется в результате логического перемножения двух сигналов а и Ъ,

U-cl-b, .(5) где d Л

С О при ,5,0 (6) 1 при Sg 0

( О при 6д 0 (7J При управляющем сигнале с выхода логического блока, равном единице ( ), коммутатор 10 разрывает, а ПРИ управляющем сигнале, равном нулю { ), коммутирует канал, связываиндий выход блока выделения экстремума 3 с одним из его входов.Коммутатор 11 при управлякнцем сигнале,равном единице () ,коммутирует кангш,связывающий выход делителя напряжения 5 с одним из входов блока памяти 8, а при управляющем сигнале U , равном нулю, разрывает указанный канал и коммутирует входы блока памяти 8,

Смысл работы логического блока 9 заключается в следующем. Фазовая плоскость систели управления делится функциями 5ц 0 и Зд-О на две области.

Область 1 соответствует условиям 575 и .

Область II соответствует условиям МАИ .

Согласно ВЁфажениям (5) - (7)

-в области 1 (8)

-в области 11 и - О - (9) При движении иэобрг1жающей точки

на фазовой плсюкости в области 1 выходной сигнал логического блока 9

и, поэтс у коммутатор 10 не подсоединяет выход блока 3 аылеления экстремума к одн( из своих входов и сигнал с выхода дифференциатсфа 2 поступает на один из входов блока 3 выделения экстрек ма, где осуществляется непре 1БНЫй выбор, и запоминание экстремального значения производной от сигнала ошибки путем сравнения текущего значения сигнала с выхода дифференциатора 2 и запомненного значения сигнала в блоке 3, т.е.

..,.,-(If )„,,,

(Ю)

,(м

где gl /exir экстремальное значение производной сигнала оогабки. .

С выхода блока 3 .сигнал -у поступает йа вход усилителя 4 с коэффициентом усиления Y, определяющим вес дифференциальной составляющей регулирующем воздействии И1) Сигнал с выхода усилителя 4 пос пает на делитель напряжения 5, вых ной сигнал которого s -nгдес,- запоминаемач часть дифференциальной составляющей (коэффициент памяти), поступает одновременно на инвертор 6 и блок памяти 8. Выходные сигналы указанных блоко б и 8 в 8 значение выходного сигнал блока памяти в момент попадания изображсиощей точки в область 1. Выходные сигналы интегратора 1, усилителя 4, инвертора 6, блока памяти 8 складываются на сумматоре 7 формирующем выходной сигнал регулирующего устройства , - где Jb - выходной сигнал регулирующего устройства, С учетом соотношений (Ю) - (14 закон формирования регулирующего воздействия при движении системы в области 1 фазовой плоскости, т.е, при выполнении условий и имеет ВИД .w,(|fX,,,4,|edi. U5, где - значение регулирующего воздействия в момент попадания изображающей точки в область 1 . В момент попадания изображающей точки системы в область П фазовой плоскости, т.е. при выполнении усло вий или S-j О, коммутатор 10 замыкает канал, обнуляя блок выделе ния экстремума 3, а KONwyTaTop 11 раз1швает канал, связывающий выход делителя 5 с одним входом блока пам ти 8, и коммутирует входы блока пам ти 8, тем самым обеспечивая сохран ние выходного сигнала блока памяти на достигнутом уровне. Выходной сигнал регулирующего устройства в этот момент уменьшает на величину i.dt /eU«где odg -н коэффициент сброса. Все время, пока изображающая точка системы находится в области ЦЧоазовой плоскости, т.е. пока выполняется условие или , дифференциальная составляющая регулирующего воздействия сохраняется на уровне, оставшемся после сброса, а изменение регулирующего воздействия может происходить только за счет интеграшьной составляющей. Применение изобретения позволит значительно уменьшить величину перерегулирования и сократить в2 - 3 раза время переходных процессов в системе. Формула изобретения Устройство для управления технологическими параметрами, содержащее последовательно соединенные интегратор сигнала ошибки и сумматор, последовательно соединенные дифференциатор сигнала ошибки и логический блок и последовательно соединенные усилитель, делитель напряжения и инвертор, выход которого подключен к одному из входов сумматора, к другому входу которого подключен выход усилителя, вход интегратора сигнала ошибки соединен со входами дифференциатора сигнала ошибки и логического блока, отлич.ающееся тем, что, рг целью повышения быстродействия И точности устройства, оно содержит блок выделения экстремума производной сигнала ошибки, первый коммутатор и последовательно соединенные второй .коммутатор и блок памяти, выход которого подключен к одному из входов сумматора, вход второго коммутатора соединен с выходом делителя напряжения, а один из выходов - с одним из входов блока памяти, выход блока выделения экстремума производной сигнала ошибки подключен ко входу усилителя и через первый коммутатор к одному из своих входов, выход. дифференциатора сигнала ошибки соединен с одним из входов блока выделения экстремума производной сигнала ошибку а выход логического блока подключен к одному из входов первого и второго коммутаторов. Источники информации, принятые во внимание при экспертизе 1.Теория систем с переменной структурой. Под рел. С.В.Емельянова, Наука, 1970, с. 325-335. 2.Двтс ское свидетельство СССР 402862/ кл. Q05 В 23/19. 08.06.71.

ftn.Z

ff

li.

,0

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящая система | 1980 |

|

SU1003016A2 |

| Датчик сил упругой деформации механизма и устройство для его настройки | 1985 |

|

SU1288511A1 |

| Противоблокировочное устройство для тормозной системы транспортного средства | 1973 |

|

SU622392A3 |

| Устройство для геологоразведки | 1979 |

|

SU807190A1 |

| Устройство для регулирования давления насоса | 1981 |

|

SU1012217A1 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1990 |

|

SU1818989A1 |

| Устройство для геоэлектроразведки | 1981 |

|

SU998994A1 |

| АВТОМАТИЗИРОВАННЫЙ КОМПЕНСАТОР | 1986 |

|

SU1841000A1 |

| Устройство для определения содержания углерода в жидком металле | 1985 |

|

SU1328747A1 |

| ЧАСТОТНО-РЕГУЛИРУЕМЫЙ АСИНХРОННЫЙ ЭЛЕКТРОПРИВОД | 2008 |

|

RU2401502C2 |

Авторы

Даты

1979-01-15—Публикация

1976-04-05—Подача