Изобретение относится к автома-. тическому управлению, может найти применение при управлении объектами, подверженными воздействию как параметрических, так и внешних возмущений .

По основному авт. св. № 642676 известна следяцая система, содержащая последовательно соединенные блок формирования сигнала ошибки и блок дифференцирования, выходы которых подключены к входам коммутатора, суммирующий усилитель и последовательно соединенные исполнительный орган и объект, первый выход которого подключен к первому входу блока формирования сигнала ошибки, выпрямитель, первый синхронный детектор, пороговый элемент, функциональный преобразователь и переключатель, входы которого подключены к выходам функционального преобразователя, блока формирования сигнала ошибки, блока дифференцирования и коммутатора, а выходы - к входам суммирующего усилителя, выход которого через пороговый элемент соединен с первым входом первого синхронного детектора, второй вход которого соединен с выходом выпрямителя, а выход - с входом исполнительного органа, связанного своим вторым выходом с входом функционального преобразователя, причем первый вход выпрямителя соединен с первым входом объекта, а второй вход - со вторым входом блока формирования сигнала ошибки 1.

Недостатком известной системы является ее низкое быстродействие.

10 Попытки увеличить быстродействие системы с помощью известных приемов приводят к резкому сокращению области устойчивости системы.

Целью изобретения является повы15шение быстродействия системы.

Поставленная цель достигаемся тем, что в системе дополнительно установлены компаратор и последовательно соединенные блок сигнатуры,

20 инвертор, второй синхронный детектор, блок памяти, сумматор, третий синхронный детектор и второй переключатель , выходы которого соединены с шестым и седьмым входами

25 суммирующего усилителя, выход коммутатора соединен с управляющими входами первого и второго переклю- . чателей через блок логики, первый вход компаратора соединен с выходом

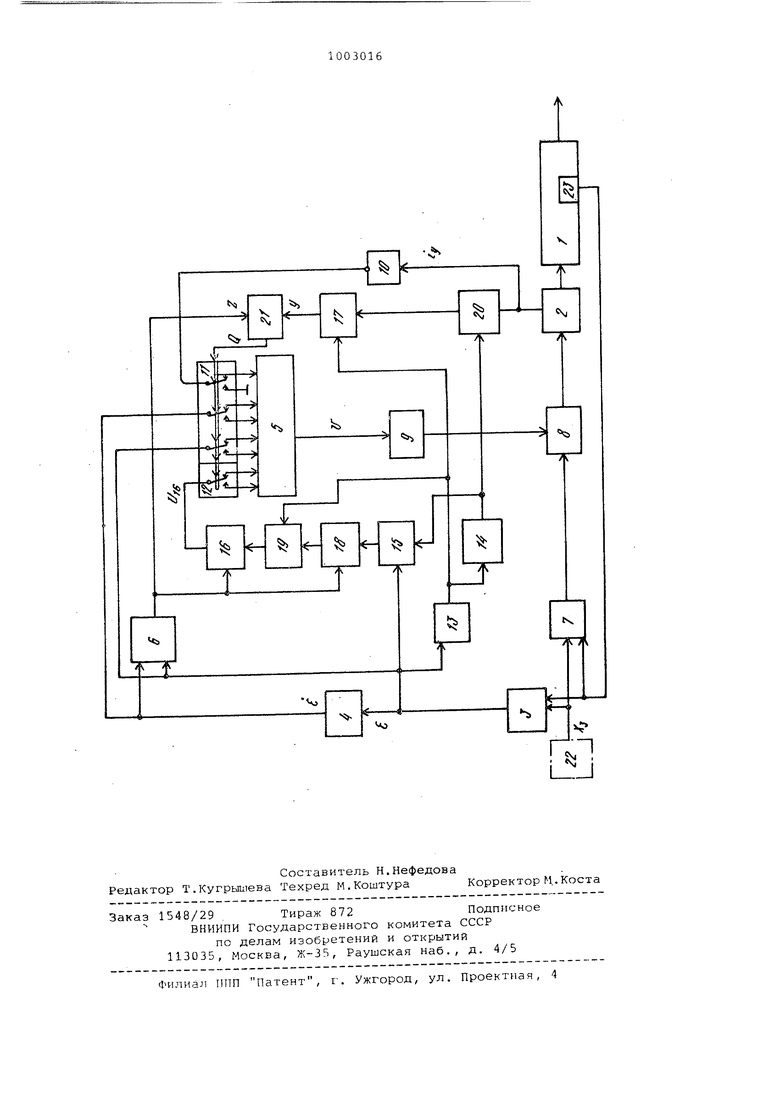

30 инвертора, второй вход - со вторым выходом ucnoJiiiHTejibn;;ro opLaiia, а выход через че1)зертык cnHxponHi.jft детектор соединен со иторым входо.м блока логики, вход блока ciiriiaryph: соединен с выходом блока формирова нкл сигнала ошибки и BTOPL-JM БХОДОМ второго синхронного детектора, а выход - со вторыми входами су.мматор и четвертого синхронно1чэ дс.гектора выход коммутатора соединеь с управляющим входом блока памяти и вторым входом третьего синхронного .детекто ра. На чертеже приведена функ1иональ ная схема системы. Система содержит объект 1 управл ния исполнительный орган 2 с нелинейной характеристикой типа насыщение, блок 3 формирования сигнала ошибки, дд;:фференциатО;, 4, су-.., усилитель 5 , коммута1ор 6 , иь;прямитель 7, первый синх1:;онн;.;й лстскиорпороговый элемент 9 , фуьп циоиаЛ1.Н1,1; преобразователь 10, первый и втсзрой переключатели 11 и 12 блок 13 си1на туры, инвертор 14, второй, -цветки и четвертый синхронн1,:е дстсктср:-; 15 - 17, блок 18 памятг , суммстгор ;1 компаратор 20, блок 21 логик;; , згщат чик 22 входного возддействйя, датч1 к 23 обратной Q - выход ной Сигнал блока 21 логики, входно воздействие, t - си1нал oii;;.:6iai, - сигнегд производимой ситяала ошибки, ток управд1ения мсполнительно1 о органа, V - сигна.п упра ления порогового э;1еме1гга , 1; - в;-:-ходной сигнал i-го бдюка, Z - выхо ной Сигнал коммутатора 6, Y - выход ной сигнал синхронного /детектора 17 Система работает следующим образом. При включении системы в работу з датчик 23 подает входное Бoз дeйcтви Х на вторые входы блока 3 формирования сигнад1а и выпрямителя На первые входы указанных (блоков поступает сигнал, пропорц -;ональный регулируемой координате, с диатчика 23 обратной связи, установд1е й1ого н объекте 1. На выходе блока 2 формируется сигнал Е ошибгси Ой,стем1.. Сигнал поступает на вход;ы ДИ(1;-ференциг1тора 4, блока 13 сигнатуры, синхронного детектора 15, коммутатора 6 и переключателя 11. На выход дифференциатора 4 формируется сигнал , пропорциональный производной от С1 гнала ошибки системы. Сигнал поступает на соответотвующие входы коммутатора 6 и переключателя 11. На выходе коммутатора 6 форми руется сигнал 7. в вйде Д1О1ического О, при выполнении с.).1едую11их уелов и и1- . JIP. Z О при 1 Е I Р -(1) 1Де fe. , t - некоторые |дороговые значе11ия, определяющие границы области в фазовом прострггистне систеь1ы. Бдюк 13 силнатуры определяет знак си1нала ошибки и формирует на своем S i gn в виде напряжения, 1:ропорционального знаку сигнала ошибки & . Сигнал выхода блока 13 сигнатуры поступает на (ОДИ1-1 из входов сумматора 19 и на вхОД 1-п верторс1 14 i-: та.м инвертируется. На 1ГГ-ЛХОДС инвертора 14 формируется сигнал и.(4- -signf, в виде напряжения со- знаком, обратным знаку с Г:;;- ла О1либки t . Сигнал U-)4 под1ается на nepBt.ie входы синхронного детект-ора 15 и компаратора 20. Синхроьппдй д eтeктop 15, осуществляющий удидОЖен;1е на знак, реализует опера1ДИ1-:. перемножени;- Сигналов Ug Е и и.ц -- - S i g п Е и на его выходе формйРуч -:-ея сшлдадь -15 (-sign ). Сигнал U-(5 поступает на вход блока 18 пам/:т, но не запоминается и на сто выхсзд не проходит потому, что :1: )а1 Ляющий ВХОД блока 18 памяти пос-гупает выходной сигнал коммутатора (Jf-j 0. На входы сумматора 19 Г1осту:даю-т сигналы и U ф-ормируется сигнал, равНдп U-jiij - siqnE, т.е. сигмал, пропорциональный знаку сигнала ошибк-и. Сигнал поступает на перj-lbi; дзход; синхронного детектора 16, осучцествляющего умножение на знак. Сипхронн;дй детектор 16 реализует огираци.ю перемножения сигналов и о19 - signE, На выходе синхронноIo детектора 16 формируется сигнал ., . signg . Сигнал Ц поступает на сигнальный вход коммутатора 12, выходные сигналы которого поддаются на соответствующие входы суг- 1у1ирую1:дего усилителя 5. Выходной сигнал комамутатора 62 0 поступает же на первый вход блока 21 логиТок управления iv. исполнительного органа поступает на вход функционального преобразователя 10 и на второй вход компаратора 20. Вид функцио- сального преобразования U)Q f(iy) 11реобразовг1телем 10 выбирается в зависимости от характеристик объекта 1 управления наличия и вида внешних и параметрических возмущений и требований к характеристикам системы. В ггростейшем случае преобразователь 10 ,;ожет иметь пропорциональную характеристику с коэффициентом пропорциональности равньп« единице, т.е. его пыходиой сигнал, T.e.U-n Сигнал -Ю у Ц поступает на соответствующий вход переключателя 11. На второй вход ком шратора 20 пос-тупает сигнал U в вид|.е напряжения со знаком, обратным знаку сигнала о1иибки Е системы. На выходе компаратора 20, осуществляющего сравнения входных сигналов U-)4 i- iy по релейному закону, формируется сигнал ( случае, если Ь -о 0 постоянная уставка, зависящая от параметров объекта 1 управления и требований к характеристикам системы. Сигнал U2Q поступает на один из вх дов синхронного детектора 17, на второй вход которого поступает сигнал ( выхода блока 13 сигнатуры. Синхронный детектор 17, осуществляющий умножение на знак, реализует опе рацию перемножения сигналов U sign6 и U2Q О и на его выходе формируется сигнал V J2oU-,3 0-signE. Сигнал поступает на второй вход блок 21 логики, на первый вход которого подается сигнал Z с коммутатора 6. На выходе блока 21 логики, реализующего итеративное логичес- кое управление вида Q.Z(Y + Q), формируется сигнал Q-H4+Q) + Oi05iQ ne+)0 Если в процессе работы системы н выходе блока 21 логики формируется низкий потенциал (т.е. логический сигнал О), то на выходной сигнал блока логики воздействует на переклю чатели 11 и 12 таким образом, что на входы усилителя 5 поступают сигналы , Е и постоянная уставка U со знаком, соответствующим знаку сигнала Е , что обеспечивается син хронным детектором 15. При этом уси литель 5суммирует указанные сигнал со своими весовыми коэффициентами и на выходе усилителя 5 формируется сигнал min где ke- . . f,,, . и Ч; . выбираютcmin Crmni Urnin irnin СЯ из требований к характеристикам си темы, в частности,Ч; может быть imin равен нулю. Сигнал V поступает на пороговый элемент 9, где сравнивается с некоторой пороговой величиной V, которая в частном случае может быть равна нулю. С выхода порогового уст ройства сигнал Ug поступает на вхо синхронного детектора 8, на второй вход которого поступает сигнал UT с выхода выпрямителя 7. Синхронный детектор 8, осуществляющий умноже.ние на знак, реализует операцию перемножения сигналов Ug и Ug . Пок сигнал V больше величины V , на и полнительный орган 2 действует разгоняющий форсирующий сигнал Ue cimas де сЦ,- максимальное значение коэфициента передачи выпрямителя 7. срабатывает пороговый элеент 9 и на исполнительный орган 2 оступает тормозящий сигнал этом случае система отрабатывает ходное воздействие в сторону меньшения ошибки , до тех пор, ока не будут выполнены условия .UE и ItUfe. В этом случае на ыходе коммутатора 6 формируется сигал Z в виде логической единицы,т.е. ifclife При этом на входы блока 21 логики, блока 18 памяти и синхронного детектора 16 подается сигнал Z 1. На выходе синхронного детектора 16 . формируется сигнал Ux((j Z-U g j1SiJ5nE , А сигнал и-|(на выходе синхронного детектора 16 меняет знак постоянной уставки, что приводит к изменению знака сигнала Ug на выходе порогового элемента 9 и на входе исполнительного органа 2. Одновременно в блоке 18 памяти по сигналу Z 1 происходит запоминание значения сигнала U-ij (.-5-icgn Е) . На выходе блока 21 логики формируется сигнал ((VB)Hfosi55r eH OsiCjnE+435 fb -)l При уменьшении сигнала разности U-,, - ivj ниже постоянной установки Од срабатывает компаратор 20 и формирует на своем выходе сигнал 1 (при iN,Uo). На выходе синхронного детектора 17 формируется сигнал . выходе блока 21 логики в этом случае формируется сигнал ()H l5i« n -H tSi4:neHHsic5n€-f)1 т.еГ сигнал логической единицы/ который исчезнет лишь при появлении на выходе коммутатора 6 сигнала Z О, После появления на выходе блока 21 логики сигнала Q 1 переключатели 11 и 12 коммутируют сигналы и,, Е , ё и ivy таким образом, чтобы на вход усилителя указанные сигналы поступали с новыми весовыми коэффициентами , и на выходе усилителя 5 формируется сигнал ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящая система | 1977 |

|

SU642676A1 |

| Реверсивный вентильный электродвигатель | 1983 |

|

SU1132329A1 |

| Интегрирующий привод переменного тока | 1984 |

|

SU1239683A2 |

| Следящая система | 1981 |

|

SU999014A1 |

| Следящая система | 1985 |

|

SU1290251A1 |

| Преобразователь значения коэффициента модуляции амплитудно-модулированного сигнала | 1983 |

|

SU1095106A2 |

| Электропривод переменного тока с бесконтактным тахогенератором | 1986 |

|

SU1411912A2 |

| Реверсивный асинхронный электропривод | 1988 |

|

SU1539951A1 |

| Цифроаналоговая следящая система | 1988 |

|

SU1580554A1 |

| Аналоговое мажоритарное устройство | 1982 |

|

SU1084989A1 |

Авторы

Даты

1983-03-07—Публикация

1980-08-08—Подача