I

Изобретение предназначено для аналоговых вычнсЛительных и измерительных устройств, требующих логического }а1равления сменой режимов.

Аналоговые (штеграторы с логическим управлением режимами посредством электронных ключей известаы и используются, например, в аналоговых машинах с периодазацией решения 11}.

Недостаток таких интеграторов заключается в невысокой точности интегрирования.

Наиболее близок к предложенному интегратор, содержащий дифф шшальный усилитель, выход которого через два последовательно соеданенных резистора начальных условий гюдключен к истоедику ншряжения начальных условий, общий вывод резисторов начальных условий через первый размьтающий ключ соеданен с инверсяым входом дифференциального усилителя, связанным через последовательно соединенные замыкающий ключ и интегрирующий конденсатор с выходам г фференциального усилителя, общ{ш вывод интегрирующего конденсатора и замыкающего ключа череЗвторой

размыкающий ключ соединен с шиной нулевого потенциала и через масштабные резисторы - со входами интегратора {2.

На сопрот1шлении замкнутого при вводе начальных условий ключа, соедакяющего обиош вывод масштабных резисторов и интегрирующего конденсатора обратной связи с шиной нулевого потенциала (зто сопротивление имеет величину порядка десятков или сотен Ом), создается падение напряжения от входных токов интегратора и тока зарядки конденсатора, и, как следствие, возникает ошибка в начальных условиях, что приводит к снижению точности интегрирования.

Целью изобретения является повьапение точ5ности интегрирования путем уменьшения погреш1ЮСТИ установки начальных условий.

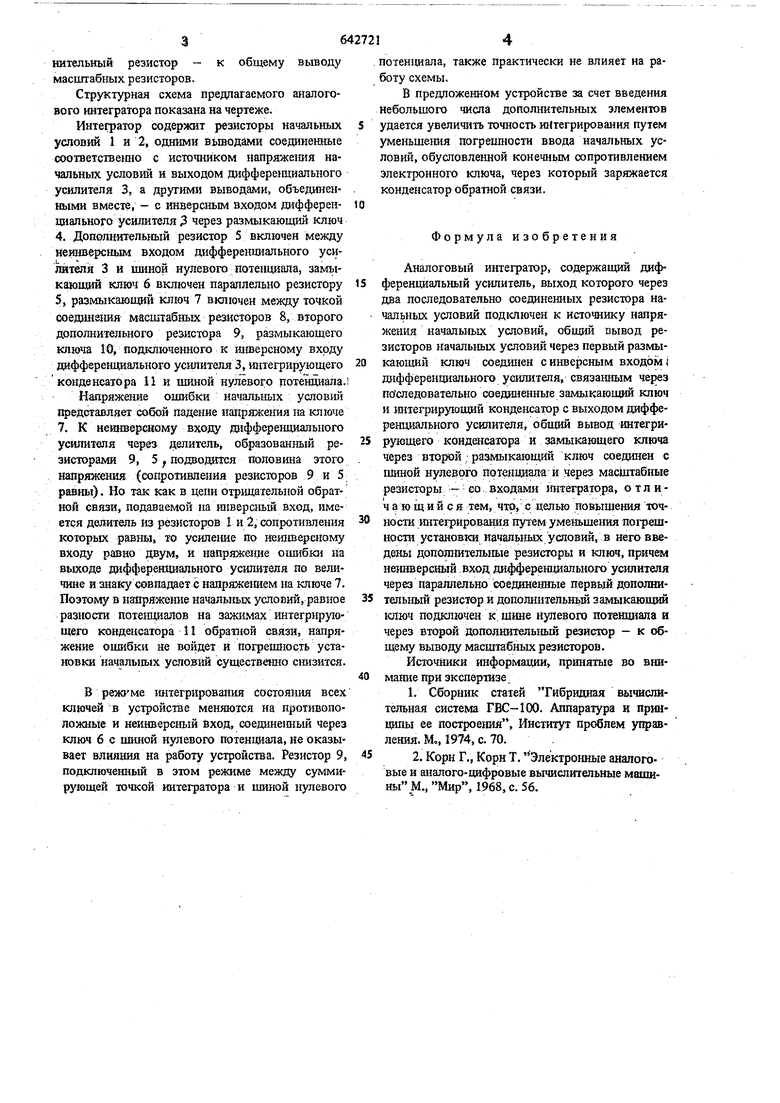

Это достигается тем, что в предлагаемый интегратор введены дополнительные резисторы и ключ, причем нешшершый вход дифференциального усилителя через параллельно соединенные первый дополнительный резистор и дополнительный замыкающий ключ подключен к шине нулевого потенциала и через второй дополк общему выводу нительнын резистор масштабных резисторов. Структурная схема предлагаемого аналогового интегратора показана на чертеже. Интегратор содержит резисторы началыат условий 1 и 2, одними вьшодами соединешше соответствешо с источником напряжения начальных условий и выходом дифферевдиального усилителя 3, а другими выводами, объединенными вместе, - с инверс1П 1М входом дифференциального усилителя 3 через размыкающий ключ 4.Дополнительный резистор 5 включен между иещлзерсным входом дифференциального усилителя 3 и шиной нулевого потенциала, замъ1кающий ключ 6 включен нараллельно резистору 5,размыкающий ключ 7 включен между точкой соединзшм масштабных резисторов 8, второго дополнительного резистора 9, размыкающего ключа 10, подключенного к инверсному входу дифференциального усилителя 3, интегрирующего конденсатора 11 и шиной нулевого потенциала. Напряжение ошибки начальных усяовш ирейставляет собой падение напряжения ш ключе 7. К нешшерсиому входу щгфферендиального усилителя через делитель, образованный резисторами 9, 5 подводится йоловина этого напряжения (сопротивления резисторов 9 и 5 равны). Но так как в цеии отр1щахельной обратной связи, подаваемой па инверсный вход, имеется делитель Из резисторов Д и 2, сопротивлештя которых равны, то усиле1ше ио нешшерсному входу равно двум, и напряжение ошибки на выходе дифферекциального усилителя по величине и знаку совпадает с напряжением на ключе 7. Поэтому в напряжение начальных условий, равное разности потенциалов на зажимах интегрирующего конденсатора П обратной связи, напряжение ошибки не войдет и погрепиюсть установки начальных условий существенно снизится. В реж}ме 1штегрирования состояния всех ключей в устройстве меняются на противоположные и неинверсный йход, соешшешый через ключ 6 с нотой нулевого потендаала, не оказывает влияния на работу устройства. Резистор 9, подключеннь1Й в этом режиме между суммирующей точкой интегратора и щиной нулевого потенциала, также практически не влияет на работу схемы. В предложенном устройстве за счет введения небольщого числа дополнительных элементов удается увеличить точность интегрирования путем уменьщегаш погреишости ввода начальных условий, обусловленной конечньхм сопротивлением электронного ключа, через который заряжается конденсатор обратной связи. Формула изобретения Аналоговый интегратор, содержащий дифференщ1альный усилитель, выход которого через два последовательно соединенных резистора начальных условий подключен к источнику напряжения начальщ 1х условий, общшЧ вывод резисторов началышк условий через первый размыкающий ключ соединен с инверсным входом i дифференциального уеилитепя, связанным через последовательно соединенные замыкающий ключ и штегрирующий конденсатор с выходом дифференциального усилителя, общий вывод интегрирующего конденсатора и замыкающего ключа через второй. размыкающий ключ соедашен с оашой нулевого потенциала и через масщтабные резисторы - со .входами интегратора, отличающий ся тем, что, с целью повышения точности интегрирования путем уменьщетш погрещности установки началь1 ых условий, в него введены дополнительные -резисторы и ключ, причем неинверсный вход дифферешщального усилителя через параллельно еоединедаые первый дополнительный резистор и дополнительньш замыкающий ключ подключен к. шине нулевого потенциала и через второй дополНителышш резистор - к общему выводу масщтабных резисторов. Источники информации, принятые во внимание при экспертизе 1. Сборник статей Гибридная амчислительная система FBC-100. Аппаратура и принципы ее nocTpoeinoi, Институт проблем управления. М,, 1974, с. 70. 2. Корн Г., Корн Т. Электронные аналоговые и аналого-цифровые вычислительные машины М., Мир, 1968, с. 56.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор | 1983 |

|

SU1088017A1 |

| Аналоговый интегратор | 1979 |

|

SU834714A1 |

| Интегратор | 1979 |

|

SU834715A1 |

| Интегратор | 1980 |

|

SU928369A1 |

| Интегратор | 1983 |

|

SU1198546A1 |

| Времяимпульсный квадратичный преобразователь | 1986 |

|

SU1406610A1 |

| Интегратор | 1984 |

|

SU1161963A1 |

| ИНТЕГРАТОР С ОБНУЛЕНИЕМ | 1991 |

|

RU2015556C1 |

| ИНТЕГРАТОР | 1990 |

|

RU2020580C1 |

| Интегратор | 1986 |

|

SU1401485A2 |

Авторы

Даты

1979-01-15—Публикация

1977-07-26—Подача