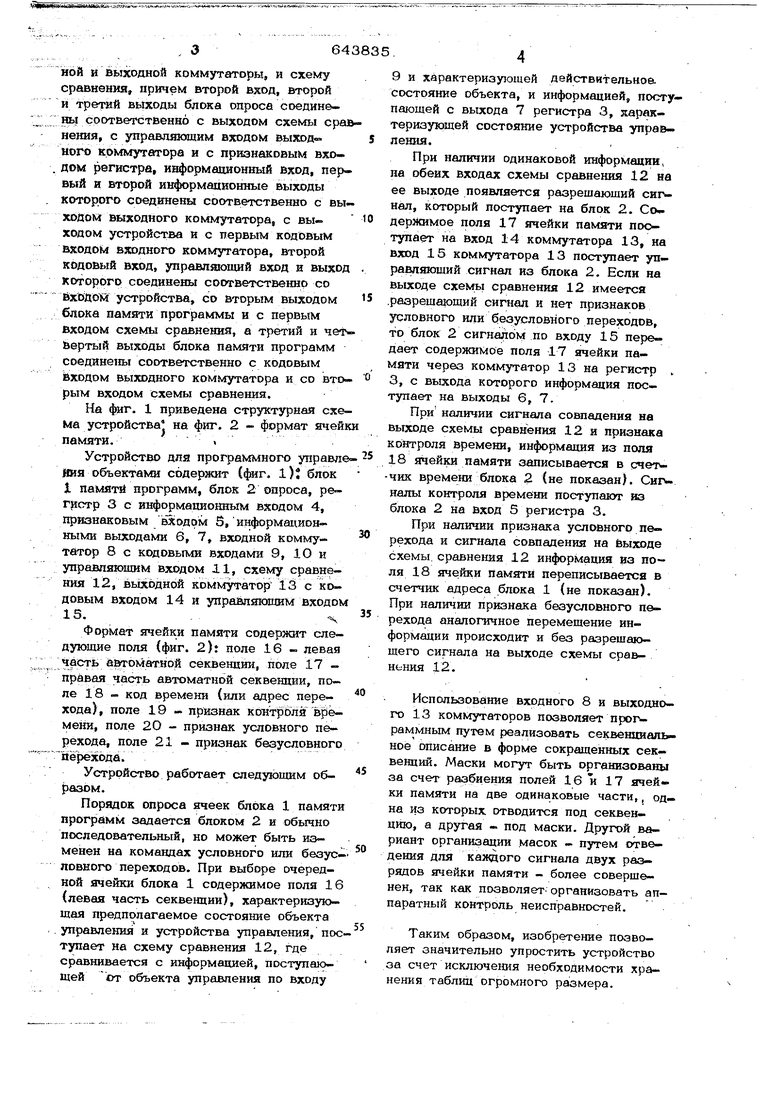

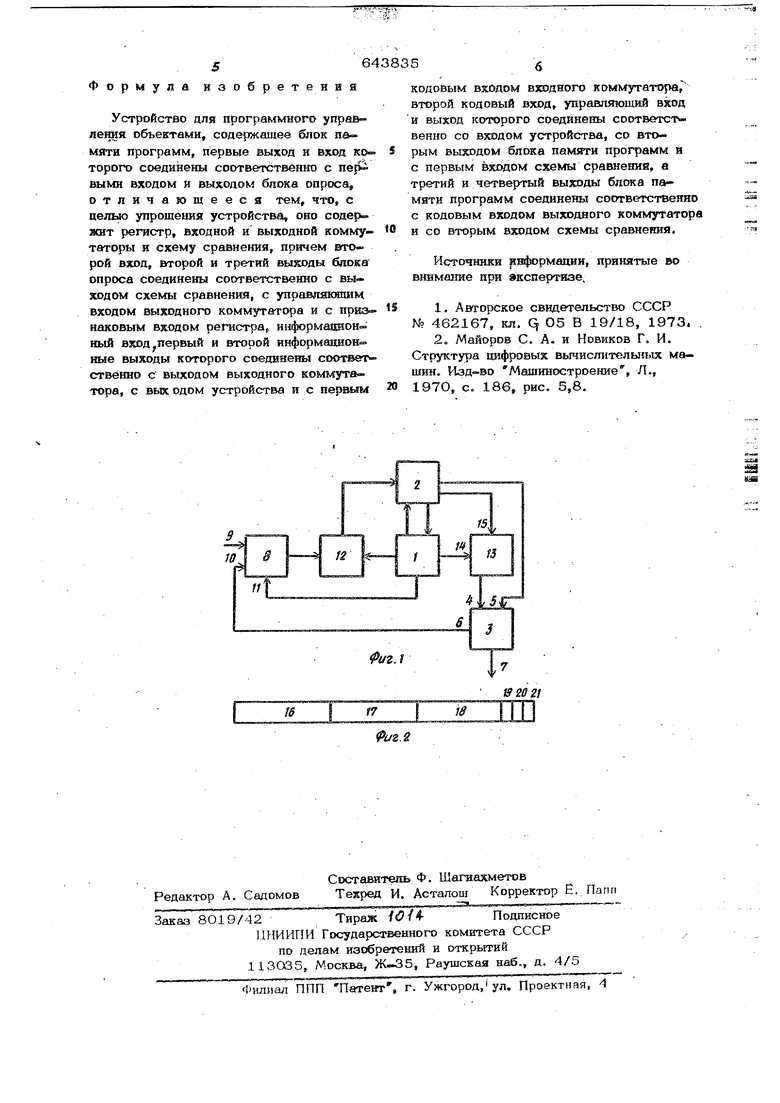

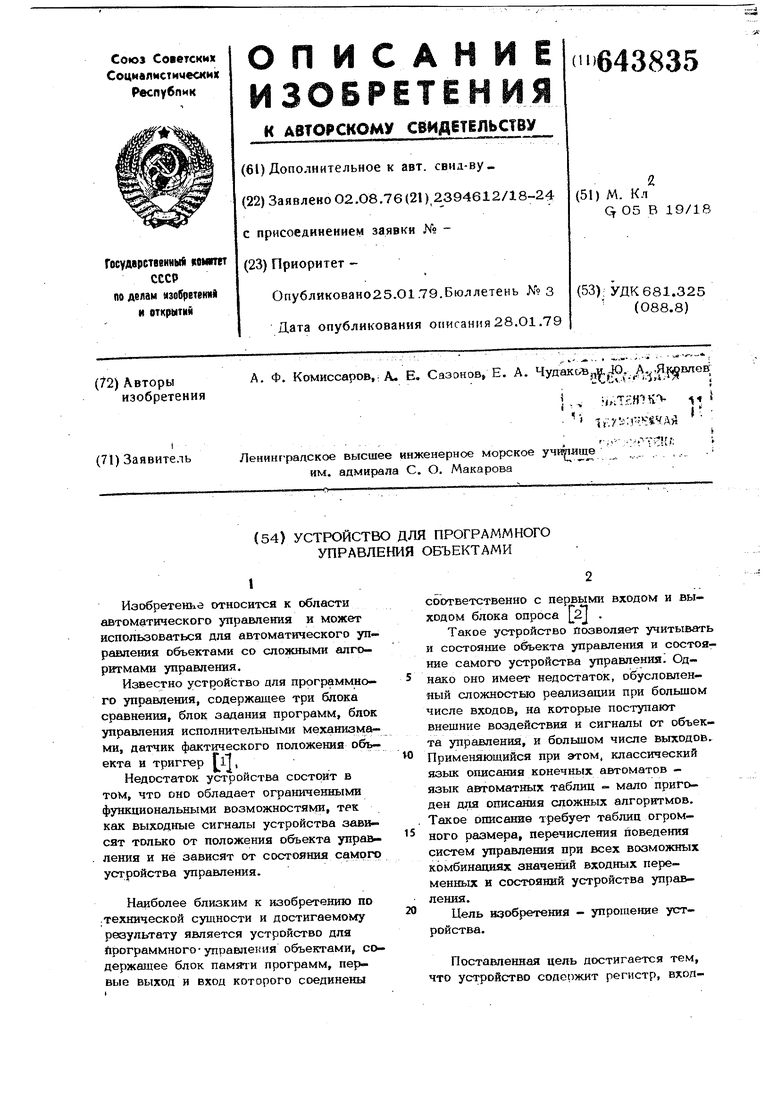

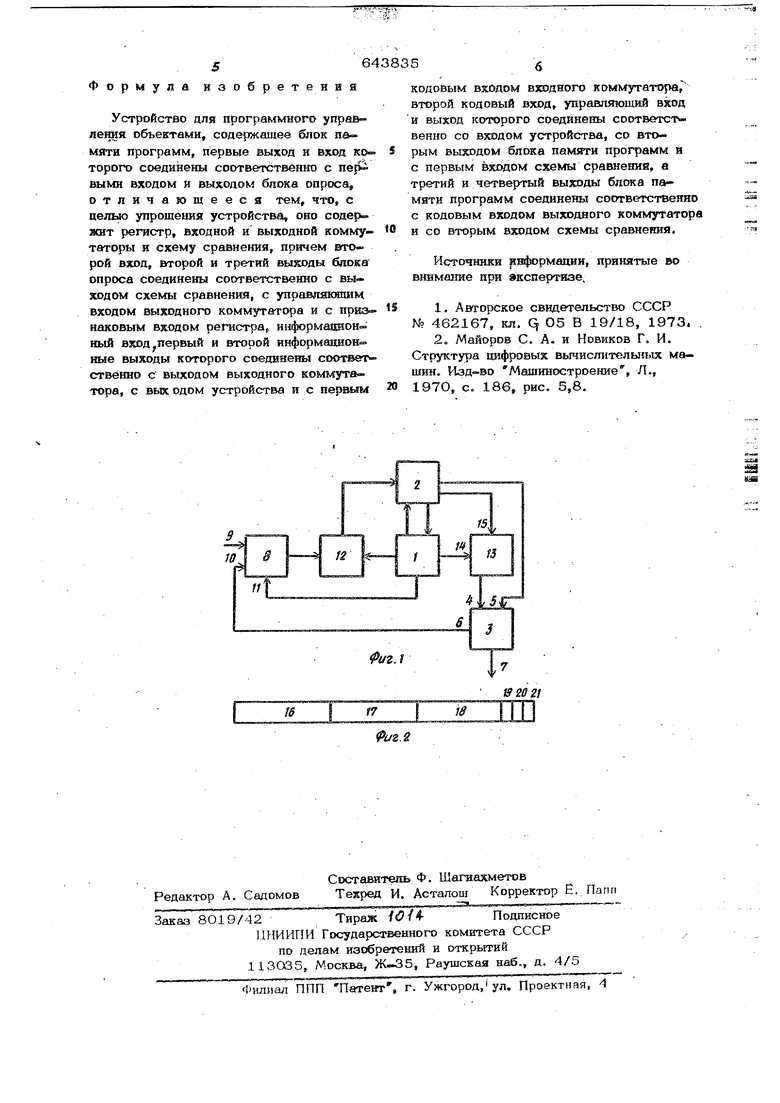

(54) УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ОБЪЕКТАМИ ,364 ной и выходной коммутаторы, и схему сравнения, причем второй вход, второй и третий выходы блока опроса соедннеНЬ1 соответственно с выходом схемы сра нения, с управляющим входом выход кого коммутатора и с признаковым входом регистра, информационный вход, первый и второй ин рмационные выходы которого соединены соответственно с вы ходом выходного коммутатора, с выходом устройства и с первым кодовым входом входного коммутатора, второй кодовый вход, управпшоншй вход и выход которого соединены соответственно со йходом устройства, со вторым выходом блока памяти программы и с первым входом схемы сравнения, а третий и чет вертый вызшды блока памяти программ соедине1а1 соответственно с кодовым 1бходом выходного коммутатора и со вто рым входом схемы сравнения. На г. 1 приведена структурная схе ма устройства на фиг. 2 - формат ячей памяти. Устройство для программного управл В1Я объектами содержит (фиг. l)J блок 1 памяти программ, блок 2 опроса, ре- грстр 3 с информационным входом 4, признаковым входом 5, информационными выходами 6, 7, входной коммутатор 8 с кодовыми входами 9, 10 и управляющим входом 11, схему сравнения 12, выходной коммутатор 13 с кодовым входом 14 и упра1влшопшм входом 15.-ч Формат ячейки памяти содержит следующие поля (фиг. 2); поле 16 - левая часть, автоматной секвенции, поле 17 правая часть автоматной секвенции, поле 18 - код времени (или адрес перехода), поле 19 - признак коитрЬля времени, поле 20 - признак условного перехода, поле 21 - признак безусловного перехода. Устройство работает следующим образом. Порядок опроса ячеек блока 1 памят программ задается блоком 2 и обычно последовательный, но может быть изменен на командах условного или безус ловкого переходов. При выборе очередной ячейки блока 1 содержимое поля 16 (левая часть секвенции), характеризующая предполагаемое состояние объекта . управлетш и устройства управления, по тупает на схему сравнения 12, где сравнивается с информацией, поступающей от объекта управления по входу 9 и характеризующей действительноа состояние объекта, и информацией, поступающей с выхода 7 регистра 3, характеризующей состояние устройства управления. При наличии одинаковой информации, на обеих входах схемы сравнения 12 на ее выходе появляется разрещающий сигнал, который поступает на блок 2. Содер39шмое поля 17 ячейки памяти поступает на вход 14 коммутатора 13, на вход 15 коммутатора 13 поступает управляющий сигнал из блока 2. Если на выходе схемы сравнения 12 имеется .разрешающий сигнал и нет признаков условного или безусловного переходов, то блок 2 сигналом по входу 15 передает содержимое поля 17 ячейки памяти через коммутатор 13 на регистр , 3, с выхода которого информация поступает на выходы 6, 7. При наличии сигнала совпадения на выходе схемы сравнения 12 и признака контроля времени, информация из поля 18 ячейки памяти записывается в счет чик времени блока 2 (не показан). Сигналы контроля времени поступают из блока 2 на вход 5 регистра 3. При наличии признака условного перехода и сигнала совпадения на быходе схемы сравнения 12 информация из поля 18 ячейки Памяти переписывается в счетчик адреса блока 1 (не показан). При наличии признака безусловного перехода аналогичное перемещение информации происходит и без разрешающего сигнала на выходе схемы сравнения 12. Использование входного 8 и выходного 13 коммутаторов позволяет программным путем реализовать секвенциальное описание в форме сокращенных секвенций. Маски могут быть организованы за счет разбиения полей 16 и 17 ячейки памяти на две одинаковые части,, одна из которых отводится под секвенцию, а другая - под маски. Другой вариант организации масок - путем отведения для казкдого сигнала двух разрядов ячейки памяти - более совершенен, так как позволяет- организовать аппаратный контроль неисправностей. Таким образом, изобретение позволяет значительно упростить устройство за счет исключения необходимости хранения таблиц огромного размера. Формула р е т е н и я Устройство для программного управ ления объектами, содержащее блок памяти программ, первые выход и вход кр торого соединены соответственно с nefSi выми входом и выходом блока опроса, отличающееся тем, что, с целыо упрощения устройства, оно содержит регистр, входной и выходной коммутаторы и схему сравнения, причем второй вход, второй и третий выкоды блока опроса соединены соответственно с выходом схемы сравнения, с управлякшшм входом выходного коммутатора и с приз наковым входом регистрвр иliфopмalшoн ный вхоДуПервый и второй информа шон ные выходы которого соединены соответ ственно с выходом выходного коммута- тора, с вых одом устройства и с первым 64 5 кодовым входом взсодного коммутатора, второй кодовый вход, управляющий вход и выход которого соединены соответсть. венно со входом устройства, со вторым выходом блока памяти программ в с первым входом схемы сравнений, а третий и четвертый выходы блока памяти программ соединены соответственно с кодовым входом выходного коммутатора и со вторым входом схемы сравнения. Источники 1ввформации, принятые во внимание при акспертизе, 1. Авторское свидетельство СССР NO 462167, кл, q О5 В 19/18, 1973. , 2., Майоров С. А. и Новиков Г. И. Структура цифровых вычислительных машин. Изд-во Машиностроение, Л., 197О, с. 186, рис. 5,8.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления объектом | 1973 |

|

SU472332A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Устройство для программного управления технологическими процессами | 1979 |

|

SU877476A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Устройство управления цифровой вычислительной машины | 1971 |

|

SU437074A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для вывода информации | 1984 |

|

SU1180876A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

Авторы

Даты

1979-01-25—Публикация

1976-08-02—Подача