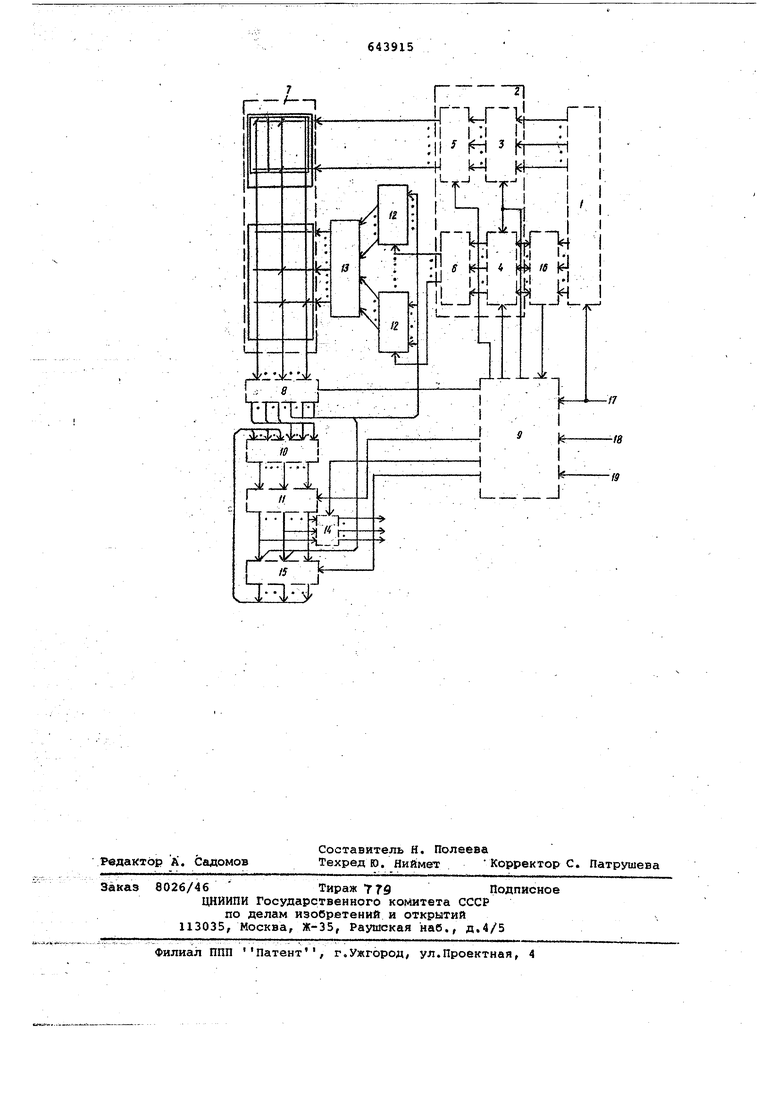

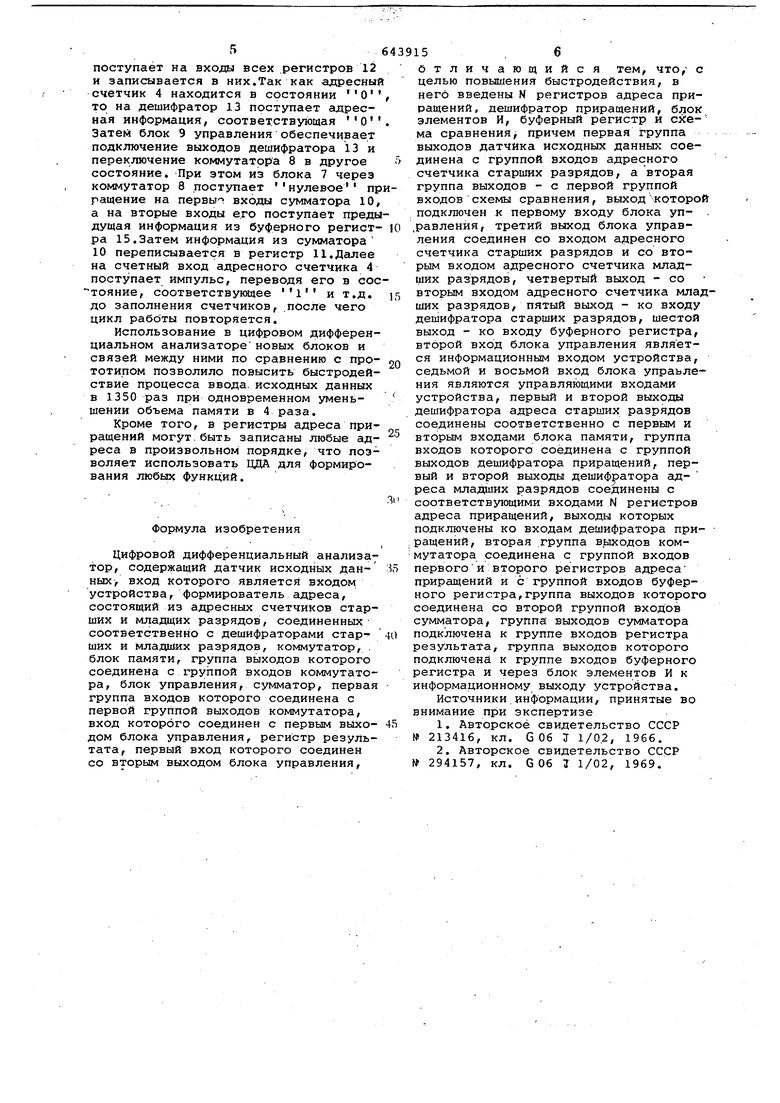

(54) ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ АНДЛИЗАТОР младших разрядов, четвертый выход Со вторым входом адресного счетчика Младших разрядов, пятый выход - ко входу дешифратора старших разрядов, шестой выход - ко входу блока буферного регистра, второй вход блока управления является информационным входом устройства, седьмой и восьмой вход блока управления являются управляющими входами устройства, первый и второй выходы дешифратора адреса разрядов соответственно с .первым и вторым входами блока памяти, группа входов которого соединена с группой выходов дешифратора прира1цений, первый и второй выходы дешифратора адреса младших разрядов соединены с соответствующими входами N регистров адреса приращений, выходы которых ПС ;ключены ко входам дешифратора приращений, вторая группа выходов коммутатора -соединена с входов первого и второго регистров адреса приращений и с группой входов буферного регистра группа выходов которого соеда1нена со второй группой входов сумматора, группа выходов сумматора подключена к группе входов регистра результата,группа выходов которого подключена к группе входов буферного регистра и через блок элементов И к информационному выходу устройства. На чертеже представлена блок-схема устройства. Цифровой дифференциальный анализатор содержит датчик 1 исходных данных формирователь 2 адреса, который содер жит адресный счетчик 3 старших разрядОв, адресный счетчик 4 младших разря дов, дешифратор 5 старших разрядов, Дешифратор i. младших разрядов, блок 7 памяти, коммутатор 8, блок 9 управления, сумматор 10, регистр 11 результата, регистры 12.,, 12 адреса приращений, дешифратор 13 приращений, блок 14 элементов И, буферный регистр 15, схема 16 сравнения, информационный вход 17, управляющие входы 18,1.9. .Устройство работает следующим образом. , При подаче внешнего импульса останов по входу 19 регистры 11, 15, адресные счетчики 3,4 устанавливаются в нулевое положение, а генератор блока 9 управления блокируется. При подаче внешнего импульса -запуск по входу 18 подключается генератор блока 9 управления,Ьбёспечивакмдий формирование на выходе его ймНульсов для управления последовательностью работы ЦДА. Сначала подключае Гся выход дешифратора 5 и из зоны старших разрядов блока 7 информация (нулевая) поступает через коммутатор 8 на старшие разряды буферного регистра 15, а из зоны адреса приращений информация обо всех адресах .дли. данного положения.адресного счетчика 3 через коммутатор 8 поступает на входы N регистров 12 , и записывается в них. Так как адресный счетчик 4 находится в нулевом состоянии, то на дешифратор 13 поступает адресная информация, соответствующая О. Затем блок 9 управления обеспечивает подключение выходов дешифратора 13, При этом из блока 7 через коммутатор 8 поступает нулевое приращение на первые входы сумматора 10, а на вторые входы его поступает информация из буферного регистра 15 (нулевая ), Затем информация из сумматора 10 переписывается в регистр 11 результата (блок 14 может отключаться только.при вводе исходных данных). Далее приходит импульс на счетный вход адресного счетчика 4, переводя его в первое положение. При этом блок 9 управления обеспечивает отключение выходов дешифратора 5 и подключение вь ходов коммутатора 8 к первым входам сумматора 10 до возникновения импульса на счетном входе адресного счетчика 3. В адресный счетчик 4 записана , Что обеспечивает подключение выходов первого регистра адреса Приращений I2,j ко входам дешифратора 13. Затем блок 9 управления обеспечивает подключение выходов дешифратора 13 и перезапись из регистра 11 в буферный регистр 15. При этом из блока 7 через коммутатор 8 поступает приращение функции на первые входы сумматора 10, а. на вторые входы его поступает предыдущая информация с выхода буферного регистра 15..Затем новое значение функции переписывается . в регистр 11 и формируется новый импульс на счетном входе адр ;сного счетчика 4, переводя его во второе состояние, что обеспечивае.т посредствдм дешифратора 6 подключение выходов второго, регистра адреса приращений 122 ко входу дешифратора 13. Затем блок 9 управления обеспечивает подключение выхсэдов дешифратора 13 и перезапись из регистра 11 в буферный регистр 15. При этом из блока 7 через коммутатор 8 поступает приращение функции на первые входы сумматора I О, а на вторые входы его поступает предыдущая информация с выхода буферного регистра 15. Затем новое значение функции переписывается is регистр 11 и формируется новый импульс на счетном входе адресного счетчика4, переводя его в третье состояние и т.д. до тех пир, пока.не возникнет:импульс на счетном входе адресного счетчика 3. При этом регистры 12 и адресный счетчик 4 обнуляются, Затем подключается выход дешифратора 5 и из зоны старших разрядов блока 7 информация поступает ерез коммутатор 8 на старшие разряды буферного регистра 15, а из зоны адеса приращений 7 информация обо всех. адресах для данного положения адресного счетчика 3 через коммутатор 8 поступает на входы всех .регистров 12 и записывается в них.Так как адресный счетчик 4 находится в состоянии О то на дешифратор 13 поступает адресная информация, соответствующая О Затей блок 9 управления обеспечивает подключение выходов дешифратора 13 и переключение коммутатора 8 в другое состояние. При этом из блока 7 через коммутатор 8 поступает нулевое пр ращение на первы входы сумматора 10, а на вторые входы его поступает преды дущая информация из буферного регистра 15.Затем информация из сумматора 10 переписывается в регистр 11.Далее на счетный вход адресного счетчика 4 поступает импульс, переводя его в сос -тояние, соответствуквдее i и т.д. до заполнения счетчиков, .после чего цикл работы повторяется. Использование в цифровом дифференциальном анализатореновых блоков и связей между ними по сравнению с прототипом позволило повысить быстродействие процесса ввода, исходных данных в 1350 раз при одновременном уменьшении объема памяти в 4 раза. Кроме того, в регистры адреса приращений могут.быть записаны любые адреса в произвольном порядке, что позволяет использовать ЦДА для формирования любых функций. Формула изобретения Цифровой дифференциальный анализа7 тор, содержащий датчик исходных данных, вход которого является входом устройства, формирователь адреса, состоящий из адресных счетчиков старших и младщих разрядов, соединенных соответственно с дешифраторами стар ших и младших разрядов, коммутатор, . блок памяти, группа выходов которого соединена с группой входов коммутатора, блок управления, сумматор, первая группа входов которого соединена с первой группой выходов коммутатора, вход которого соединен с первым выходом блока управления, регистр результата, первый вход которого соединен со вторым выходом блока управления. Отличающийся тем, что/ с целью повышения быстродействия, в него введены N регистров адреса приращений, дешифратор приращений, блок элементов И, буферный регистр и сЯема сравнения причем первая группа выходов датчика исходных данных соединена с группой входов адресного счетчика старших разрядов, а вторая группа выходов - с первой группой входов схемы сравнения, выход которой подключен к первому входу блока уп.равлеиия, третий выход блока управления соединен со входом адресного счетчика старших разрядов и со вторым входом адресного счетчика младщих разрядов, четвертый выход - со вторым входом адресного счетчика младших разрядов, пятый выход - ко входу дешифратора старших разрядов, шестой выход - ко входу буферного регистра, второй вход блока управления является информационным входом устройства, седьмой и восьмой вход блока управления являются управляющими входами устройства, первый и второй выходы дешифратора адреса старших разрядов соединены соответственно с первым и вторым входами блока памяти, группа входов которого соединена с группой выходов дешифратора приращений, первый и второй выходы дешифратора адреса младших разрядов сое;цинены с соответствующими входами N регистров адреса приращений, выходы которых подключены ко входам дешифратора приращений, вторая .группа в.ыходов коммутатора соединена с группой входов первогои второго регистров адреса приращений и с группой входов буферного регистра,группа выходов которого соединена со второй группой входов сумматора, группа выходов сумматора подключена к группе регистра результата, группа выходов которого подключена к группе входов буферного регистра и через блок элементов И к информационному выходу устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 213416, кл. G Об J 1/0.2, 1966. 2.Авторское свидетельство СССР № 294157, кл. G06 Т 1/02, 1969.

G

-Т

Г

ir-vr K--T-J

:ii I :i I ;| N И- И M-

if-

т I

m

I

п.1 М -I I

6 Ш Ш fe . J I .1 И Il

L-f JLA-J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство буферизации команд процессора | 1983 |

|

SU1092506A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| Цифровой кусочно-линейный аппроксиматор | 1988 |

|

SU1615743A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

| Устройство для программного управления | 1990 |

|

SU1807449A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| УСТРОЙСТВО ДЛЯ СОКРАЩЕНИЯ ИЗБЫТОЧНОСТИ ИЗМЕРИТЕЛЬНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2007760C1 |

| Устройство для ввода и вывода динамически изменяющейся информации | 1982 |

|

SU1115043A1 |

n

ф,

Г fO 1

tI

Jf Jf sL. Г // k

-J

:

/Г / UQZ

n T-/7

-W

f9

j

Авторы

Даты

1979-01-25—Публикация

1974-10-08—Подача