Изобретение относится к контрольноизмерительной технике, в частности к технике программируемых тестовых исг пытаний микроэлектронных логических схем,может быть использовано для регулировки, контроля правильности функционирования и контроля электрических параметров микроэлектронньтх логических схем вычислительной техники.

Известно устройство для контроля микроэлектронных логических схем, содержащее блок управления, входной, выходной и запоминающий регистры, npoiv. раммируемый блок питания, амплитудный селектор, цифровой блок сравнения, формирователь входных сигналов, блок запуска, индикации, цифропечатаю- щий блок, блок ввода и вывода, временной селектор, управляемый элемент за« держки l .

Недостатком этого устройства являет ся возможность выхода его из строя или повреждения проверяемой микроэлектронной логической схемы в случае, если к

выходам формирователей входных сигналов устройства подключаются выходы проверяемой схемы.

С целью повьпцения надежности, в известное устройство для контроля микроэлектронных логических схем по авт. св. № 273342 ввейен блок ковггроля ; коммутаторов входов, цричем его информацио шые входы соответственно соединены с выходами блока формирователей входных сигналов, управляющий вход соединен с одним из Выходов блока управления, первый выход - с одним из управаляющих входов блока формирователей входных сигналов, а его второй выходс одним из входов цифропечатающего блока.

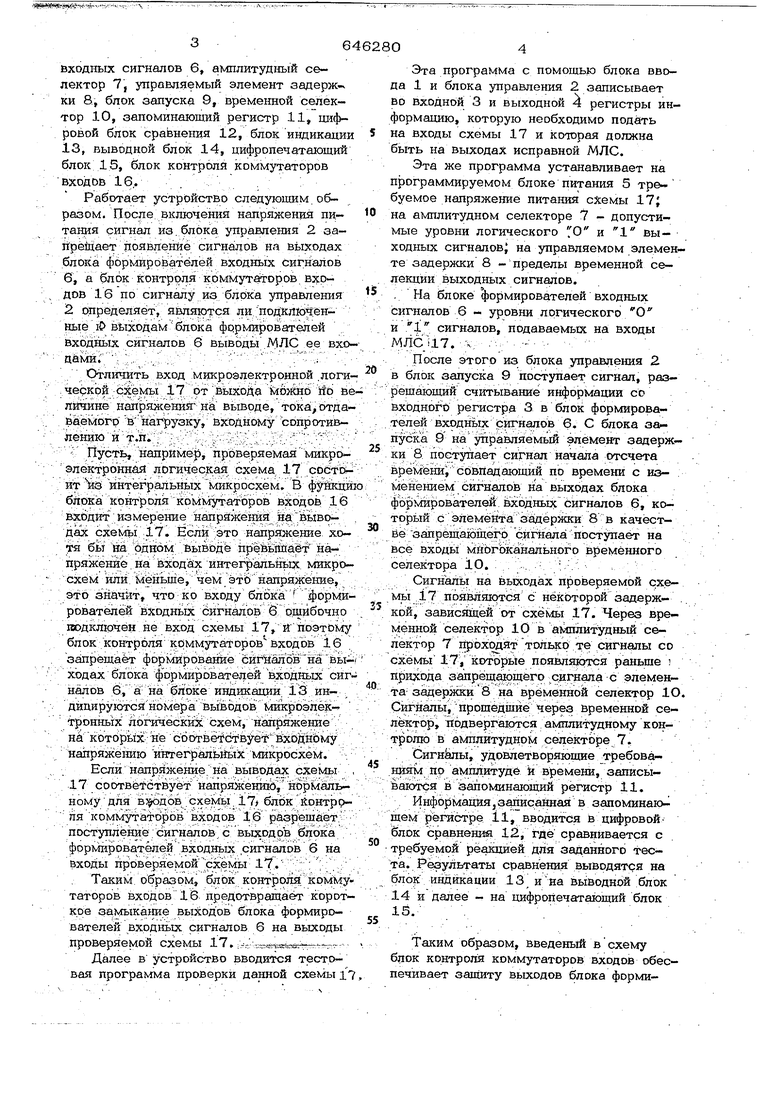

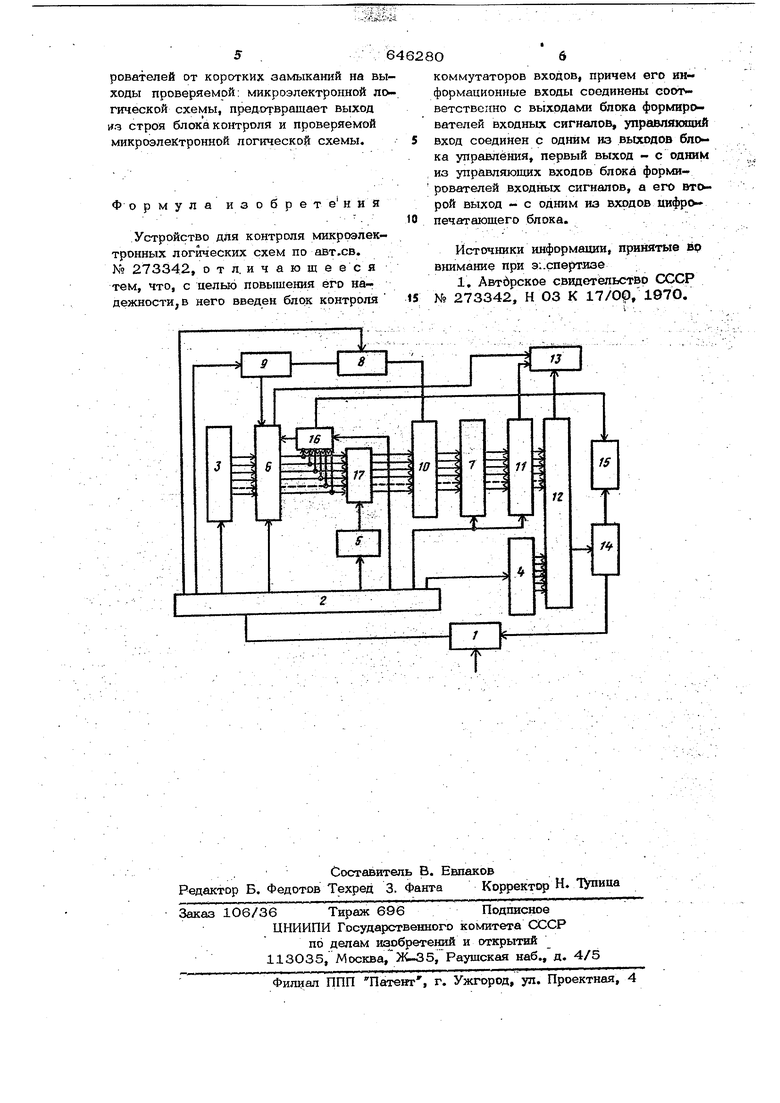

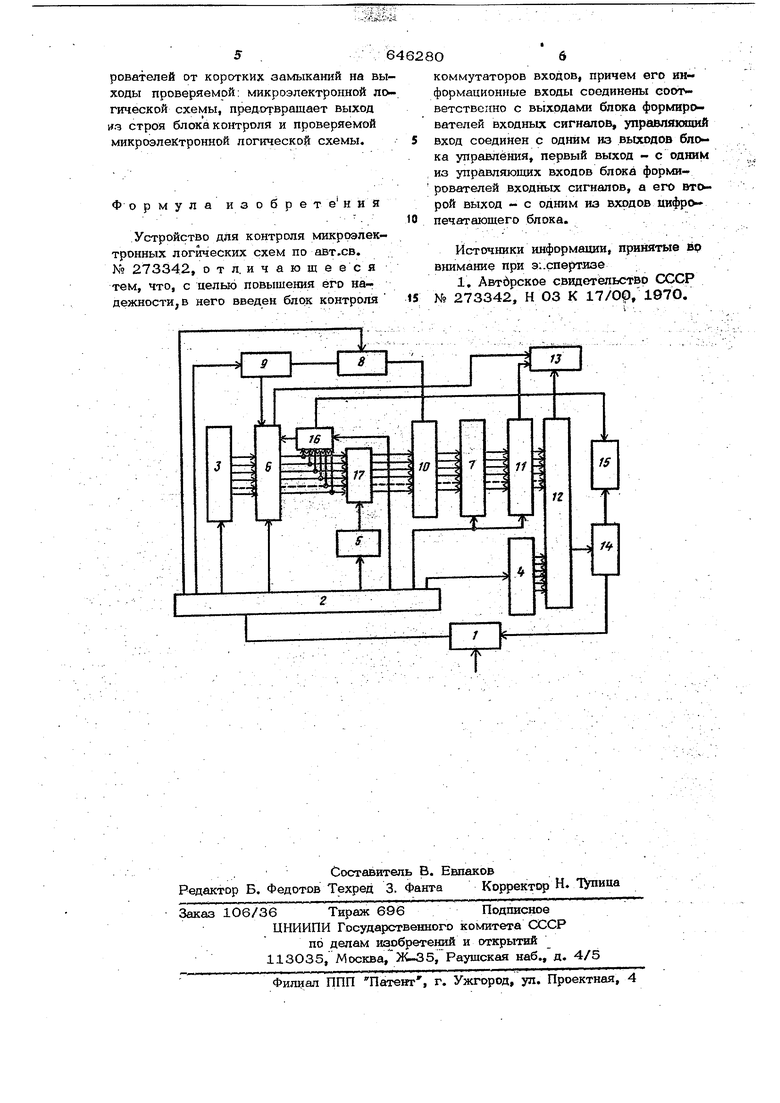

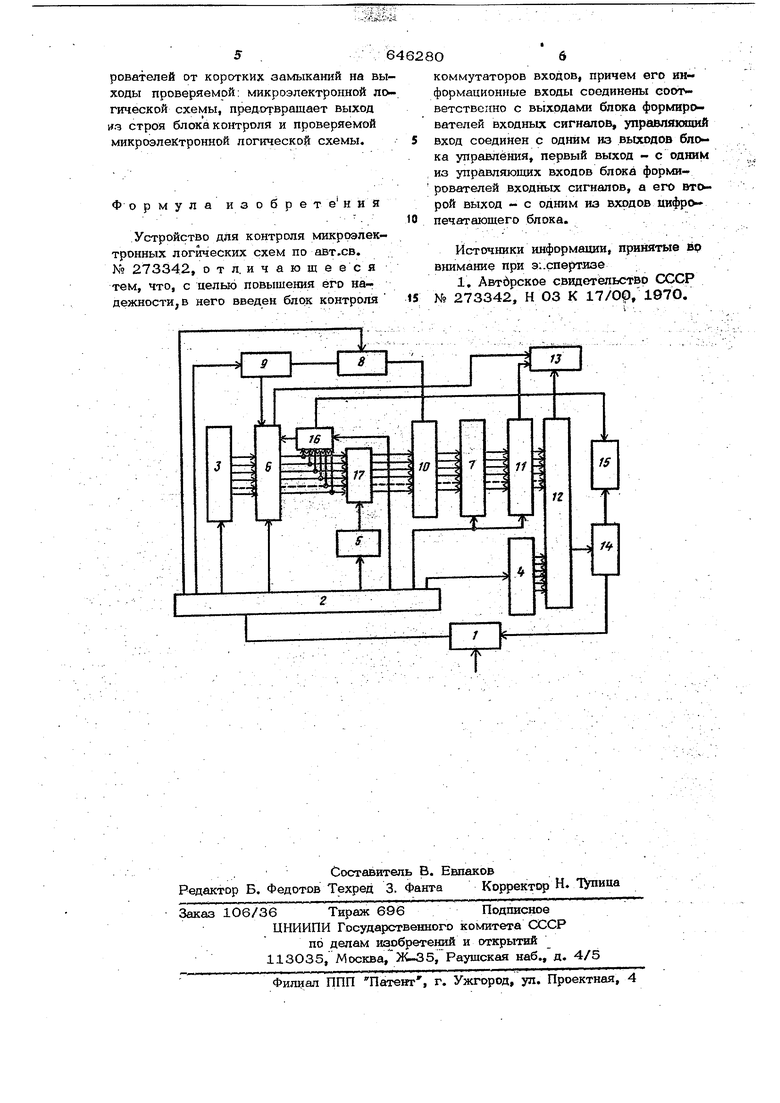

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Устройство содержит блок ввода 1, блок управления 2, входной регистр. 3, выходной регистр 4, программируемый блок питания 5, блок формирователей

646280 входных сигналов 6, амнлитудный селектор 7, управляемый элемент задерж-v ки 8, блок запуска 9, временной селектор 10, запоминающий регистр 11, цифровой блок сравнения 12, блок индикации 13, выводной блок 14, цифропечатающий блок 15, блок контроля коммутаторов ВХОДОВ 16.,. Работает устройство следующим образом. После включения напряжения питашя сигнал из. блока управле шя 2 запрей аетцоявленйё сигналов на выходах блока формирователей входных сигналов 6, а блок йонтроля коммутаторов входов 16 по сигналу из блока управления 2 определяет, являются ли подключенные lO выходам блока формирователей (входных сигналов 6 выводы МЛС ее входами. Отличить вход микроэлектронной логи ческой схемы 17 от выхода можно Яо ве личине напряжения на выводе, тока отдава.емогр в нагрузку, входному сопротивлению и т.п..Пусть, например, проверяемая микроэлектронная логическая схема 17 состоит из интегральных микросхем. В функци блока контроля коммутаторов входов 16 входит измерение напряжения на выводах схемь 17. Если это напряжение хотя бы на одном Выводе превышает напряжение на вх:ода1Х интегральньгх микросхем или. меньше, чем это напряжение, это значит, что ко входу блока формирователей входных сигналов 6 ошибочно гаодключен не вход схемы 17, и поэтому блок контроля коммутатороввходов 16 запрещает формирование сигналов на вы- ходах блока формирователей входных сиг налов 6, а на блоке индикации 13 индицируются номера выводов микроэлектронных логических схем, напряжение на которых не соответствует вхо з:ному напряжению интегральйых микросхем. Если напряжение на выводах схемы 17 соответствует напряжению, нормальному для схемы 17 блок йонтррпя коммутаторов входов 16 разрешает поступление сигналов с выходов блока формирователей входных сигналов 6 на входы проверяемой схемы 17. Таким образом, блок контроля комму таторов входов 16 предотвращает коротк.ое замыкание выходов блока формирователей входньис сигналов 6 на выходы проверяемой схемы 17. ,.,.-sK-rr-- -.--- Далее в устройство вводится тестовая программа проверки данной схемы 1 Эта программа с помощью блока ввода 1 и блока управления 2 записывает во входной 3 и выходной 4 регистры информацию, которую необходимо подать на входы схемы 17 и которая должна быть на выходах исправной МЛС. Эта же программа устанавливает на программируемом блоке питания 5 требуемое напряжение питания схемы 17J на амплитудном селекторе 7 - допустимые уровни логического О и 1 выходных сигналов на управляемом элементе задержки 8 - пределы временной селекции выходных сигналов. . На блоке формирователей входных сигналов 6 - уровни логического О и 1 сигналов, подаваемых на входы МЛС117. ч:, .-: - После этого из блока управления 2 в блок запуска 9 поступает сигнал, разрещающий сч1ттывание информации со входного регистра 3 в блок формирователей входных игналов 6. С блока запуска 9 на 5травляемый элемент задержки 8 поступает сигнал начала отсчета времени совпадающий по времени с изйеНением сигналов на выходах блока форкшрователей выходных сигналов 6, который с элемента задержки 8 в качестве аапрётающегЬ с.йгнала поступает на всё входы многоканального Временного селектора 10. . .. :....-. .... Сигналы на выходах проверяемой схемы 17 прЯ1вляютсяс нёк)эторой задерж- .. кой, зависящей от схемы 17. Через временной селектор 10 в амплитудный селектор 7 lipоход;яттолько те сигналы со схемы 17, которые появляются раньше : прихода запрёщ эдёго сдгнала с элемента задержки S на временной селектор 1О. Сигйалы,. прощёдшиё через временной селектор, подвергаются амплитудному контролю в амплитудном селекторе 7. Сигналы, удовлетворяющие требова.киям по амплитуде и времени, записываются в запоминающий регистр 11. И нформация J запис.анная в запоминающем регистре 11, вводится в цифровойёлок сравнения 12, где сравнивается с требуемой рёалсцией для заданного теста. Результаты сравнения выводятря на бло1с индикации 13 ина выводной блок 14 и далее - на цифропечатающий блок 15,.. . Таким образом, введеный всхему блок контроля коммутаторов входов обеспечивает защиту выходов блока форми рователей от коротких замыканий на вы ходы проверяемой: микроэлектронной л гической схемы, предотвращает выход v.3 строя блока контроля и проверяемой микроэлектронной логической схемы. Формула изобретения Устройство для контроля микррэлектронных логических схем по авт.св. № 273342, отл. ичающееея тем, что, с целью повышения его надежности, в него введен блок контроля О коммутаторов входов, причем его информационные входы соединены соответственно с выходами блока форкгарователей входных сигналов, управляхшшй вход соединен с одним из выхоаов блока управления, первый выход - с одним из управляющих входов блока формирователей входных сигналов, а его второй выход - с одним иа входов цифрсу печатающего блока. Источники информации, принятые во внимание при экспертизе 1. Автбрское сввдетёльствр СССР N 273342, Н 03 К 17/Ор, 197О.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для КОНТРОЛЯ МИКРОЭЛЕКТРОННЫХ ЛОГИЧЕСКИХ СХЕМ | 1970 |

|

SU273342A1 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| Устройство для контроля запоминающих матриц | 1979 |

|

SU875468A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1518906A2 |

| Устройство для программирования микросхем постоянной памяти | 1985 |

|

SU1285535A1 |

| Устройство для контроля электрических параметров кварцевых резонаторов | 1978 |

|

SU779927A1 |

| Устройство для контроля электронных схем | 1982 |

|

SU1084815A1 |

| СИСТЕМА АВТОМАТИЗИРОВАННОГО КОНТРОЛЯ | 1991 |

|

RU2006896C1 |

| Устройство для тестового диагностирования логических блоков | 1976 |

|

SU661552A1 |

| Устройство для функциональногоКОНТРОля МиКРОэлЕКТРОННыХ узлОВ | 1978 |

|

SU809185A1 |

Авторы

Даты

1979-02-05—Публикация

1977-04-14—Подача