Изобретение относится к автоматике и вычислительной технике и может быть использовано на предприятиях, изготавливающих сложную, радиоэлектронную аппаратуру.

Известны устройства для контроля логических узлов, содержащие блок оперативной памяти, адресный, коммутатор, блок управления, блок генерации стимулирувяцих воздействий, блок коммутации стимулирующих воздействий, блок шлявления неисправностей и блок аналнгза неисправностей и логической обработки и соответствущие связи f и 2 .

Указанные устройства подают на объект контроля тестовые воздействия, контролируют и анализируют выходные сигналы об.ъекта контроля и выдают полученные результаты испытаний.

Недостатком указанных устройств является невозможность обеспечения контроля временных последовательностей.

Наиболее близким к изобретению по технической сущности является устройство для контроля электронных схем, содержащее блок управления, входной выходной и запоминающий регистры, программируелий блок питания, амплитудный селектор, цифровую схему сравнения, формирователь входных, сигналов, блок запуска, бЛок индикации, дифропечатающее устройство, устройство ввода и вывода, временной селектор и блок Зс1дания времени вход которого подключен к формирующему выходу блока запуска, выход - к управляющему входу временного селектора, управляющий вход соединен с блоком управления, входы временного селектора подсоединены к выходам контролируемой схемы, а выходы - к входам амплитудного селектора 3j .

Однако известное устройство не позволяет измерять длительность временных интервалов, формируемых последовательно в объектах контроля, что делает его неприменимым при контроле программных устройств, формирующих последовательность выдержек времени.

Цель изобретения - расширение области применения, т.е. обеспечение возможности контроля временных последовательностей .

Указанная цель достигается тем, что в устройство для контроля электронных схем, содержащее блок хранения теста, первый выход которого соединен с информационным входом первого входного регистра, связанного выходом с информационным входом первого промежуточного регистра, выход которого через цифроаналоговый преобразователь соединен с выходом

устройства, первый вход которого соединен с информационным входом временного селеткора, подключенного выходом через амплитудный селектор к информационному входу первого выходного регистра, связанного выходом с первым входом элемента эквивалентности, второй выход блока хранения теста соединен с информационным входом второго входного регистра, выход которого соединен с установочным входом счетчика времени, подключенного первым выходом к информационному входу второго выходного регистра,, связанного выходом с вторым входом элемента эквивалентности, третьим входом подключенного к третьему выходу блока хранения теста, четвертый выход которого соединен с информационным .входом третьего входного регистра, первый выход которого через первый элемент И соединен с управляющим входом первого промежуточного регистра, второй выход через второй элемент И подключен к управляющим входам временного селектора и первого- выходного регистра, третий выход через третий элемент И соединен с тактовым входом счетчика адреса, подключенного выходом к адресному входу блока хранения теста, и выходу блока задержки , выход которого подключён к тактовому входу счетчика кода дефекта, выходгд элемента эквивалентности соединены с входами первого элемента ИЛИ, выход которого соедигнен со счетным входом счетчика кода дефекта, подключенного выходом, чере дешифратор к блоку индикации,запускющий вход устройства подключен к установочному входу счетчика адреса и запускающему входу счетчика кода дефекта, введены четвертый входной регистр, второй промежуточный регистр, блок ключей, второй элемент ИЛИ, выход которого подключен к вторым входам -первого, второго и третьего элементов И, к управляющим входам счетчика времени и второго выходного регистра, к управляющему входу второго промежуточного регистра, выход которого подключен к первому входу блока ключей, выходом подключенного к первому входу второго элемента ИЛИ, первый вход которого соединен с запускающим входом устройства, второй и третий входы блока ключей соединены соответственно с вторым выходом счетчика времени и вторым входом устройства, пятый выход блока хранения тестасоединен через четвертый входной регистр с информационным входом второго промежуточного регистра.

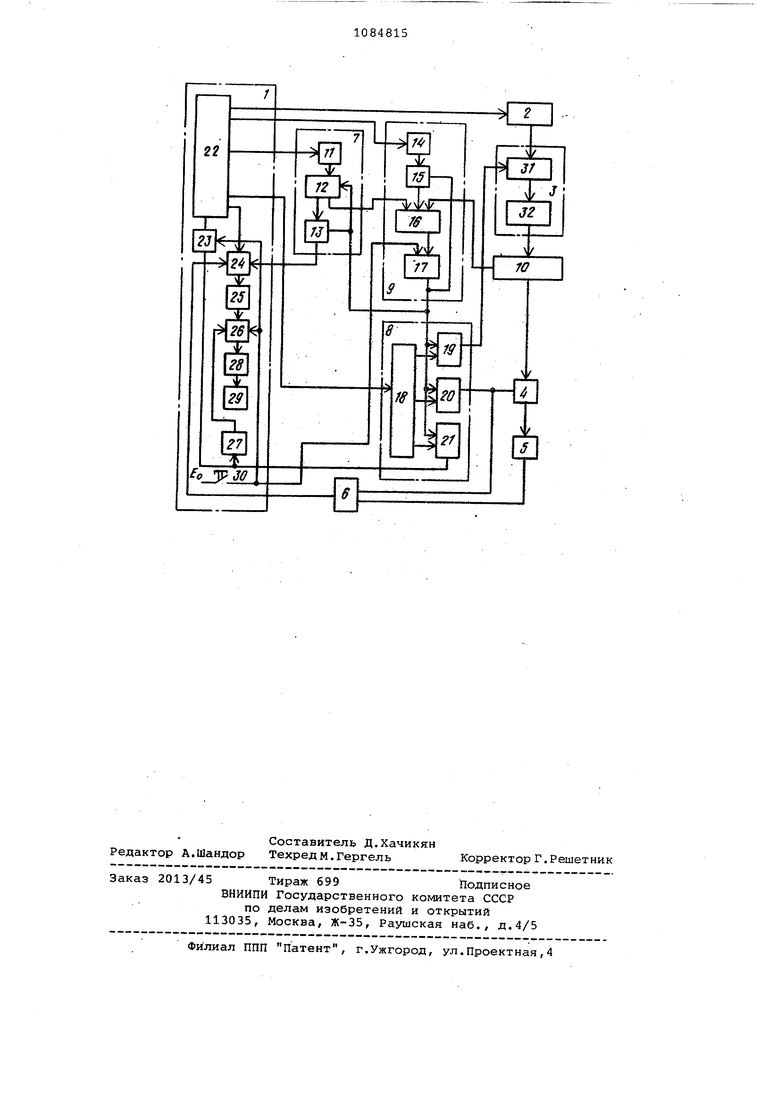

На чертеже показана структурная схема предлагаемого устройства.

Устройство содержит узел 1 анализа и управления, первый входной регистр 2, формирователь 3 входных сигналов, временной селектор 4, амплитудный селектор 5, первый выходной регистр 6, узел 7 счета времени, узел 8 запуска и узел 9 стробирования, контролируемую электронную схему 10.Узел 7 содержит второй входной регистр 11, счетчик 12 времени и второй выходной регистр 13.

Узел 9 содержит четвертый входной регистр 14, второй промежуточный регистр 15, блок 16 ключей и второй элемент 17.

Узел 8 содержит третий входной регистр 18, элементы И 19-21.

Узел 1 содержит блок 22 хранения теста, счетчик 2J адреса, элемент 24 эквивалентности,, первый элемент ИЛИ 25, счетчик 26 кода дефекта, блок 27 задержки, дешифратор 28, блок 29 индикации и кнопку 30 Пуск (запускающий вход устройства).Формирователь 3 содержит первый промежуточный регистр 31 и преобразователь 32 кода.

Устройство работает следующим образом.

Оператор нажимает кнопку 30, счетчик 23 формирует адрес информации, необходимой для первого-шестоFO воздействия. Из блока 22 хранения теста в регистр 2 заносятся коды, соответствующие первому тестовому воздействию, в регистр 11 - код, соответствующий задаваемой устройством длительности временного интервала, если подготавливается задание или код, соответствующий максимальному пределу счетчика 12, если предстоит измерение длительности временного интервала.

В третий 18 и четвертый 14 регистры заносятся коды в соответствии с функциями узлов 8 и 9запуска и стробирования соответственно. На выходе первого элемента ИЛИ 17 и узла 9 формируется сигнал подачи первого тестового воздействия на объект: код из второго входного регистра переносится в счетчик 12, в результат е чего последний начинает счет, код из

регистра 2 переписывается в регистр 31 и с выходов преобразователя 32 на схему 10 подаются сигналы тестового воздействия, стробирующий код из регистра 14 переписывается в регистр 15, сигнал с третьего выхода элемента И 21 увеличивает содержимое счетчика 23.

Увеличение содержимого счетчика 23 приводит к действиям, подготавливающим очередное тестовое воздействие, заносятся соответствующие очередному воздействию коды в регистры 2,11, 14 и 18. Одновременно с этим на входах элемента 24 выставляются эталонные значения ре.акции объекта на текущее тестовое воздействие.

После срабатывания схемУ 10 или счетчика 12, выбранного кодом, хра нящимся 3 регистре 15, на выходе узла 9 появляется сигнал, который приводит к записи содержимого счетчика 12 в регистр 13, сигналов реакции схемы 10 - в регистр б, подаче на объект следующего тестового воздействия, запуску следующего цикла счета времени для измерения или задания длительности. В результате на схему 10 подано очередное тестовое воздействие, на входы элемента эквивалентности поданы сигнала реакции схемы 10 на предыдущее тестовое воздействие и измеренное значе.ние времени вместе с соответствующим эталонным значением.

После некоторой задержки, формируемой блоком 27, сигнал с выхода элемента ИЛИ 25 принимается счетчиком 26. Дальнейшая работа происходит аналогично. После окончания диагностирования в счетчике 26 будет накоплено, а в блоке 29 индицировано число, соответствующее состоянию контролируемой схемы 10 (код дефекта).

Использование узла стробирования позволяет осуществить синхронизацию его контролируемой электронной схемы и, вследствие этого, измерять последовательность формируемых контролируемых объектом временных интерВсШОВ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| Устройство для диагностирования дискретных узлов | 1988 |

|

SU1681305A1 |

| Устройство для диагностирования дискретных блоков | 1986 |

|

SU1520516A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1988 |

|

SU1667075A1 |

| Многоканальное устройство для контроля систем управления | 1985 |

|

SU1345200A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРОННЫХ СХЕМ, содержащее блок хранения теста, первый выход которого соединен с информационным входом первого входного регистра, связанного выходом с информационным входом первого промежуточного регистра, выход которого через цифроаналоговый преобразователь соединен с выходом устройства, первый вход которого соединен с информационным входом временного селектора, подключенного выходом через амплитудный селектор к информационному входу первого выходного регистра, связанного выходом с первым входом элемента эквивалентности , второй выход блока хранения теста соединен с информационным входом второго входного регистра, выход которого соединен с установочным входом счетчика времени, подключенного первым выходом к информационному входу второго выходного регистра, связанного выходом с вторым входом элемента эквивалентности, трет.ьим входом подключенного ,к третьему выходу блока хранения теста, четвертый выход которого соединен с информационным входом третьего входного регистра, первый выход которого через первый элемент И соединен с управляющим входом первого промежуточного регистра, второй выход через второй элемент И подключен к управляющим входам временного селектора и первого шлходного регистра, третий выход через третий элемент И соединен с тактовым входом счетчика адреса, подключенного выходом к адресному входу блока хранения теста и входу блока задержки, выход которого подключен к тактовому входу счетчика кода дефекта, выходы элемента эквивалентности соединены с входами первого элемента ИЛИ, выход которого соединен со счетным входом i счетчика кода дефекта, подключённого выходом через дешифратор к блоку (Л индикации, запусканкций вход устройства подключен к установочному вхо ду счетчика адреса и запускающему входу счетчика кода дефекта, о т личайщееся тем, что, с .целью расширения области его приме. нения, в него введены четвертый входной регистр, второй промежуточный регистр, блок ключей, второй элемент X) ИЛИ, выход которого подключен к вторым входам первого, второго и третьJiiii его элементов И, к управляющим вхоэо :л дам счетчика времени и второго выходного регистра, к управляющему входу второго промежуточного регистра, выход которого подключен к первому входу блока ключей, выходом подключенного к первому входу второго элемента ИЛИ, первый вход которого соединен с запускающим входом устройства, второй и третий входы блока ключей соединены соответственно с вторым выходом счетчика времени и вторым входом устройства, пятый выход блока хранения теста соединен через четвертый входной регистр с информационным входом второго промежуточного регистра.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-04-07—Публикация

1982-06-14—Подача