Изобретение относится к контрольно-измерительной технике, в частности к технике программируемых тестовых испытаний сложных микроэлектронных логических схем.

Известны устройства для контроля сложных микроэлектронных логических схем, содержащие блок управления, входной, выходной и запоминающий регистры, программируемый блок питания, амплитудный селектор, цифровую схему сравнения, формирователь входных сигналов, блок запуска, блок индикации, цифропечатающее устройство, устройства и вывода.

Недостатком известных устройств является либо полпое отсутствие возможности проверки динамических характеристик проверяемых сложных логических схем, либо их возможности в этом отношении сильно ограничены сравнительно низким быстродействием устройств намяти и управления, которые не могут вынолнять операций считываиия, сравнения и записи тестовой информации с такой тактовой частотой, какая требуется для динамических испытаний проверяемых микроэлектронных логических узлов.

Цель изобретения - увеличение программной гибкости статических и динамических испытаний, расширение возможности динамических исследований .микроэлектронных логических схем в наносекундном диапазоне и повышение эффективности его использования в лабораторных и производственных условиях.

Это достигается тем, что в предлагаемом устройстве дополнпте.тьно установлены временной селектор, входы которого подсоединены к выходам контролируемой схемы, а выходы - ко входам амплитудного селектора, и управляемая линия задерлчки, вход которой подключен к формпруютцему выходу блока

запуска, выход - к управляющему в.ходу временного селектора и управляющий в.ход соединен с блоком управления.

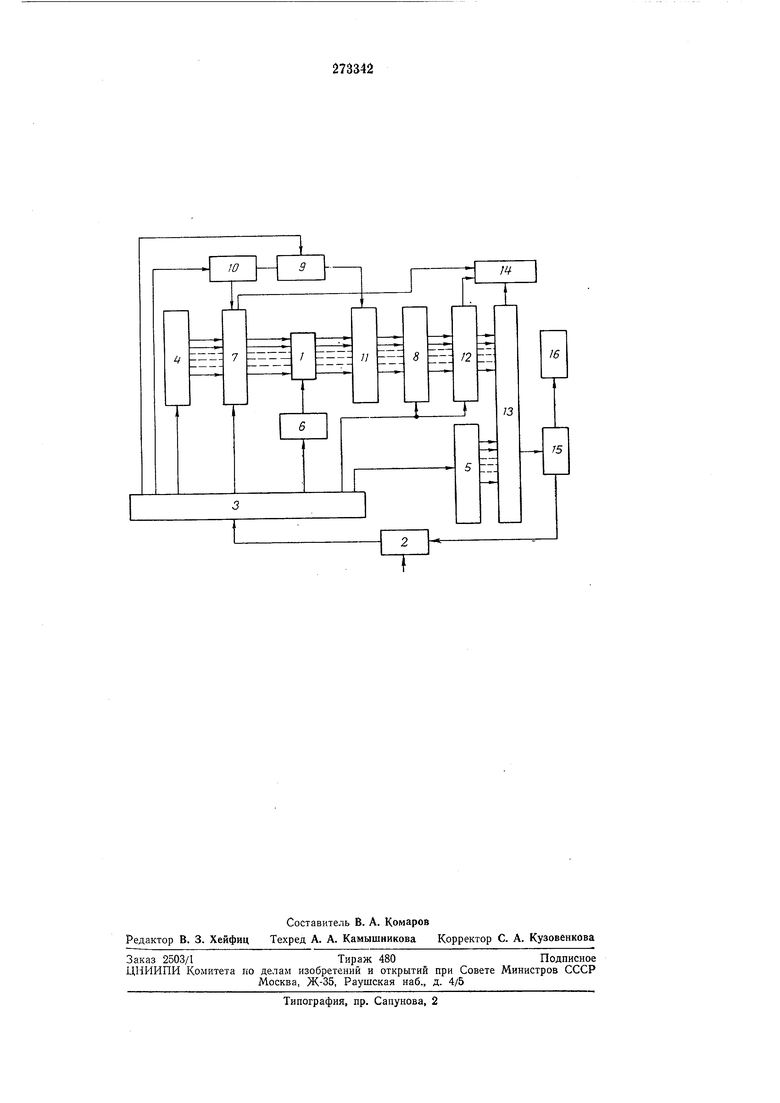

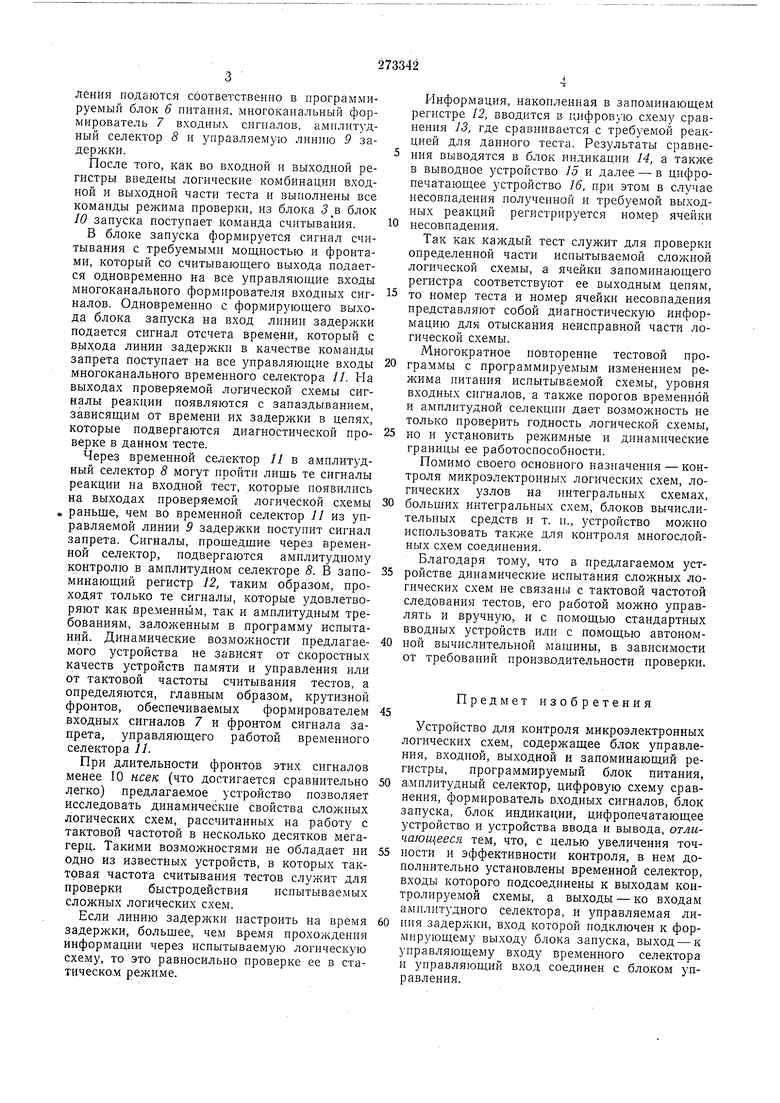

На чертеже приведена функциональная блок-схема описываемого устройства.

Контрольно-диагностическаяпрограмма

проверкн мпкроэлектронной логической схемы / в виде магнитной .ленты, перфоленты или другого носителя тестовой информации подается в устройство ввода 2, откуда с помощью блока 3 управления записывается во входной 4 и выходной 5 регистры. Количество ячеек этих регистров равно соответственно максимальному числу входов и выходов проверяемых логических схем. В программе тестовых испытаню имеются команды установления заданного режима по питанию, выбора требуемых уровней входных логических сигналов «О и «1, уровней амплитудной селекции выходных сигналов и границ их временленйя подаются соответст-веняо в программируемый блок 6 питапия, многоканальный формирователь 7 входных сигналов, амплитудный селектор 8 и управляемую линию 9 задерл ки.

После того, как во входной и выходной регистры введены логические комбинации входной и выходной части теста и выполнены все команды режима ироверки, из блока 3 ъ блок 10 запуска поступает команда считывания.

В блоке запуска формируется сигнал считывания с требуемыми мощностью и фронтами, который со считывающего выхода подается одновременно на все управляющие входы многоканального формирователя входных сигналов. Одновременно с формирующего выхода блока запуска на вход линии задержки подается сигнал отсчета времени, который с в.ыхода линии задерл :ки в качестве команды занрета поступает на все управляющие входы многоканального временного селектора 11. На выходах проверяемой логической схемы сигналы реакции появляются с запаздыванием, зависящим от времени их задержки в цепях, которые подвергаются диагностической проверке в данно,м тесте.

Через временной селектор 11 в амплитудный селектор 8 могут пройти лищь те сигналы реакции на входной тест, которые появились на выходах проверяемой логической схемы раньще, чем во временной селектор //из управляемой линии 9 задержки поступит сигнал запрета. Сигналы, прошедщие через временной селектор, подвергаются амплитудному контролю в амплитудном селекторе 8. В запоминающий регистр 12, таким образом, ироходят только те сигналы, которые удовлетворяют как временньш, так и амплитудным требованиям, заложенным в программу испытаний. Динамические возможности предлагаемого устройства не зависят от скоростных качеств устройств памяти и управления или от тактовой частоты считывания тестов, а определяются, главным образом, крутизной фронтов, обеспечиваемых формирователем входных сигналов 7 и фронтом сигнала занрета, управляющего работой временного селектора //.

При длительности фронтов этих сигналов менее 10 нсек (что достигается сравнительно легко) предлагаемое устройство позволяет исследовать динамические свойства сложных логических схем, рассчитанных на работу с тактовой частотой в несколько десятков мегагерц. Такими возможностями не обладает ни одно из известных устройств, в которых тактовая частота считывания тестов служит для проверки быстродействия испытываемых сложных логических схем.

Если линию задерл ки настроить на время задержки, больщее, чем время прохождения информации через испытываемую логическую схему, то это равносильно проверке ее в статическо,м режиме.

Информация, накопленная в запоминающем регистре 12, вводится в цифровую схему сравнения 13, где сравнивается с требуемой реакцией для данного теста. Результаты сравнения выводятся в блок индикации 14, а также в выводное зстройство 15 и далее - в цифропечатающее устройство 16, при этом в случае несовпадения полученной и требуемой выходных реакций регистрируется номер ячейки

несовпадения.

Так как каждый тест служит для проверки определенной части испытываемой сложной логической схемы, а ячейки запоминающего регистра соответствуют ее выходным цепям,

то номер теста и номер ячейки несовпадения представляют собой диагностическую информацию для отыскания неисправной части логической схемы. Многократное повторение тестовой программы с программируемым изменением режима питания испытываемой схемы, уровня входных сигналов, а также порогов временной и амплитудной селекции дает возможность не только проверить годность логической схемы,

но и установить режимные и динамические границы ее работоспособности.

Помимо своего основного назначения - контроля микроэлектронных логических схем, логических узлов на интегральных схемах,

больщих интегральных схем, блоков вычислительиых средств и т. п., устройство можно использовать также для контроля многослойных схем соединения. Благодаря тому, что в предлагаемом устройстве динамические испытания сложных логических схем не связаны с тактовой частотой следования тестов, его работой можно управлять и вручную, и с помощью стандартных вводных устройств или с помощью автономной вычислительной машины, в зависимости от требований производительности проверки.

Предмет изобретения

Устройство для контроля микроэлектронных логических схем, содержащее блок управления, входной, выходной и запоминающий регистры, программируемый блок питания, амплитудный селектор, цифровую схему сравнения, формирователь входных сигналов, блок запуска, блок индикации, цифропечатающее устройство и устройства ввода и вывода, отличающееся тем, что, с целью увеличения точности и эффективности контроля, в нем дополнительно установлены временной селектор, входы которого подсоединены к выходам контролируемой схемы, а выходы - ко входам амплитудного селектора, и управляемая липня задержки, вход которой подключен к формирующему выходу блока запуска, выход - к управляющему входу временного селектора и заправляющий вход соединен с блоком управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микроэлектронных логических схем | 1977 |

|

SU646280A2 |

| Устройство для контроля электронных схем | 1982 |

|

SU1084815A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

| Устройство для проверки функционирования логических схем | 1980 |

|

SU955072A1 |

| Устройство для формирования тестовых воздействий | 1987 |

|

SU1476473A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1608697A1 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1013960A1 |

| Устройство для контроля запоминающих матриц | 1979 |

|

SU875468A1 |

Авторы

Даты

1970-01-01—Публикация