1

Изобретение относится к вычиспитепь ной техншсе и может быть испопьзовйнр дпя. вычиспения взаимных и автокоррепяционных функций.

Известен цифровой коррелятор, характеризующийся частично коррепироваяной выборкой с одной стороны, иш невысоким быстродействием с другой стороны

Наиболее бгшзким. пОтетаическойсущности является многоканальный коррелятор содержащий в каждом канале аналого-цифровой преобразователь, соединенный с выходным регистром, цифровую пинию задержки, бпок умножения, выход которого подключен к бдоку усреднения, допоинитепьный аналого-цифровой преобразователь, соединенный с допопнитепьйым выходным регистром, выход которого соединен с первыми входами бпоков умножения каждого канала, входы всех яого-пифроЕых преобрааоватеяей объегрдаены и являются входом коррелятора, каналы не симметричны, так как они содер жат неодинаковые линии звиерккв; у которых время задержки возрастает в каждом аосяеду1Ш1ем канале.

В корреляторе степень корреляции определяется из соотношения между числом каналов М, шагом задержки д

, At . ..

И периодом квантования дг -. - i ..-. а I

Отсюда, если используется, например,

восьмиканальный коррелятор, при вычислении принимают во внимание только

каждый восьмой отсчет, что приводит к потере точности 2.

Целью изобретения является повьпне- кие точности.

Поставленная цель достигается тем,

что в йоррелятор введен распределитель и в кажхый канал - первый и второй регистры и коммутатор , причем в канале первый и второй входы коммутатора соединены соответственно с

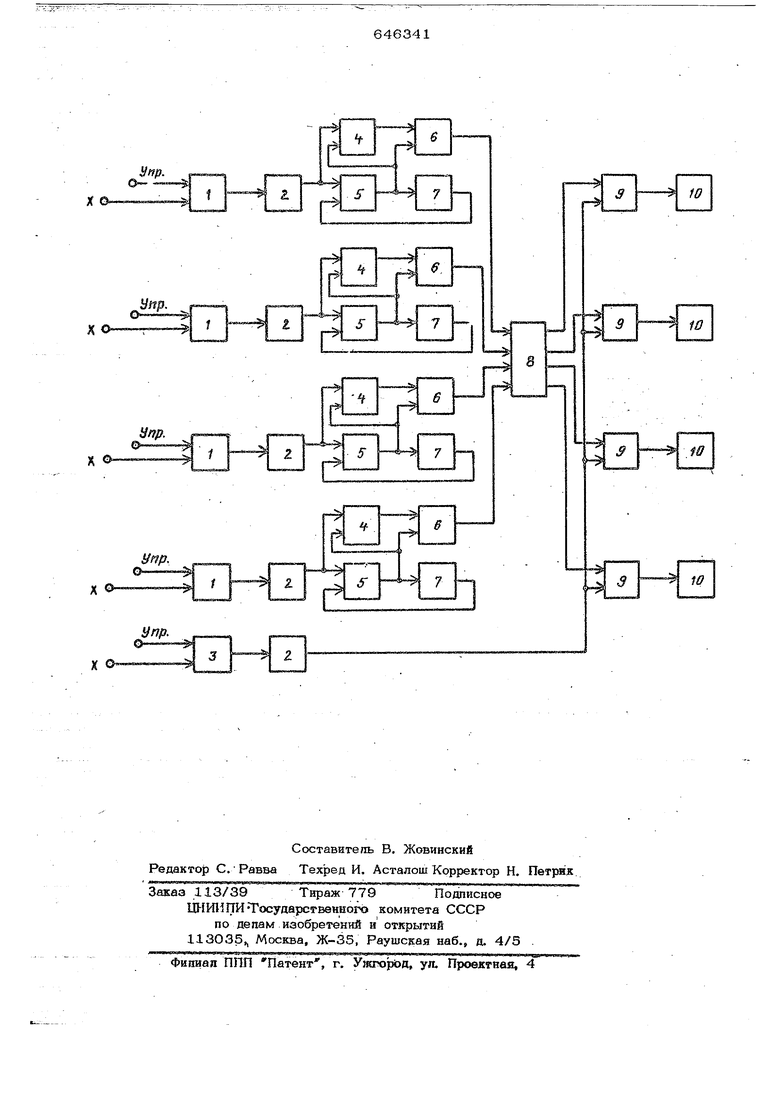

выходами первого и второго регистров, выход второго регистра подключен к первому входу первого регистра и ко входу цй4фовой линии задержки, выход которой соединен с первым входом второго регистра, вторые входы первого и второго регистров подключены к выходу выходного регистра, выход коммутатора кажд го канапа соединен с соответствующим входом распреде-яигекя ВЬТХОДЬЕ которого соединены со вторьумк входами бпо- ков умножения. На чертеже изображена бпок-схема описьтаемого коррелгстора. Он содержит; анапого-цифровой преобразоватепь 1 с .регистром 2, общий анапого-цифровой . преобразоватепь 3, регистры 4,5, ком мутатор 6 сомножитепей, цифровая пини задержки 7,., распредепитепь 8 канапов, блок умножения. 9, блок усреднения 1О. Коррелятор состоит из М каналов, каждьй из которых содержит аналогоцифровой преобразователь (АЦП) 1, выхош Ой регистр 2, который своими выходами подключен к соответствующим входам регистров 4 и 5. Выходы регис ров 4 подключены к одним входам коммутаторов 6 сомножителей, а выходы регистров 5 по цключены ко входам циф ровых линий 7 задержки, выходы которых соединены со вторыми входами регистров 5, и вторым входом регистров 4, и коммутаторов С сомножителей, вы ходы которых пошслючены ко входам распределителя 8 каналов. Выходы распределителя 8 каналов подключены к одним входам соответствующих блоков умножения 9, вторые входы которых соединены с выходом выхошюго регист ра 2, подключенного своим входом к АЦП 3, Выходы блоков умножения 9 соединены со входами блоков усреднения 10. 1Тод воздействием управляющих импульсов, запускающих аналого-цифровые преобразователи 1, последовательно в порядке возрастания номера канала с частотой дискретизации исходных нроце сов заполняются регистры 2, При ера-, батывайии АЦП М-pro и запол нения соответствующего регистра 2 от- счеты по всем каналам поступают в. регистры 5,откуда .они переписьтаются в цифровую пинию 7 задержки и одн временно через коммутатор 6 и распре делитель 8 канапов поступают на- одни входы блоков 9 соответствующих каналов. На вторые входы блоков умножения 9 поступает отсчет, произведенный в один момент времени с преобразователем М-ого канапа и находящийся в соответствующем регистре 2 блока ум- ноженип. Результаты перемножения отсчетов поступают в блоки усреднения 10, В послед Юшие моменты врекзени до прихода в регистр 2 первого канапа следующего отсчета в регистр 5 с тактовой частотой работы цифровой задержки 7 считьтаются ранее записанные в ней отсчеты в порядке, обратном поступлению, и через коммутатор б и распределитель 8 каналов подаются на одни входы тех же блоков умножения, На протяжении всего цикла вычислений (до прихода следукяяего отсчета в ре гистр 2 первого канала) в регистре 2 общего аналого-цифрового преобразователя хранится отсчет, снятый в один момент времени с отсчетом, хранимым Э регистре 2 М-ого канала, а распределитель 8 коммутирует сомножитель первого канала на вход блока умножения первого канала, сомножитель второго канапа на вход бпока умноже ния второго канала и т. д. Таким образом, между сомножителями первого и общего каналов временной сдвиг равен (М-1)ДС , (2 М - l)/iC , (ЗМ-1) дТ...между сомножителями второго и общего каналов - (М-2), (), (ЗМ-2) ,.. и т. д, С приходом следующего отсчета в регистр 2 первого канала и регистр 2 общего канала (они совпадают по времени) цикл вычислений производится аналогично во всех каналах за исключением первого, В первом канале считьгеание с линии задержки 7 и регистр 5 отсчета, записанного в линию задержки 7 в. предыдущем цикле, совпадает по времени с перезаписью нового отсчета из регистра 2 И коммутации его коммутатором 6 на вход распределителя 8 канапов. Таким образом, в первом канале ;сдвиг во вре мени между сомножителями (отсчетом первого канала и отсчетом, находящимся в. регистре 2 общего канала) равен О jAtT, во втором - (M-l)AC, в третьем (М-2) Atr и т. д. Распределитель 8 каналов коммутиру ет сомножители следующим образом: с первого канала на блок умножения. 9 М-ого канала, со второго канала на блок умножения 9 первого канала, с третьего канала на блок 9 второго канала и т„ д. Таким образом,сомножители сдвигаются на один канал Б сторону уменьшения номера канала. Считывание поспедукядих отсчетов с цифровой ЛИНИЙ 7 первого канапа iв регистр бсопровождается перезаписью пр дыдугаего отсчета в регистр 4 и коммутаци ей его на вход распре делителя 8 каналов. Такая последовательность работы сохра няется на протяжении всего цикпа до прихода спедуюшего отсчета в приемный регистр 2 второго канала. По приходу следующего отсчета в приемный регистр 2 второго канала и регистр .3 общего цикл вычислений прои ходит аналогич о ранее описанному во всех каналах за исключением первых двух, где последовательность вычислений соответствует описанному выше для первого канала, а сомножители распределителем 8 каналов сдвигаются на два канала в сторону уменьшения номера канала. Такая тенденция последовательности работы сохраняется до прихода спедуюшего отсчета в приемный регистр 2 М-ого канала, с приходом которого весь описанный алгоритм работы повторяется. Введение дополнительных регистров, а также коммутатора и распредепигеля t каналов позволяет распараллеливать вы числение корреляционных функций по идентичным каналам при исследовании случайных процессов как со слабо, так и с сильно коррелированной выборкой, т. е. с потерей и без потерь информации между отсчетами, что дает возможность обрабатьгаать кратковременные быстропротекающие процессы в реальном масштабе времени. Формула изобретения Многоканальный коррелятор, содержа щий в канале аналого-цифровой преобразователь, соединенный с выходным регистром, цифровую пинию задержки, блок умножения, выход которого подключен к блоку усреднения, дополнительный аналого-цифровой преобразователь, соединенный с дополнительным выходным регистром, выход которого соединен с первыми входами блоков умножения каждого канала, входы всех аналого-цифро вых преобразователей объединены и являются входом, коррелятора, отличающийся тем, что, с иелью повышения точности, в коррелятор введен распределитель и в каждый канал первый и второй регистры и коммутатор, причем в каждом канале первый и второй входы коммутатора соединены соответственно с выходами первого и второго регистров, выход второго регистра подключен к первому входу первого регистра и ко входу цифровой линии задержки, выход которой соединен с первым входом второго регистра, вторые входы первого и-второго регистров подключены к выходу выхошюго регистра, выход коммутатора каждого канала соединен с соответствующим входом распредепителя, выходы которого соединены со вторыми входами блоков умножения. ; Источники информации, принятые во внимание,при экспертизе 1.Жовинский В. Н., Лрховский В. Ф. Корреляционные устройства. М.,Энергия , 1974. 2.Авторское свидетельство СССР №292169,Q 06 F 15/34, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор для обнаружения эхо-сигналов | 1976 |

|

SU642713A1 |

| Цифровой коррелятор | 1976 |

|

SU636619A1 |

| Многоканальный многомерныйцифРОВОй КОРРЕлОМЕТР | 1978 |

|

SU809199A1 |

| Цифровой коррелятор | 1990 |

|

SU1824642A1 |

| Цифровой коррелятор | 1976 |

|

SU610117A1 |

| МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ КОРРЕЛОМЕТР | 1972 |

|

SU419895A1 |

| ИНТЕГРИРОВАННЫЙ ПРИЕМНИК СИГНАЛОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1999 |

|

RU2146378C1 |

| Автокоррелятор | 1989 |

|

SU1617447A1 |

| РАДИОПРИЕМНОЕ УСТРОЙСТВО МНОГОЧАСТОТНЫХ СИГНАЛОВ | 2005 |

|

RU2310992C2 |

| ПРИЕМНИК ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2423794C1 |

Авторы

Даты

1979-02-05—Публикация

1977-02-24—Подача