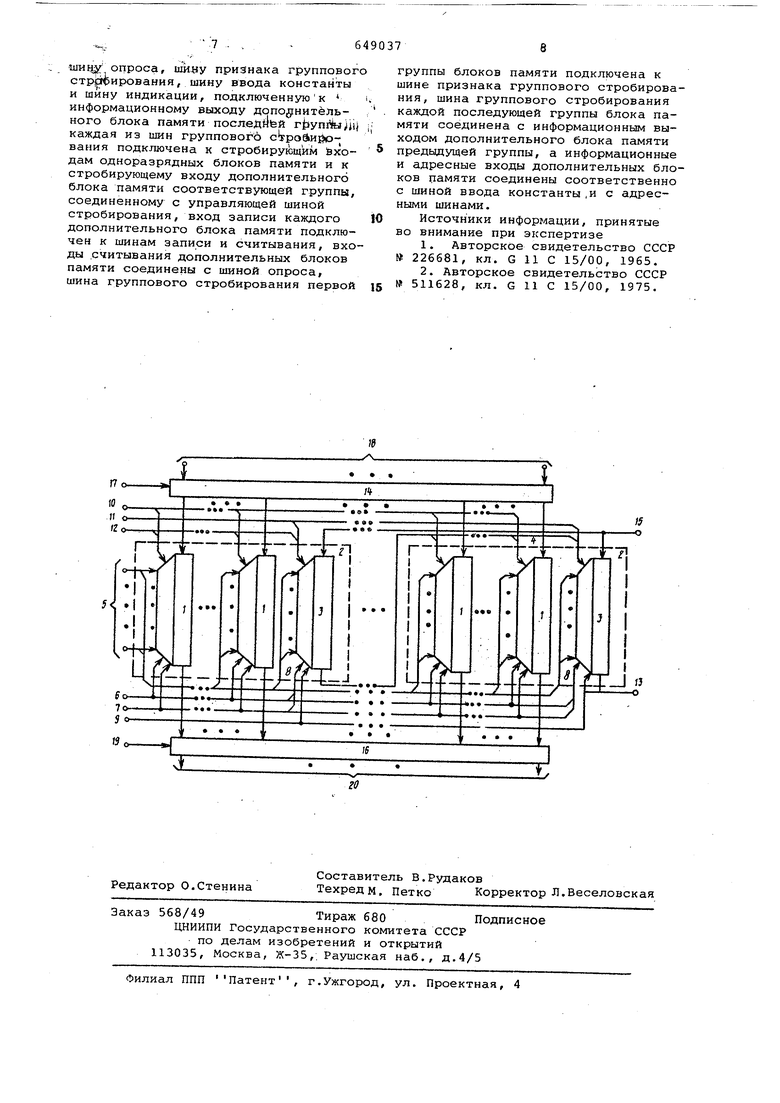

(54) ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО вующей группы, соединенному с управляющей шиной стробирования, вход записи каждого дополнительного блока памяти подключен к шинам записи и считывания, входы считывания дополнительных блоков памяти соединены с шиной опроса, шина группового стробирования первой группы блоков памяти подключена к шине признака группового стробирования, шина группового стробирования каждой последующей группы блоков памяти соединена с ниформационным выходом дополнительного блока памяти предыдущей группы, а информационные и адресные входы дополнительных блоков памяти соединены соответственно с шиной ввода константы и с адресными . Hd чертеже приведена схема предло женного логического запоминающего .устройства. Устройство содержит одноразрядные блоки памяти 1, объединенные в группы 2, каждая из которых содержит дополнительный блок памяти 3, шину 4 группового .стробирования. Адресные входы блоков памяти 1 и подключены к адресным шинам 5. Входы записи и считывания блоков памяти 1 соединены с одноименными шинами запи си 6 и считывания 7, а вход 8 записи блоков памяти 3 подключен как к шин записи б,, так и к шине считывания 7 Входы считывания всех блоков памяти соединены с шиной опроса 9. Стробирующие входы блоков памяти 1 каждой из групп 2 подключены.к шин 10 общего стробирования и к соответствующей шине 4 группового стробирования, а стробирующий вход каждого блока памяти 3 соединен с соответст вующей шиной 4 группового стробирования и с управляющей шиной 11 стробирования. Шина 4 группового.стробирования первой группы 2 подключена к шине 1 признака группового стробирования, а информационный выход блока памяти 3 последней группы 2 соединен с шин 13 индикации. Информационные входы блоков памя ти 1подключены к выходам входного регистра 14, информационные входы блоков памяти 3 - к шине 15 ввода константы, а информационные выходы блоков памяти 1 соединены со входами выходногорегистра 16. Устройство также содержит управл щую шину 17 и входы 18 входного : регистра 14, управляющую шину 19 и выходные шины 20 выходного регист ра 1 6 . Логическое запоминающее устройст во имеет два режима работы: режим работы с полным словом и режим груп работы. . Считаем,что до начала работы во :всех ячейках блоков памяти 3 записа нули. Выполнение операций записи или считывания в блоках памяти 1 и 3 происходит только в том случае,если они находятся в активном состоянии. Переход каждого из блоков 1 и 3 в активное состояние возможен не только по сигналу,поступающему на стробирующий вход этих блоков .После выполненияопераций записи или считывания блоки памяти 1 и 3 переходят в пассивное состояние. Управляющие сигналы на шины 5-7, 9-12, 15,17 и 19 подаются от блока управления (на чертеже не показан). Работа устройства в режиме с полным словом происходит следующим образом. В первом такте на шину 10 общего стробирования поступает управляющий сигнал, переводящий в активное состояние все блоки памяти 1. Во втором такте управляющие сигналы подаются на адресные шины 5 и на одну из шин записи 6 или считывания 7, Если во втором такте управляющий сигнал присутствовал на шине записи б, то в адресном сечении блоков памяти 1, соответствующем коду адреса на адресных шинах 5, произведена запись содержимого входного регистра 14. Если же во втором такте управляющий сигнал поступал на шину считывания 7, то из адресного сечения блоков памяти 1, соответствующего коду адреса на адресных шинах 5, произведено считывание и занесение информации в выходной регистр 16, . По окончании второго такта режим работы с полным словом заканчивается.. Работа логического запоминающего устройства в групповом режиме происходит следуюдим образом. Считаем, что при выполнении операции записи, информация, поступающая на входы 18 входного регистра 14, имеет байтовой формат и заносится по сигналу в управляющей шине 17 во все группы разрядов входного регистра 14 соответствуюйше группам 2блоков памяти 1, а при выполнении операции считывания, байт информации, считываемый в любой из групп 2, заносится по сигналу в управляющей шине 19 в определенную группу разрядов выходного регистра 16, предназначенную для вывода информации байтового формата. в первом такте на управляющую шину 11 стробирования подается сигнал, переводящий все блоки памяти 3в активное состояние. Во втором такте при выполнении операции записи по сигналам, поступающим на шину опроса 9 и на управляющую шину 17, производится опрос адресного сечения блоков памяти 3, определяемого кодом адреса на адресных шинах 5, и запись байта информа ции, поступившего в этом же такте на входы 18, во все группы разрядов входного регистра 14, соответствующие группам 2 блоков памяти 1. Если в каком-нибудь блоке памяти 3 в опрошенном адресном сечении записана единица, то происходит ее сч тывание и сигнал с информационного выхода этого блока памяти 3 поступает на шину группового стробирования 4 последующей группы 2 и вызывае переход в активное состояние всех блоков памяти 1 и блока памяти 3 последующей группы 2. В третьем такте управляющие сигналы подаются на адресные шины 5, . на шину ввода константы 15 и на шину записи 6, в результате в адрес ном сечении, определяемом кодом адре са на адресных шинах 5, той группы 2, блоки памяти 1 и 3 которой находятся в активном состоянии, будет произведена ,запись содержимого соответствующей группы разрядов входного регистра 14 в блоки памяти 1 и единицы, поступающей по щине ввода константы 15, в блок памяти 3. Таким образом, наличие единицы в одном из адресных сечений блока пам ти 3 говорит о выполнении операции в данном адресном сечении блоков па мяти 1 соответствующей группы 2. Повторение рассмотренной трехтак ной последовательности обеспечивает поочередное выполнение операций в п следовательно расположенных группах а именно запись последовательно поступающих байтов информации а одн и том же адресном сечении последовательно расположенных групп 2,либо считывание байтов информации из одного и того же адресного сечения последовательно расположенных групп Считывание информации выполняется с разрушением, вследствие чего в любой адресном сечении всех блоков памяти 3 не может находиться более одной единицы, что обеспечивает выполнение операции только в одной из групп 2. Отличие работы логического запоминающего устройства при считывании информации в групповом режиме от работы в групповом режиме при записи информации состоит в том, что во втором такте отсутствует сигнал на управляющей.шине 17 входного регистра 14, а в третьем такте также сигнал на шине записи б отсутствует и подаются сигналы на шину считывания 7 и на управляющую шин; 19 выход ного регистра 16. Вследствие этого в блоках памяти 1, находящихся в активном состоянии выполняется операция считывания, а наличие сигнала на управляющей шине 19 выходного регистра 16 обеспечивает занесение считываемой информации с информационных выходов блоког памяти 1 любой из групп 2 в определенную группу разрядов выходного регистра 16, Вывод информации из выходного регистра 16 .на выходные шины 20 производится в первом такте. Появление во втором такте сигнала на шине индикации 13, подключенной к информационному выходу блока памяти 3 последней группы 2, означает, что закончено в данном адресном сечении формирование полного слоеа из поступающих байтов информации при Bt iполнении операции записи, либо закончено расформирование хранимого в данном адресном сечении запоминающего устройства полного слова на байты при выполнении операции считывания. По сигналу на шине индикации 13 блок управления формирует в этом же такте сигнал на шине 12 признака группового стробированид, переводя в активное состояние блоки памяти 1 и 3 первой группы 2. Одновременно изменяется и код адреса на адресных шинах 5. В томслучае, если работа логического запоминающего устройства Б груп-Повом режиме заканчивается после окончания формирования либо расформирования полного слова, блок управления при последующем переходе к групповому режиму работы дополнительно посылает во втором такте иэ первси серии в три такта сигнал на ину 12 признака групповогс стробирования. Работа логического запоминающего устройства в остальных трехтактных сериях не отличается от рассмотренной . Описанное логическое запоминающее устройство обладает более 1ш- рокой областью применения по сравнению с известными и может быть использовано, например, для организации обмена информацией с временной ее буферизацией между каналами связи, имеющими различные форматы передаваемых данных. Формула изобретения Логическое запоминающее устройсто, содержащее группы одндразрядных локов памяти, адресные входы которых одключены к адресным шинам, входы записи и считывания соединены с одноменными шинами записи и сч11тывания, тробирующие входы подключаемы к шине бщего стробирования, информационные ходы и выходы соединены соответстенно с выходами входного-и со входаи выходного регистров, о т л и ч а юе е с я тем, что, с целью расширеия области применения устройства, оно одержит дополнительные блоки памяти шины группового стробирования по ислу групп одноразрядных блоков паяти, управляющую шину стробирования

шину опроса, шйзу признака группового стррЬирования, шину ввода константы и шину индикации, подключенную к i. информационному выходу дсзпо нитёль- . ного блока памяти последней rbynifer ij j; каждая из шин групповогЬ сгройийо-; вания подключена к стробирующим fexo- дам одноразрядных блоков памяти и к стробирующему входу дополнительного блока памяти соответствующей группы, соединенному с управляющей шиной стробирования, вход записи каждого 10 дополнительного блока памяти подключен к шинам записи и считывания, входы считывания дополнительных блоков памяти соединены с шиной опроса, шина группового стробирования первой 15

группы блоков памяти подключена к шине признака группового стробирования, шина группового стробирования каждой последующей группы блока памяти соединена с информационным выходом дополнительного блока памяти предыдущей группы, а информационные и адресные входы дополнительных блоков памяти соединены соответственно с шиной ввода константы ,и с адресными шинами.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 226681, кл. G 11 С 15/00, 1965.

2.Авторское свидетельство СССР № 511628, кл. G 11 С 15/00, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1980 |

|

SU947910A2 |

| Логическое запоминающее устройство | 1979 |

|

SU858103A2 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| Устройство для ввода информации | 1984 |

|

SU1201842A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для управления замещением информации | 1975 |

|

SU651413A1 |

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Устройство управления для кассетной памяти на цилиндрических магнитных доменах | 1987 |

|

SU1495850A1 |

| Запоминающее устройство с обнаружением отказавших блоков | 1980 |

|

SU903974A1 |

Авторы

Даты

1979-02-25—Публикация

1975-04-21—Подача