Изобретение относится к вычислительной технике и может быть использовано при построении устройств хранения и обработки дискретной информации .

По основному авт.ев. 649037 известно логическое запоминающее устройство, содержащее группы одноразрядных блоков памяти, в каждую иэ которых входят основные блоки памяти,адресные входы которых подключены к адресным шинам, входы записи и считывания соединены с одноименными шинами записи и считывания, стробирующие входы подключены к шине общего стробирования, информационные входы и выходы подключены соответст вёВИо к выходам входного и входам выходного регистров, а также вспомогательный блок памяти, шины группового стробирования по числу групп одноразрядных блоков памяти, управляющую шину стробирования, шину опроса, шину признака группового стробирования, шину ввода константы и шину индикации,подключенную к информационному выходу вспомогательного блока памяти последней группы, каждая из шин группового стробирования подключена к стробирующим входам основных блок.ов памяти и

стрюбирующему входу вспомогательного блока памяти соответствующей группы, соединенному с управляющей шиной стробирования, вход записи каждого вспомогательного блока Пс1мяти подключен к шинам записи и считывания, входы считывания вспомогательных блоков памяти соединены с шиной опроса, шина группового стробирования первой

10 группы блоков памяти подключена к шине признака группового стробирования, шина группового стробирования каждой последующей группы блоков памяти соединена с информационным выходом

15 вспомогательного блока памяти предыдущей группы, а информационные и адресные входы вспомогательных блоков пзмятн соединены соответственно а шиной ввода константы и с адресными

20 шинами 1.

Недостатком известного логическо-: го запоминающего устройства является то, что оно не может быть использовано для выполнения операций редак25тирования информгщии и приоритетного обслуживания запросов на обмен информации.

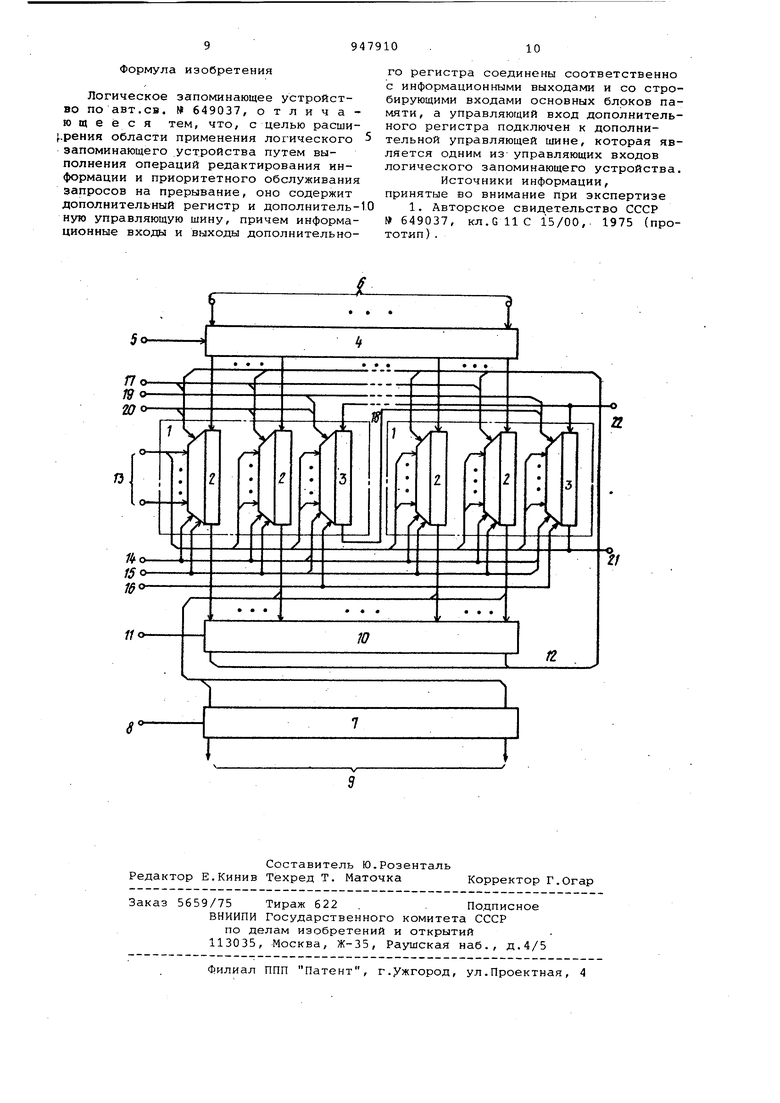

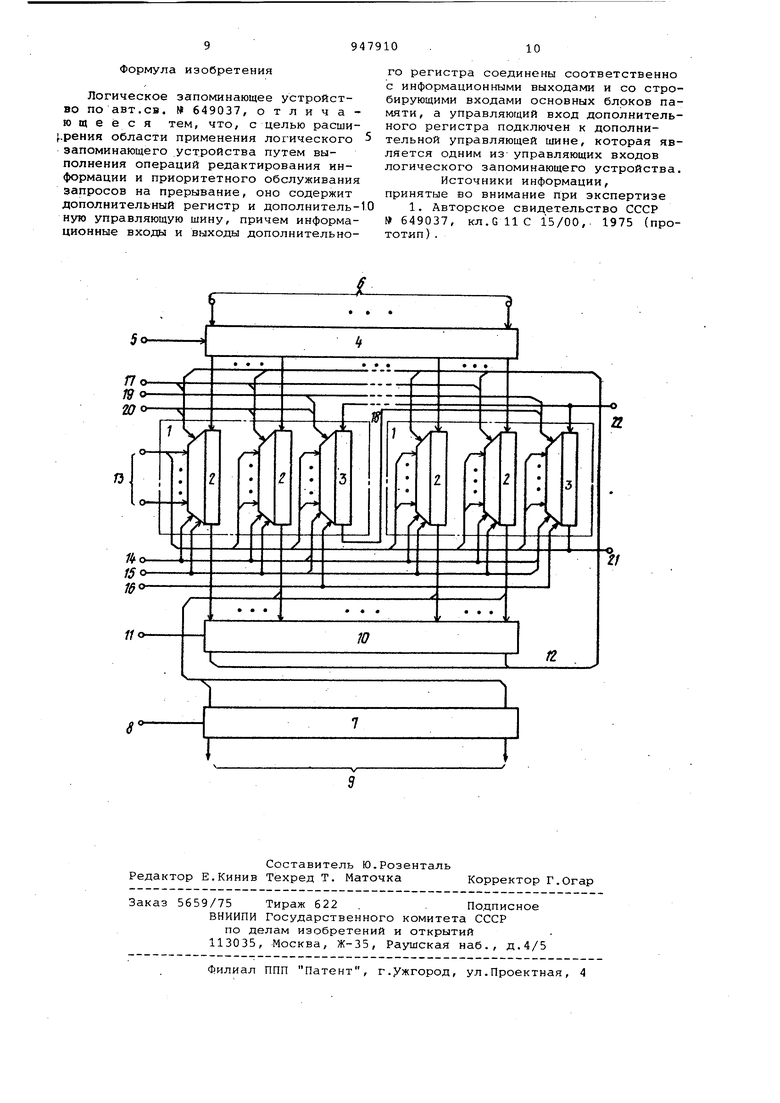

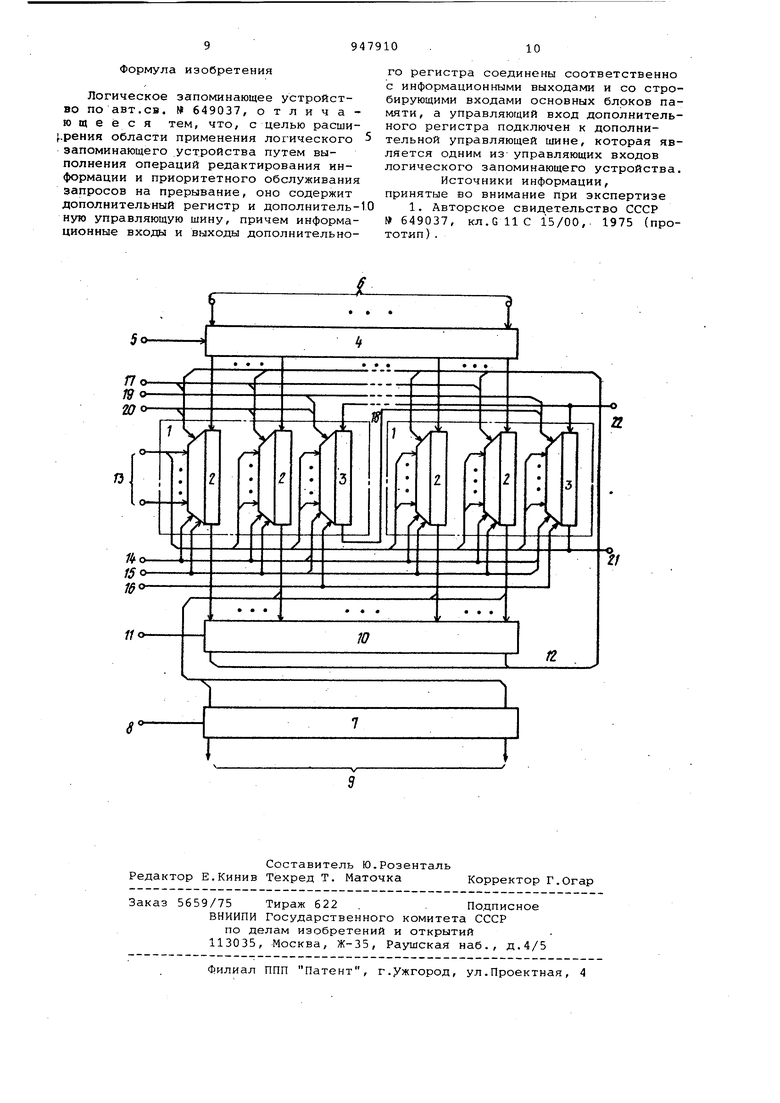

Цель изобретения - расширение области применения логического запо30минающего устройства, что позволит использовать устройство для выполнения операций редактирования информации и приоритетного обслуживания запросов на п ерьшание. Поставленная цель достигается за счет того, что известное логическое запоминающее устройство содержит дополнительный регистр и дополнительную управляющую шину, причем информационные входы и выходы дополнитель ного регистра соединены соответствен но с информационными выходами и со стробирующими входами основных блоков , а управляющий вход дополнительного регистра подключен к дополнительной управляющей шине, которая является одним из управляющих входов логического запоминающего уст ройства. На чертеже приведена схема предлагаемого логического запоминающего устройства. Устройство содержит группы 1 одноразрядных блоков памяти, в каждую из которых входят основные 2 блоки памяти и вспомогательные 3 блоки памяти, входной регистр 4, выходы кото рого подключены к информационным входам основных блоков 2 памяти, вход управления - к управляющей шине 5, а входы 6 являются информационньлми входами логического запоминающего устройства, выходной регистр 7, входы которого связаны с информационными выходами основных блоков 2 памяти, вход управления под ключен к управляющей шине 8, а выход 9 являются информационными выходами логического запоминающего устройства а также дополнительный регистр 10, входы 11 которого подключены к информационным выходам основных блоков 2 памяти, а выходы 12 к стробирующим входам соответствующих основных блоков 2 памяти. Адресные входы бло ков 2 и 3 памяти подключены к адрес ным шинам 13. Входы записи и считывания основных блоков 2 памяти подключены к одноименным шинам записи 14и считывания 15. Вход записи всп могательных блоков 3 памяти подключ как к шине 14 записи, так и к шине 15считывания. Входы считывания . вспомогательных блоков 3 памяти под ключены к щине 16 опроса. Стробирую щие входы основных блоков 2 памяти подключены к шине 17 общего стробирования и к соответствующей шине 18 группового стробирования, а стробирующий вход каждого вспомогательног блока 3 памяти подключен к соответс вующей шине 19 стробирования. Шина группового стробирования первой грул пы 1 подключена к шине 20 признака группового стробирования, а информа ционный выход блока 3 памяти послед ней группы 1 соединен с щиной 21 ин дикации. Информационные входы вспомогательных блоков 3 памяти подключены к шине 22 ввода константы. Логическое запоминающее устройство имеет четыре режима работы: работа с полным словом, групповая работа, редактирование и приоритетное обслуживание запросов. Допустим, что до начала работы во всех ячейках блоков 3 памяти записаны нули. Выполнение операций записи или считывания в блоках 2 и 3 памяти происходит только в том случае, если они находятся в активном состоянии. Переход каждого из блоков 2 и 3 памяти в активное состояние возможен только по сигналу, поступающему на стробирующий вход этих блоков. После выполнения операций записи или считьтания блоки 2 и 3 памяти переходят в пассивное состояние. Управляющие сигналы на шины 5,8,11,13-17,19,20 и 22 подаются от блока управления (не показан) . Работа устройства в режиме с полным словом происходит следующим образом. В первом такте на шину 17 общего стробирования поступает управляющий сигнал, переводящий в активное состояние все блоки 2 памяти. Во втором такте управляющие сигналы подаются на адресные шины 13 и на одну из шин записи 14 или считывания 15. Если во втором такте управляющий сигнал присутствовал на шине 14 записи, то в адресном сечении блоков 2 памяти, соответствующем коду адреса на адресных шинах 13, произведена запись содержимого входного регистра 4. Если же во втором такте управляющий сигнал поступал на шину 15 считывания, то из адресного сечения блоков 2 памяти, соответствующего коду адреса на адресных шинах 13, произведены считывание и занесение информации в выходной регистр 7. По окончании второго такта режим работы с полньлм словом заканчивается. Работа логического запоминающего устройства в групповом режиме происходит следующим образом. Допустим, что при выполнении операции записи, информация, поступающая на входы 6 входного регистра 4, имеет байтовый формат и заносится по сигналу в управляющей шине 5 во все группы разрядов входного регистра 4, соответствующие группам 1 блоков 2 памяти, а .при выполнении операции считывания,байт информации, считываемый в любой из групп 1, заносится по сигналу в управляющей шине 8 в определенную группу разрядов выходного регистра 7, предназначенную для вывода информации байтового формата. В первом такте на управляющую шину 19 стробирования .подается сигнал.

переводящий все блоки 3 памяти в активное состояние. Во втором такте при выполнении операции записи по сигналам, поступающим на шину опроса 16 и на управляющую шину 5, производится опрос адресного сечения блоков 3 памяти, определяемого кодом адреса на сшресных шинах 13, и запись байта информации, поступившего в этом же такте на входы 6, во все группы разрядов входного регистра 4, соответствующие группгии 1 блоков 2 памяти.

Если в каком-нибудь блоке 3 памяvTH в опрошенном адресном сечении записана единица, то происходит ее считывание и сигнал с информационното выхода этого блока 3 памяти поступает на шину группового стробирования 18 последующей группы 1 и вызывает переход в активное состояние всех блоков 2 и 3 памяти последующей группы 1..

в третьем такте управляющие сигналы подаются на адресные шины 13, на шину 22 ввода константы и на шину 14 записи. В результате в адресном сечении, определяемом кодом адреса на адресных шинах 13 той группы 1, блоки 2 и 3 памяти которой находятся в активном состоянии, будет произведена запись содержимого соответствующей группы разрядов входного регистра 4 в блоки 2 памяти и единицы, поступающей по шине 22 ввода константы, в блок 3 памяти.

Таким образом, наличие единицы в одном из адресных сечений блока 3 памяти говорит о выполнении операции в данном адресном сечении блоков 2 памяти соответствующей группы 1.

Повторение рассмотренной трехтактовой последовательности обеспечивает поочередное выполнение операций в последовательно расположенных группах 1, а именно запись последовательно поступающих байтов информадни в одном и том же адресном сечении последовательно расположенных групп 1, либо считывание байтов информации из одного и того же адресного сечения последовательно расположе ных групп 1.

Считывание информации выполняется с разрушением, вследствие чего в любом адресном сечении всех блоков 3. памяти не может находиться более одной единицы, что обеспечивает выполнение операции только в одной из групп 1.

Отличие работы логического запоминающего устройства при считывании информации в групповом режиме от работы в групповом режиме при записи информации состоит в том, что во втором такте отсутствует сигнал на управляющей шине 5 входного регистра 4 а в третьем такте отсутствует также сигнал на шине записи 14 и подаются сигналы на шину считывания 15 и на управляющую шину 8 выходного регистра. 7..

Вследствие этого в блоках 2 памяти, находящихся в активном состоянии, выполняется операция считывания, а наличие сигнала на управляющей шине В выходного регистра 7 обеспечивает занесение считываемой информации с информационных выходов блоков 2 памяти любой из групп 1 в определенную группу разрядов выходного регистра 7.

Вывод информации из выходного регистра 7 на выходе шины 9 производится в первом такте. Появление во втором такте сигнала на шине 21 индикации, подключенной к информационному выходу блока 3 памяти последней группы 1, означает, что закончено в данном адресном сечении формирование полного слова из поступающих байтов информации при выполнении операции записи, либо закончено расформирование хранимого в данном адресном сечении запоминающего устройства полного слова на байты при выполнении операции считывания.

По сигналу на шинег 21 индикации блок управления формирует в этом же такте сигнал на шине 20 признака группового стробирования, переводя э активное состояние блоки 2 и 3 памяти первой группы 1. Одновременно изменяя и код адреса, на адресных шинах 13.

В том случае, если работа логического запоминающего устройства в групповом режиме заканчивается после окончания формирования либо расформирования полного слова, блок управления при последующем переходе к групповомурежиму работы дополнительно посылает во втором такте из перво серии в три такта сигнал на шину 20 признака группового стробирования. Работа логического запоминающего устройства в остальных трехтактовых сериях не отличается от рассмотренной.

Рассмотрим работу логического запоминающего устройства в режиме редактирования информации иа примере выполнения таких операций редактиро аания как маскирование, замена групп разрядов, выполнение логической операции над группой разрядов.

Считаем, что в Р ячейках(, где п - общее количество ячеек логического запомимающего устройства) хранятся маски, которые используются пр выполнении перечисленных ныне операций.

Работа логического згшоминаюи)его устройства при выполнении операции маскирования протекает следующим образом. В первом такте на шину 17 общего стробирования поступает сигнал, переводящий все блоки 2 памяти в актив ное состояние. Вовтором такте управляющие сигналы подаются на адресные шины 13, шину 15 считывания и уп равляющую шину 11, После второго такта в дополнительный регистр 10 будет занесена маска, содержащая нули в группе из К разрядов (, где m - разрядность слова данньох) . При этом управляющие сигналы с выходов 1 дополнительного регистра 10 переведут в активное состояние все блоки 2 памяти, кроме тех, в которых содержится группа из К разрядов слов . В третьем такте управляющие сиг налы подаются на адресные шины 13, шину 15 считывания и шину 8. По окон чании третьего такта операции маскирования заканчивается и в -выходной регистр 7 заносится слово данных, группа из К разрядов которого содер жит нули. Работа логического запоминающего, устройства при выполнении операции замены группы разрядов. Управляющие сигналы в. первых двух тактах подаются в такой же последовательности, как при выполнении операции маскирования. После второго такта в дополнительный регистр 10 заносится маска, содержащая единицы в группе разрядов, которые подлежат замене. При этом в активное состояние переходят соответствующие блоки 2 памяти. В третьем такте управляющие сигналы поступают на адресные шины 13 и шину 14 записи. После чего нужная группа в слове данных заменяется на -поступившую из входного регистра 4. Работа логического запоминающего устройства при выполнении логичес кой операции Конъюнкция. Управляющие сигналы в первых дву тактах подаются так же,как и при вы полнении операции маскирования и за мены групп разрядов. После второго такта в дополнительный регистр 10 з писывается один из операндов. При этом в активное состояние переходят блоки 2 памяти, на стробирующие вхо ды которых поступают единичные сигналы с выходных шин 12 дополнительного регистра 10. В третьем такте управляющие сигналы поступают на ад ресные шины 13, шину считывания 15 шину 8.- По окончании третьего та та в выходной регистр 7 записываетс результат выполнения операции Конъ юнкция . В режиме приоритетного обслужива ния запросов логическое запоминающее устройство работает : следующим образо Допустим, что по одному кз алресов в логическом запоминающем устройстве, например по нулевому адресу, хранится маска обслуживаемого запроса, равная инверсии слова приоритета внешнего устройства. Коды запроса поступают от внешних устройств на адресные шины 13 логического запоминающего устройства, в адресных сечениях которого хранят.ся слова приоритета внешних устройств. При поступлении на адресные шины 13 кода запроса от внешнего устройства логическое запоминающее устройство начинает обрабатывать- запрос. В первом такте управляю1ций сигнал поступает на шину 17 общего стробирования и переводит в активное состояние все блоки 2 памяти. Во втором такте управляющие сигналы поступают на шину 15 считывания и на шину 11. При этом в дополнительный регистр заносится слово приоритета, поступившего запроса и в активное состояние переходят блоки 2 памяти, на которые поступают единичные сигналы с выходных шин 12 дополнительного регистра 10. В третьем такте управляющие сигналы поступают на адресные шины 13, шину 15 считывания и шину 8. После третьего такта в выходной регистр 7 заносятся нули, если приоритет обслуживаемого запроса выше или равен проритету поступившего запроса, и занесена хотя бы одна единица в противном случае. В первом случае продолжено обслуживание прежнего запроса, а во втором, обслуживание прежнего запроса прервано, начато обслуживание поступившего запроса и в .четвертом такте управляющие сигналы поступают на шину 5, при этом во входной регистр принята константа, содержащая единицы во всех разрядах, шину 17 общего стробирования, адресные шины 13 и шину 14 записи. При этом все блоки 2 памяти переходят в активное состояние и по нулевому адресному сечению записаны единицы. В пятом такте управляющий сигнал поступает на адресные шины 13 и шину 14 записи. После чего по нулевому адресному сечению записана маска поступившего запроса, равная инверсии содержимого дополнительного регистра 10. По окончании пятого такта закончено формирование маски обслуживаемого запроса и логическое запоминающее устройство переходит в режим ожидания нового запроса . Таким образом, введение дополнительного регистра и дополнительной управляющей шины позволяет расширить область применения логического запоминающего устройства благодаря возможности выполнения ряда дополнительных операций, что говорит о достижении поставленной цели.

Формула изобретения

Логическое запоминающее устройство по авт.св. №649037, отличающееся тем, что, с целью расши.рения области применения логического запоминающего устройства путем выполнения операций редактирования информации и приоритетного обслуживания запросов на прерывание, оно содержит дополнительный регистр и дополнительную управляющую шину, причем информационные входы и выходы дополнительного регистра соединены соответственно с информационными выходами и со стробирующими входами основных блоков памяти, а управляющий вход дополнительного регистра подключен к дополнительной управляющей шине, которая является одним из управляющих входов логического запоминающего устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 649037, кл.СИС 15/00,. 1975 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1975 |

|

SU649037A1 |

| Логическое запоминающее устройство | 1979 |

|

SU858103A2 |

| Логическое запоминающее устройство | 1975 |

|

SU529486A1 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

| Логическое запоминающее устройство | 1974 |

|

SU608199A2 |

| Логическое запоминающее устройство | 1979 |

|

SU801101A2 |

| Логическое запоминающее устройство | 1980 |

|

SU886052A2 |

| Логическое запоминающее устройство | 1974 |

|

SU492934A1 |

| Запоминающее устройство с последовательным доступом | 1982 |

|

SU1070606A2 |

| Устройство для аппаратурной трансляции | 1981 |

|

SU993272A1 |

Авторы

Даты

1982-07-30—Публикация

1980-12-05—Подача