1

Изобретение относится к запоминающим устройствам и может быть применено для создания полупроводниковых блоков памяти с локализацией отказов до уровня микросхем.

Известно запоминающее устройство с обнаружением отказавших блоков, которое содержит полупроводниковые блоки памяти, схемы согласования, блок микропрограммного управления, схему сравнения, блок индикации П.

Недостатком этого устройства является то, что оно не позволяет диагностировать отказавшие элементы.

Наиболее близким к предлагаемому является запоминающее устройство, содержащее полупроводниковые блоки памяти (запоминающие микросхемы), дешифратор, блок адресных формирователей, блоки согласования, блок микропрограммного управления, схему ИЛИ, схему сравнения, коммутатор, регистры неисправной строки и столбца соответственно и схему локализации ошибок 23.

Недостатком этого устройства является невысокий уровень локализации неисправностей, поскольку отсутствует возможность определения номера неисправного адреса формирователя,разделения отказов адресных формирователей и формирователя режима, разрядных формирователей и усилителей сМитываIDния.

Цель изобретения - повышение уровня локализации неисправностей запоминающего устройства до элемента и монолитного блока (микросхемы).

ts

Указанная цель достигается тем, что в запоминающее устройство с обнаружением отказавших блоков, содержащее полупроводниковые блоки памяти, адресные входы которых соединены с

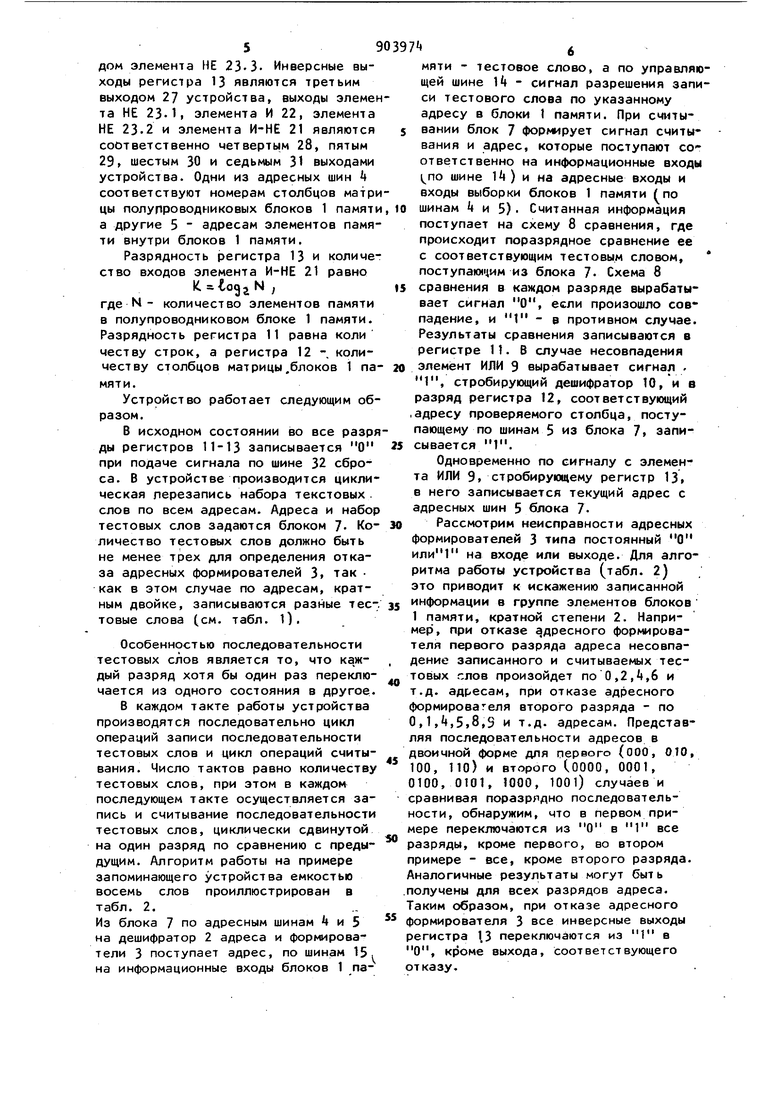

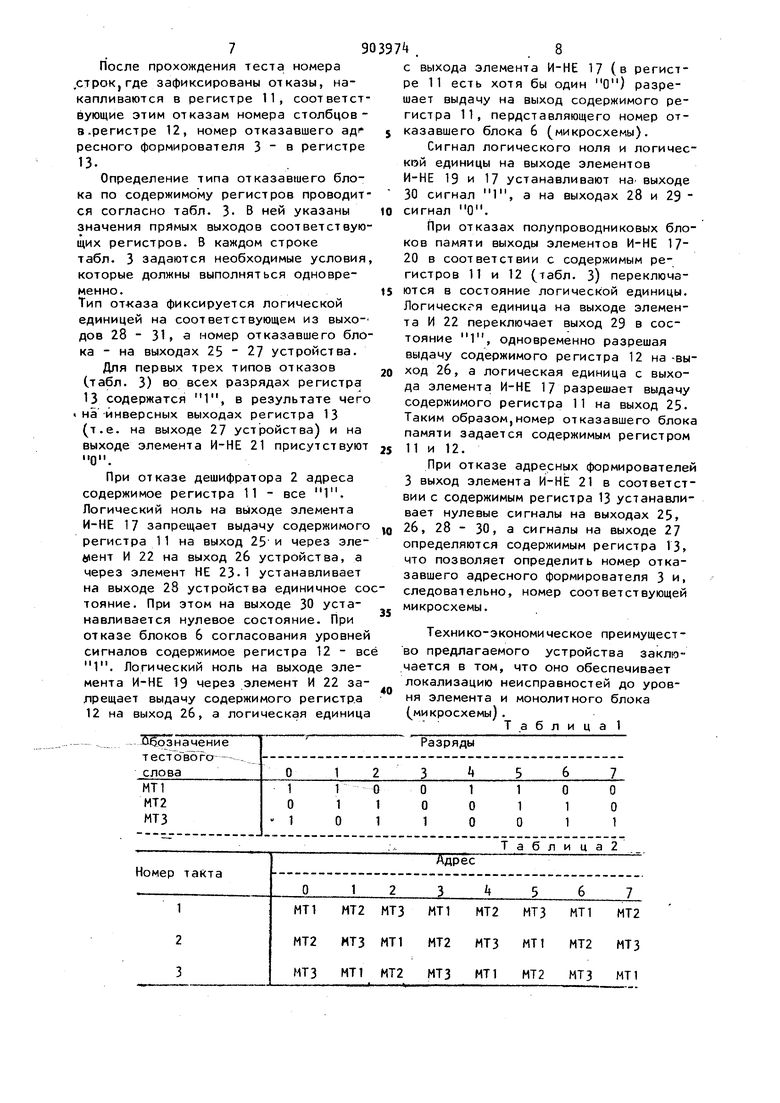

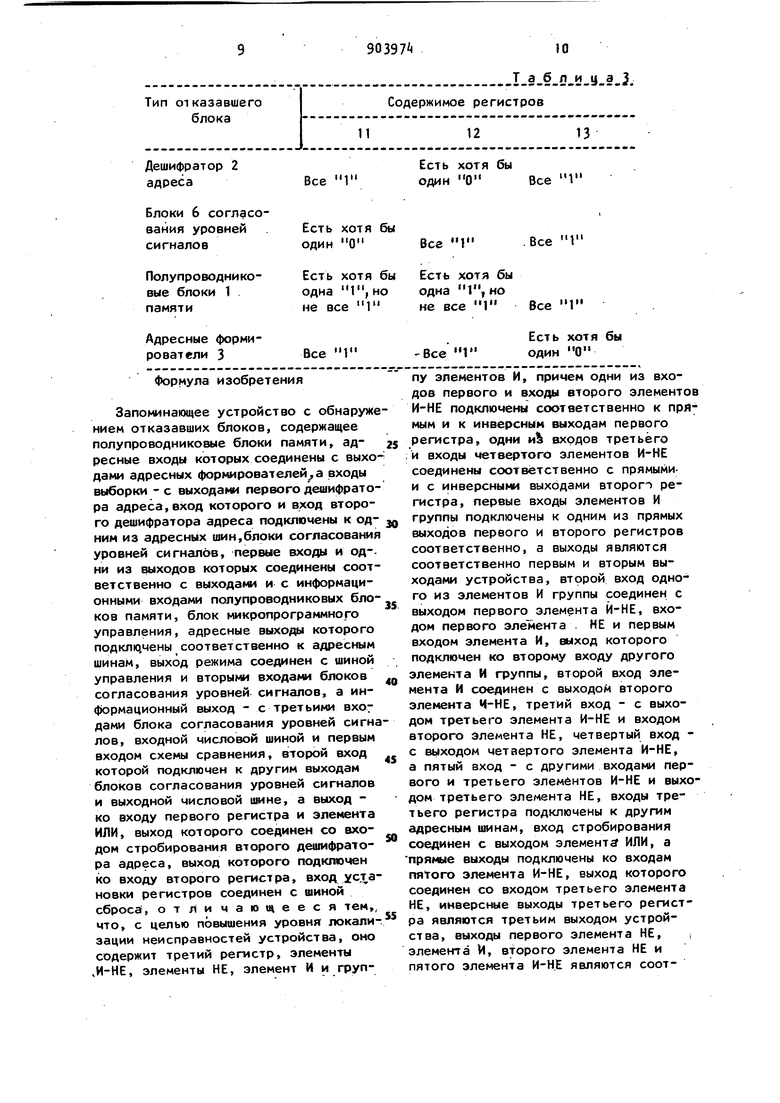

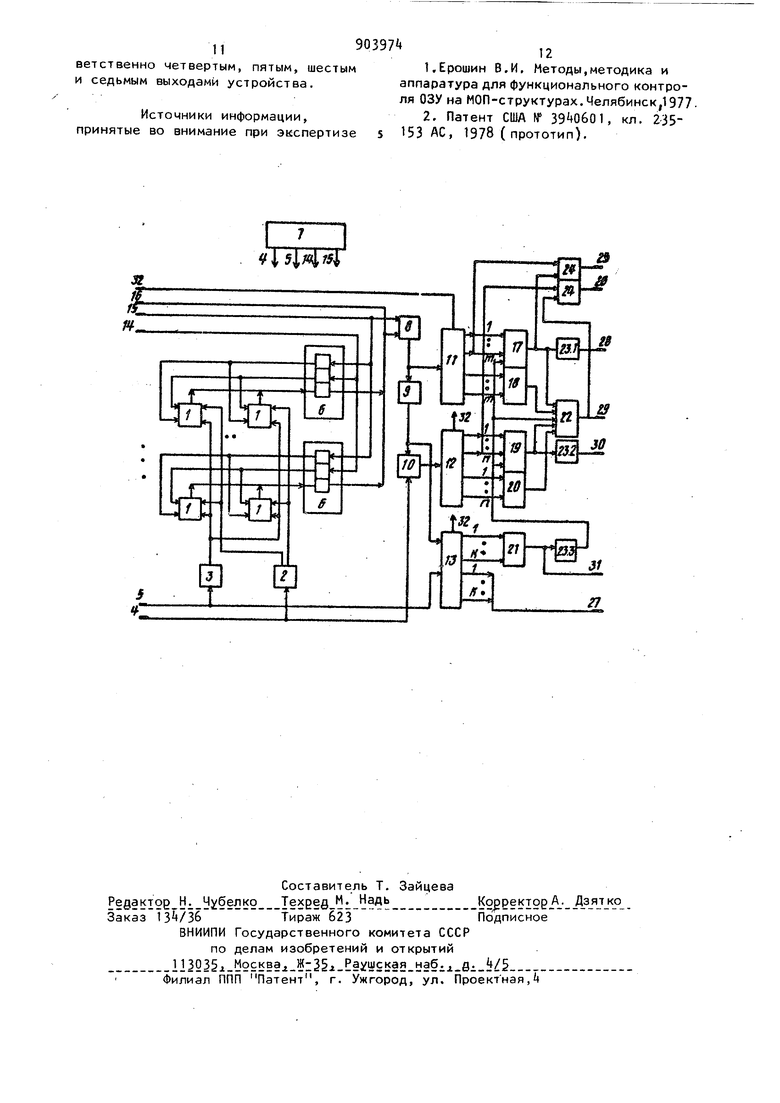

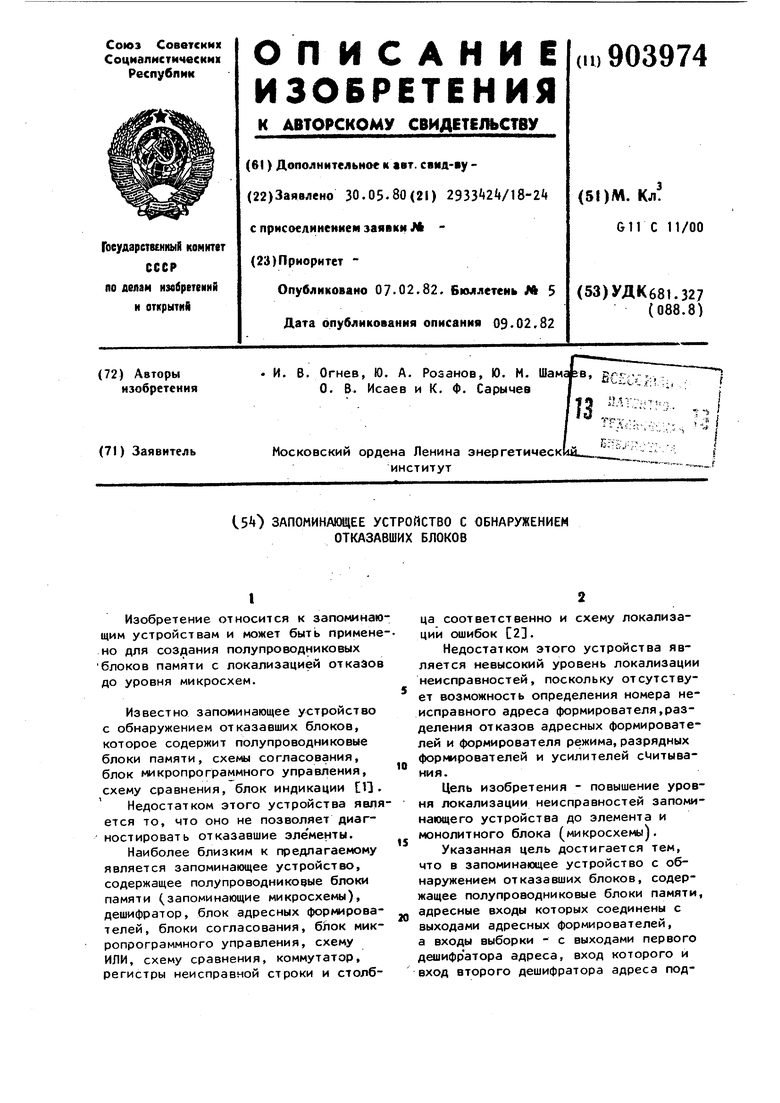

20 выходами адресных формирователей, а входы выборки - с выходами первого дешифратора адреса, вход которого и вход второго дешифратора адреса под390ключены к одним из адресных шин, бло ки согласования уровней сигналов, первые входы и одни из выходов которых соединены соответственно с выходами и с информационными входами полупроводниковых блоков памяти, блок микропрограммного управления, адресные выходы которого подклю чены соответственно к адресным шинам выход режима соединен с шиной управления и вторыми входами блоков согла сования уровней сигналов, а информационный выход - с третьими входами блоков согласования уровней сигналов входной числовой шиной и первым эходом схемы сравнения, второй вход коiторой подключен к другим выходам бло ков согласования уровней сигналов и выходной числовой шине, а выход - ко входу первого регистра и элемента ИЛИ, выход которого соединен со входом стробирования второго дешифратора адреса, выход которого подключен ко входу второго регистра, вход уста новки регистров соединен с шиной сброса, введены третий регистр, элементы И-НЕ, элементы НЕ, элемент И и группа элементов И, причем одни из входов первого и входы второго элементов И-НЕ подключены соответственно к прямым и к инверсным выходам первого регистра, одни из входов тре тьего и входы четвертого элементов И-НЕ соединены соответственно с прямыми и с инверсными выходами второго регистра, первые входы элементов И группы подключены к одним из прямых выходов первого и второго регистров соответственно, а выходы являются соответственно первым и вторым выходами устройства, второй вход одного из элементов И группы соединен с выходом первого элемента И-НЕ, входом первого элемента НЕ и первым входом элемента И, выход которого подключен ко второму входу другого элемента И группы, второй вход элемента И соединен с выходом второго элемента И-Н третий вход - с выходом третьего эле мента И-НЕ и входом второго элемента НЕ, четвертый вход - с выходом четвертого элемента И-НЕ, а пятый вход с другими входами первого и третьего элементов И-НЕ и выходом третьего элемента НЕ, входы третьего регистра подключены к другим адресным шинам, вход стробирования соединен с выходом элемента ИЛИ,а прямые выходы подключе ны ко входам пятого элемента И-НЕ,выХОД которого соединен со входом третьего элементна НЕ,инверсные выходы третьего регистра являются третьим выходом устройства, выходы первого элемента НЕ, элемента И, второго элемента НЕ и пятого элемента И-НЕ являются соответственно четвертым, пятым, шестым и седьмым выходами устройства. На чертеже изображена структурная схема устройства. Устройство содержит полупроводниковые блоки 1 памяти, организованные в матрицу, первый дешифратор 2 адреса, группу адресных формирователей 3, адресные шины А и 5, блоки 6 согласования уровней сигналов, блок 7 микропрограммного управления, схему 8 сравнения, элемент ИЛИ 9, второй дешифратор 10 адреса, первый 11, второй 12 и третий 13 регистры, шину 1 управления, входные 15 и выходные 16 числовые шины, первый-пятый элементы И-НЕ 17 - 21, элемент и 22, первый 23-1, второй 23-2 и третий 23.3 элементы НЕ и группу 24 элементов И. На чертеже обозначены выходы 25-31 устройства, служащие для выдачи сигна лов об отказе, и шина 32 сброса. Одни из входов первого 17 и входы второго 18 элементов И-НЕ подключены соответственно к прямым и к инверсным выходам регистра 11. Одни из входов третьего 19 и входы четвертого 20 элементов И-НЕ соединены соответственно с прямыми и с инверсными выходами регистра 12. Первые входы элементов И группы 2 подключены к одним из прямых выходов регистров 11 и 12 соответственно, а выходы являются соответственно первым 25-и вторым 2б выходами устройства. Второй вход одного из элементов И группы 2k соединен с выходом элемента И-НЕ 17 входом; элемента Ht 23-1 и первым входом элемента И 22, выход которого подключен ко второму входу другого элемента И группы 2k, Второй вход элемента И 22 соединен с выходом элемента И-НЕ 18, третий вход - с выходом элемента И-НЕ 20 и входом элемента НЕ 23-2, четвертый вход - с выходом элемента И-НЕ 20,а пятый вход - с другими входами элементов И-НЕ 17 и 19 и выходом элемента НЕ 23-3- Входы регистра 13 подключены к другим адресным шинам 5 вход стробирования соединен с выходом элемента ИЛИ 9, а прямые выходы подключены ко входам элемента И-НЕ 21,выход которого соединен со вхо5дом элемента НЕ 233- Инверсные выходы регистра 13 являются третьим выходом 27 устройства, выходы элеме та НЕ 23-1, элемента И 22, элемента НЕ 23.2 и элемента И-НЕ 21 являются соответственно четвертым 28, пятым 29, шестым 30 и седьмым 31 выходами устройства. Одни из адресных шин соответствуют номерам столбцов матр цы полупроводниковых блоков 1 памят а другие 5 - адресам элементов памя ти внутри блоков 1 памяти. Разрядность регистра 13 и количе ство входов элемента И-НЕ 21 равно К. ода I гдеМ - количество элементов памяти в полупроводниковом блоке 1 памяти. Разрядность регистра 11 равна коли честву строк, а регистра 12 -. количеству столбцов матрицы.блоков 1 па мят и. Устройство работает следующим образом. В исходном состоянии во все разря ды регистров 11-13 записывается О при подаче сигнала по шине 32 сброса. В устройстве производится циклическая перезапись набора текстовых . слов по всем адресам. Адреса и набор тестовых слов задаются блоком 7. Количество тестовых слов должно быть не менее трех для определения отказа адресных формирователей 3, так как в этом случае по адресам, кратным двойке, записываются разные тестовые слова (см. табл. 1). Особенностью последовательности тестовых слов является то, что ка ждый разряд хотя бы один раз переключается из одного состояния в другое. В каждом такте работы устройства производятся последовательно цикл операций записи последовательности тестовых слов и цикл операций считывания. Число тактов равно количеству тестовых слов, при этом в каждом последующем такте осуществляется запись и считывание последовательности тестовых слов, циклически сдвинутой на один разряд по сравнению с предыдущим. Алгоритм работы на примере запоминающего устройства емкостью восемь слов проиллюстрирован в табл. 2. Из блока 7 по адресным шинам 4 и 5 на дешифратор 2 адреса и формирователи 3 поступает адрес, по шинам 15 на информационные входы блоков 1 ,памяти - тестовое слово, а по управляющей шине k - сигнал разрешения записи тестового слова по указанному адресу в блоки 1 памяти. При считывании блок 7 формирует сигнал считывания и адрес, которые поступают соответственно на информационные входы (по шине 1) и на адресные входы и входы выборки блоков 1 памяти (по шинам f и 5) Считанная информация поступает на схему 8 сравнения, где происходит поразрядное сравнение ее с соответствующим тестовым словом, поступающим из блока 7. Схема 8 сравнения в каждом разряде вырабатывает сигнал О, если произошло совпадение, и 1 - в противном случае. Результаты сравнения записываются в регистре 1I. В случае несовпадения элемент ИЛИ 9 вырабатывает сигнал . 1, стробирующий дешифратор 10, и в разряд регистра 12, соответствующий .адресу проверяемого столбца, поступающему по шинам 5 из блока 7, записывается 1. Одновременно по сигналу с элемента ИЛИ 9, стробирующему регистр 13, в него записывается текущий адрес с адресных шин 5 блока 7. Рассмотрим неисправности адресных формирователей 3 типа постоянный О илиЧ на входе или выходе. Для алгоритма работы устройства (табл. 2) это приводит к искажению записанной информации в группе элементов блоков 1 памяти, кратной степени 2. Например, при отказе адресного формирователя первого разряда адреса несовпадение записанного и считываемых тестовых слов произойдет по 0,2,t,6 и т.д. адресам, при отказе адресного формирователя второго разряда - по ,8,3 и т.д. адресам. Представляя последовательности адресов в двоичной форме для первого (ООО, 010, 100, 110) и второго СОООО, 0001, 0100, 0101, 1000, 1001) случаев и сравнивая поразрядно последовательности, обнаружим, что в первом примере переключаются из О в 1 все разряды, кроме первого, во втором примере - все, кроме второго разряда. Аналогичные результаты могут быть олучены для всех разрядов адреса. аким образом, при отказе адресного ормирователя 3 все инверсные выходы егистра 3 переключаются из 1 в О, KfJOMe выхода, соответствующего тказу. После прохождения теста номера .строк, где зафиксированы отказы, накапливаются в регистре П, соответствующие этим отказам номера столбцов в.регистре 12, номер отказавшего ад| ресного формирователя 3 в регистре Определение типа отказавшего блока по содержимому регистров проводится согласно табл. 3- В ней указаны значения прямых выходов соответствующих регистров. В каждом строке табл. 3 задаются необходимые условия которые должны выполняться одновременно. Тип отказа фиксируется логической единицей на соответствующем из выходов 28 - 31, а номер отказавшего бло ка - на выходах 25 - 27 устройства. Для первых трех типов отказов (табл. 3) во всех разрядах регистрвг 13 содержатся 1, в результате чего на инверсных выходах регистра 13 (т.е. на выходе 27 устройства) и на выходе элемента И-НЕ 21 присутствуют При отказе дешифратора 2 адреса содержимое регистра 11 - все 1. Логический ноль на выходе элемента И-НЕ 17 запрещает выдачу содержимого регистра 11 на выход 25 и через элеideHT И 22 на выход 26 устройства, а через элемент НЕ 23-1 устанавливает на выходе 28 устройства единичное со тояние. При этом на выходе 30 устанавливается нулевое состояние. При отказе блоков 6 согласования уровней сигналов содержимое регистра 12 - вс 1. Логический ноль на выходе элемента И-НЕ 19 через элемент И 22 залрещает выдачу содержимого регистра 12 на выход 26, а логическая единица 9 .. 8 с выхода элемента И-НЕ 17 (в регистре 11 есть хотя бы один О) разрешает выдачу на выход содержимого регистра 11, пердставляющего номер отказавшего блока 6 (микросхемы). Сигнал логического ноля и логической единицы на выходе элементов И-НЕ 19 и 17 устанавливают на выходе 30 сигнал 1, а на выходах 28 и 29 сигнал О. При отказах полупроводниковых блоков памяти выходы элементов И-НЕ 1720 в соответствии с содержимым регистров 11 и 12 (табл. 3) переключаются в состояние логической единицы. Логическгя единица на выходе элемента И 22 переключает выход 29 в состояние 1, одновременно разрешая выдачу содержимого регистра 12 на -выход 26, а логическая единица с выхода элемента И-НЕ 17 разрешает выдачу содержимого регистра 11 на выход 25. Таким образом,номер отказавшего блока памяти задается содержимым регистром 11 и 12. При отказе адресных формирователей 3 выход элемента И-НЕ 21 в соответствии с содержимым регистра 13 устанавливает нулевые сигналы на выходах 25, 2б, 28 - 30, а сигналы на выходе 27 определяются содержимым регистра 13, что позволяет определить номер отказавшего адресного формирователя 3 и, следовательно, номер соответствующей микросхемы. Технико-экономическое преимущество предлагаемого устройства заключается в том, что оно обеспечивает локализацию неисправностей до уровня элемента и монолитного блока (микросхемы). Таблица Дешифратор 2 Все 1 адреса Блоки 6 согл сования уровней Есть хотя бы один О сигналов ПолупроводникоЕсть хотя бы Есть хотя одна 1, но одна 1, н вые блоки 1 не асе 1 не все 1 памяти Адресные формирователи 3 Все 1 Формула изобретения Запоминающее устройство с обнаруже нием отказавших блоков, содержащее полупроводниковые блоки памяти, адресные входы которых соединены с выхо дами адресных форкмрователейна входы выборки - с выходами первого дешифратора адреса, вход которого и вход второго дешифратора адреса подключены к одним из адресных шин,блоки согласования уровней сигналов, первые входы и од-, ни из выходов которых соединены соответственно с выходами и с информационными входами полупроводниковых блоков памяти, блок микропрограммного управления, адресные выходы которого подклю.чены соответственно к адресным шинам, выход режима соединен с шиной управления и вторыми входами блоков согласования уровней сигналов, а информационный выход - с третьими входами блока согласования уровней сигна лов, входной числовой шиной и первым входом схемы сравнения, второй вход которой подключен к другим выходам блоков согласования уровней сигналов и выходной числовой шине, а выход ко входу первого регистра и элемента ИЛИ, выход которого соединен со входом стробирования второго дешифратора адреса, выход которого подключен ко входу второго регистра, вход хст.ановки регистров соединен с шиной сбросй, отличающееся тем,, ЧТО, с целью повышения уровня локали зации неисправностей устройства, оно содержит третий регистр, элементы ,И-НЕ, элементы НЕ, элемент И и групЕсть хотя один О Все 1 -Все f ы Все V .Все ы Все Есть хотя бы один О пу элементов И, причем одни из входов первого и входы второго элементов И-НЕ подключены соответственно к прямым и к инверсным выходам первого регистра, одни и входов третьего ;и входы четвертого элементов И-НЕ соединены соответственно с прямымии с инверсными выходами второго регистра, первые входы элементов И группы подключены к одним из прямых выходов первого и второго регистров соответственно, а выходы являются соответственно первым и вторым выходами устройства, второй вход одного из элементов И группы соединен с выходом первого элемента И-НЕ, входом первого элемента . НЕ и первым входом элемента И, выход которого подключен ко второму входу другого элемента И группы, второй вход элемента И соединен с выходом второго элемента И-НЕ, третий вход - с выходом третьего элемента И-НЕ и входом второго элемента НЕ, четвертый вход с выходом четвертого элемента И-НЕ, а пятый вход - с другими входами первого и третьего элементов И-НЕ и выходом третьего элемента НЕ, входы третьего регистра подключены к другим адресным , вход стробирования соединен с выходом элемента ИЛИ, а прямые выходы подключены ко входам пятого элемента И-НЕ, выход которого соединен со входом третьего элемента НЕ, инверсные выходы третьего регистра являются третьим выходом устройства, выходы первого элемента НЕ, , элемента М, второго элемента НЕ и пятого элемента И-НЕ являются соот1190397 ,2

ветственно четвертым, пятым, шестым ЬЕрошин В.И. Методы,методика и и седьмым выходами устройства. аппаратура для функционального контроИсточники информации,2. Патент США № 39+Об01, кл. 2-35принятые во внимание при экспертизе 5 53 АС, 1978 (прототип). ля ОЗУ на МОП-структурах. Челябинск, 977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обнаружением отказов | 1981 |

|

SU1005192A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1993 |

|

RU2037874C1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1215140A1 |

| Устройство для исправления ошибокВ блОКЕ пАМяТи | 1979 |

|

SU842976A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Устройство для записи и контроля программируемой постоянной памяти | 1986 |

|

SU1376121A2 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

I 1

Авторы

Даты

1982-02-07—Публикация

1980-05-30—Подача