Устройство относится к технике связи и может использоваться в системах с уплотнением каналов связи. Известно устройство для уплотнения каналов связи, содержащее последовательно соединенные блок обработки данных, адресный регистр, первый селектор адреса и основной запоминающий блок 1. Однако данное устройство не обеспечивает высокой эффективности выборки каналов связи для передачи и приема. Цель изобретения - обеспечение повышения эффективности выборки каналов связи для передачи и пр-иема. Для этого в устройство для уплотнения каналов связи, содержащее последовательно соединенные блок обработки данных, адресный регистр, первый селектор адреса и основной запоминающий блок, введены дополнительный адресный регистр, линейный регистр управления адресом, накопитель данных, блок выбора считывание - запись информации, регистр управления, детектор полных символов, детектор состояния передачи, второй селектор адреса, запоминающий блок ввода - вывода, селектор приема, селектор передачи, блок декодирования, декодирующий блок передачи, селектор каналов, регистр приема, регистр передачи и регистр готовности. При этом дополнительные выходы блока обработки данных подключены соответственно через дополнительный адресный регистр и через линейный регистр управления адресом к дополнительным входам первого селектора адреса, одни выходы которого подсоединены ко входам запоминающего блока ввода - вывода через второй селектор адреса, а другие выходы - к входам селектора приема, селектора каналов и декодирующего блока передачи. Основной запоминающий блок соединен через блок выбора считывание - запись информации с накопителем данных, который связан с блоком обработки данных, с одним из входов селектора передачи и с регистром Зправления, выходы которого подключены соответственно к другому входу селектора передачи и к входу детектора состояния передачи, к входу блока декодирования, выходом подсоединенного к управляющему входу основного запоминающего блока, и к входу детектора полных символов, выход которого подключен к одному из управляющих входов блока выбора считывание - запись информации. Запоминающий блок ввода - вывода соединен с регистром приема, выход которого через селектор приема подключен к другому управляющему входу блока выбора считывание - запись информации, с регистром передачи, к другим входам которого подключены соответственно выход регистра управ:Лення -через декодирующий блок передачи и выход,селектора передачи, и с регистром готовности, выход которого через селектор каналов подсоединен к соответствующим входам регистра управления.

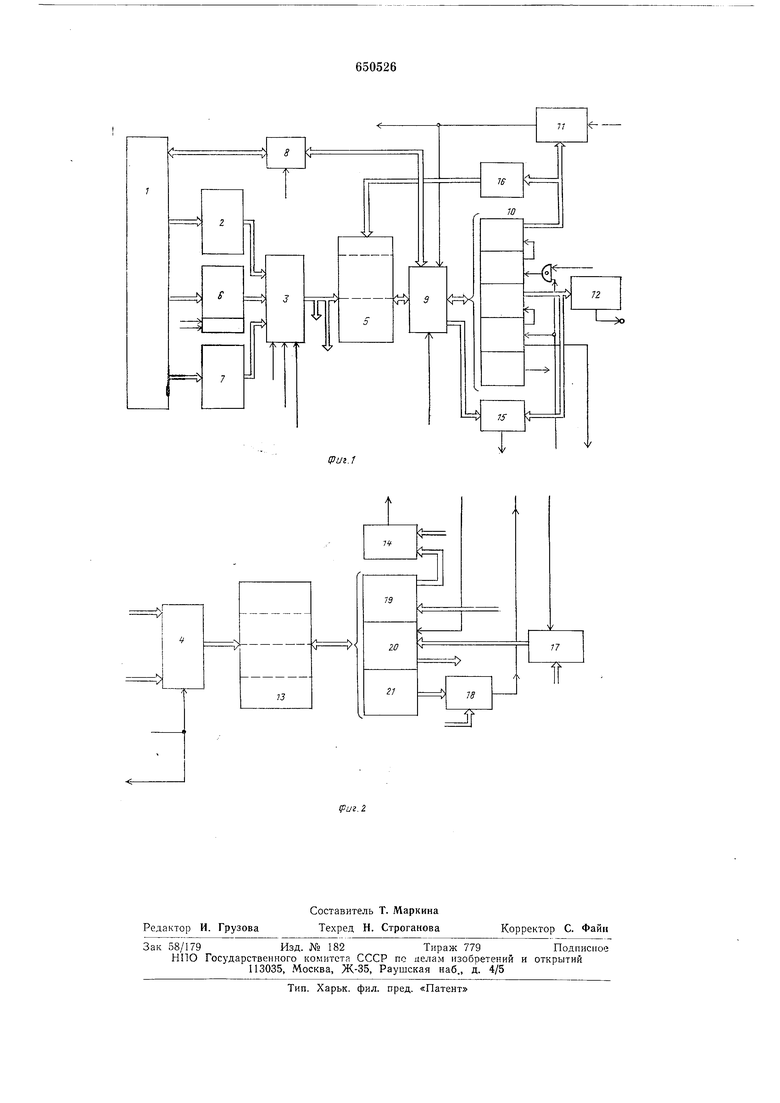

На фиг. 1 и 2 представлена структурная электрическая схема предложенного устройства.

Устройство для уплотнения каналов связи содержит блок 1 обработки данных, адресный регистр 2, первый 3 и второй 4 селекторы адреса, основной запоминающий блок 5, дополнительный адресный регистр 6, линейный регистр 7 управления адресом, накопитель 8 данных, блок 9 выбора считывание - запись информации, регистр 10 управления, детектор 11 полных символов, детектор 12 состояния передачи, запоминающий блок 13 ввода-вывода, селектор 14 приема, селектор ,75 передачи, блок 16 декодирования, декодирующий блок 17 передачи, селектор 18 каналов, регистр 19 приема, регистр 20 передачи и регистр 21 готовности.

Работает предложенное устройство сле дующим образом.

Адрес передается из блока / обработки данных в основной запоминающий блок 5, содержащий слово управления, передаваемое в регистр 10, который проверяется с помощью детектора 11 с целью определения того, полный ли признак считан из запоминающего блока 5 и передан в блок / обработки. Одновременно регистр 10 проверяется через детектор 12 для того, чтобы определить, должен ли передаваться признак из блока / обработки в запоминающий блок 5. Если оба детектора 11 и 12 не показывают необходимость передачи признака, то слово управления, содержащееся в регистре 10, вновь записывается в запоминающий блок 5, после чего адресный регистр 2 получает добавление и цикл заканчивается.

Если детектор 11 показывает, что признак должен быть передан из запоминающего блока 5 в блок 1 обработки, то посылается запрос на ввод данных, поступающий в блок обработки.

Когда детектор 12 указывает на необходимость передачи признака из блока / обработки в запоминающий блок5, то практически одновременно подается запрос на вывод данных, который также поступает на блок обработки.

В случае, если индикация необходимости передачи признака осуществляется одновременно обоими детекторами // и 12, то вначале действует запрос на ввод данных.

Однако операции осуществляются только после того, как блок обработки готов к приему запроса. Это условие может не выполняться в течение нескольких циклов или даже нескольких интервалов суб-бита.

Адрес в регистре 2 остается неизменным, пока блок 1 обработки не получит запроса.

Даже если в блок обработки не поступает запрос на ввод информации, признак информации передается из запоминающего блока 5 в накопитель 8 через блок 9 выбора. Таким образом, адрес в адресном регистре 2 не изменяется, попытки передать информацию из других адресов не приносят Зспеха, так как процессом управляет блок обработки, который должен быть готов к приему запросов. Когда блок обработки

принимает запрос на ввод информации, создается возможность перевода адреса из накопителя 8, куда он был предварительно записан, в блок / обработки.

В течение следующего цикла признак

передается вз накопителя 8 в блок обработки, если блок обработки не получил признака во время последнего цикла и когда он готов к приему признака. Если признак уже поступил из накопителя 8 в блок обработки, то в течение указанного следующего цикла признак передается из блока обработки в накопитель при условии, что имел место запрос на вывод данных и этот запрос поступил в блок обработки. В случае если запрос в блок обработки не поступил, то попытка выполнить этот запрос будет сделана в течение следующего цикла работы. Если запрос на вывод данных попал в блок обработки, то признак подается из

блока обработки в накопитель и основной запоминающий блок 5 через блок 9 выбора. После того как признаки передачи и приема отработаны для линии, адрес которой содержится в адресном регистре 2, адрес«ни регистр получает приращение и переводится, таким образом, к новому адресу.

В течение работы по второму принципу с блока обработки поступает адрес на адресный регистр 6, который, в свою очередь,

адресуется к основному запоминающему блоку 5 таким образом, что слово управления для линии, обращение к которой должно осуществляться, поступает в регистр 10 через блок 9 выбора. Одновременно с передачей слова из блока обработки в регистр 10, адресный регистр 6 адресует память из запоминающего блока 13.

Таким образом, одновременно с передачей слова управления в регистр 10 адресный регистр 6 осуществляет адресование к запоминающему блоку 13, так что из него в регистры 19, 20 и 21 поступает 8 битов приема, 8 битов передачи и 8 битов считывания.

В течение того же цикла 7 бит адресного регистра 5 организуется таким образом, что осуществляется обращение к слову данных в запоминающем блоке 5. Далее из регистра 21 передаются 8 битов считывания в

селеКТОО J8. я бит гцитыияиия кптппмй должен выходить ,из селектора 18, подается в регистр 10, работа которого разрешается адресными битами. Если поступает бит считывания для линии, к которой осуществляется обращение, то бит считывания пропускается через селектор .18, в регистр 10 записывается дополнительный сигнал. Если для линии связи, обращение к которой осуществлено, не поступает импульса считывания, то прибавление в регистре 10 не производится. Тот факт, что в регистре 10 дополнительно произведена запись, свидетельствует о том, что истек интервал суб-бита, т. е. одна седьмая часть интервала бита конкретной линии связи, к которой осуществлялось обращение. Принимаемый бит передается из запоминающего блока 13 в запоминающий блок 5. Регистр 10 проверяется на полный признак с помощью детектора 11, н выбранный бит записывается в запоминающий блок 5. раз, когда поступает бит, он передается из запоминающего блока 13 в запоминающий блок 5 независимо от числа, записанного в регистре 10. Таким образом, даже если принятый бит не выбран в средней точке и может быть ошибочным, он переводится из запоминающего блока 13 в запоминающий блок 5 при каждом прибавлении в регистре 10. Каждый из сигналов выбора независимо от того, относится ли выбор к средней точке бита, может быть записан в запоминающий блок 5, так как выбор бита, соответствующий средней точке бита, является последним отрезком бита, записанным по указанному адресу. Поступающий бит, следовательно, считывается в запоминающий блок 5 ,из запоминающего блока 13. Предложенное устройство обеспечивает повыщение эффективности выборки каналов связи для передачи и приема. Формула изобретения Устройство для уплотнения каналов связи, содержащее последовательно соединенные блок обработки данных, адресный регистр, первый селектор адреса и основной запоминающий блок, отличающееся тем, что, с целью обеспечения повышения эффективности выборки каналов связи для передачи и приема, введены дополнительный адресный регистр, линейный регистр управления адресом, накопитель данных, блок выбора считывание-запись информации, регистр управления, детектор полных символов, детектор состояния передачи, второй селектор адреса, запоминающий блок ввода-вывода, селектор приема, селектор передачи, блок декодирования, декодирующий блок передачи, селектор каналов, регистр приема, регистр передачи и регистр готовности, при этом дополнительные выходы блока обработки данных подключены соответственно через дополнительный адресный регистр и через линейный регистр управления адресом к дополнительным входам первого селектора адреса, одни выходы которого подключены к входам запоминающего блока ввода-вывода через второй селектор адреса, а другие выходы - к входам селектора приема, селектора каналов и декодирующего блока передачи, основной запоминающий блок соединен через блок выбора считывание-запись информации с накопителем данных, который соединен с блоком обработки данных, с одннм пз входов селектора передачи и с регистром управления, выходы которого подключены соответственно к другому входу селектора передачи и к входу детектора состояния передачи, к входу блока декодирования, выход которого подключен к управляющему входу основного запоминающего блока, и. к входу детектора полных символов, выход которого подключен к одному из управляющих входов блока выбора считывание-запись информации, а запоминаюпщй блок ввода-вывода соединен с регистром приема, выход которого через селектор приема подключен к другому управляюндему входу блока выбора считывание-запись информации, с регистром передачи, к другим входам которого подключены соответственно выход регистра управления через декодирующий блок передачи и выход селектора передачи, и с регистром готовности, выход которого через селектор каналов подключен к соответствующим входам регистра управления. Источник информации, принятый во внимание при экспертизе: 1. Патент СССР № 485611, кл. Н 04 М 3/22, опублик. 1969.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексное устройство для сканирования линий, работающих с различными скоростями передачи | 1973 |

|

SU1093264A3 |

| Устройство для адресации блоков памяти | 1973 |

|

SU676193A3 |

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛИРОВАНИЯ И ДЕКОДИРОВАНИЯ ВИДЕОСИГНАЛОВ | 1996 |

|

RU2172566C2 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ВИДЕОСИГНАЛОВ, КОДИРОВАННЫХ В РАЗНЫХ ФОРМАТАХ | 1996 |

|

RU2171548C2 |

| МИКРОЭВМ | 1991 |

|

SU1819017A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| СИСТЕМА ДЛЯ ОБРАБОТКИ КОМПОНЕНТ ПРОГРАММ И СХЕМА УПРАВЛЕНИЯ ПАМЯТЬЮ ДЛЯ ТРАНСПОРТНОГО ПРОЦЕССОРА | 1995 |

|

RU2145728C1 |

| Система для обмена информацией | 1990 |

|

SU1815646A1 |

| Система для сопряжения терминальных устройств с вычислительной машиной | 1973 |

|

SU510952A1 |

Авторы

Даты

1979-02-28—Публикация

1973-03-12—Подача