соединены соответственно с четвертым входом первого элемента И и третьим и первым входами второго и шестого элементов И, второй вход которого соединен с выходом пятого элемента И, выходы первого и второго элементов И соединены с первым и вторым входами первого элемента ИЛИ, выход которого соединен с первым входом первого триггера и через первый элемент, НЕ с первым входом седьмого элемента И, второй вход которого соединен с выходом второго элемента ИЛИ, первый второй и третий входы которого соединены соответственно с выходами третьего, четвертого и шестого элементов И, выход седьмого элемента И соединен с вторым входом первого триггера,

первый выход которого является третьим выходом блока и подключен к первым входам восьмого и девятого элементов И, выход восьмого элемента И является первым выходом блока, а второй вход через второй элемент НЕ соединен с выходом девятого элемента И, выход второго элемента НЕ яв ляется пятым выходом блока, второй вход девятого элемента И соединен с выходом второго триггера и первым входом десятого элемента И, второй которого соединен с вторым выходом первого триггера, который является четвертым выходом блока,выход десятого элемента И через третий элемент НЕ соединен с вторым выходом блока,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адресации блоков памяти | 1973 |

|

SU676193A3 |

| Устройство для приоритетного подключения источника информации к общей магистрали | 1976 |

|

SU1274634A3 |

| Многопроцессорная вычислительная система | 1987 |

|

SU1792540A3 |

| Устройство для сопряжения электронной вычислительной машины с дискретными датчиками | 1982 |

|

SU1084774A1 |

| Устройство для уплотнения каналов связи | 1973 |

|

SU650526A3 |

| МУЛЬТИПЛЕКСНАЯ СИНХРОННАЯ/АСИНХРОННАЯ ШИНА ДАННЫХ | 1989 |

|

RU2101865C1 |

| Устройство для управления распределенными объектами | 1985 |

|

SU1290261A1 |

| Устройство для ввода информации | 1985 |

|

SU1285457A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Скважинный инклинометр | 1990 |

|

SU1721225A1 |

1. МУЛЬТИПЛЕКСНОЕ УСТРОЙСТВО ДПЯ СКАНИРОВАНИЯ ЛИНИЙ, РАБОТАКЯЩХ С РАЗЛИЧНЫМИ СКОРОСТЯМИ ПЕРЕДАЧИ, содержащее память, соединенную двусторонней связью с линиями передачи данных, поделенными на группы в соответг ствии со скоростями передачи, адресный регистр, выход которого соединен с адресным входом памяти, генератор импульсов и блок управления, отличающееся тем, что, с целью,повьшения коэффициента использования оборудования и упрощения устройства, оно содержит три счетчика, дешифратор, элементы И, ИЛИ, триггеры, причем выход генератора импульсов соединен со счетными входами первого, второго и третьего счетчиков, входы сброса которых соединены с выходом элемента И сброса, первьй, второй и третий входы которого соединены соответственно с выходом дешифратора и первым и вторым выходами второго счетчика, вход запуска которого соединен с выходом генератора импульсов, разрядные выходы первого, второго и третьего счетчиков соединены соответственно с первыми входами первого, второго и третьего элементов И, выходы которьрс соединены с соответствующими входами элемента ИЛИ, -ВЫХОД которого соединен с входом адресного регистра, первый и второй выходы памяти соединены с входами первого и второго триггеров, выходы которых, а также выходы дешифратора и первый и второй выходы второго счетчика соединены соответственно с первым, вторым, третьим, четвертым и пятым входами блока управления, первый, второй, третий, четвертый и зпятый выходы которого соединены соответственно с входами запуска первого, СП третьего счетчиков, вторыми и третьис ми входами первого, второго и третьего элементов И, разрядные выходы второго счетчика соединены с входами дешифратора. 2. Устройство по п. 1, отличающе сея тем, что блок управления содержит десять элементов И, со со узел фиксации скорости линии, два триггера, два элемента ИЛИ и три элеrsD мента НЕ, причем первые входы первоО5 го, второго, третьего, четвертого и i4 пятого элементов И являютсячетвертым входом блока, вторые входы первого, третьего и пятого элементов И являются пятым входом блока. Третий вход первого и пятого и второй вход второго элементов И являются третьим входом блока, третий вход третьего и четвертый вход пятого элементов И являются первым входом блока, второй вход четвертого элемента И является вторым входом блока, первый и второй выходы узла фиксации скорости линии

1

Изобретение относится к системе связи, а именно к мультиплексору, используемому в этой системе для отпирания схемы передачи данных по соответствующим линиям связи, соединенным с системой.

Известно устройство, содержащее развертывающий узел, состояищй из трех взаимосвязанных блоков, в котором линии коммутации разделены на три группы, так что они могут обслуживаться при различных скоростях 1

Недостатком указанного устройства является то, что при каждом цикле развертьюающее устройство сканирует каждую линию лишь однажды.

Наиболее близким к предложенному является механическое устройство, в котором коммутатор работает с разной (Йсоростью, поддерживаемой в заданном соотношении Г2 3.

Недостаток указанного устройства. заключается в том, что не учитываетсяраспознавание каналов и поэтому должна осуществляться многократная передача механически в точном синхронизме .

Цель изобретения - повышение коэффициента использования оборудования и упрощение конструкции.

Поставленная цель достигается тем, что в мультиплексном устройстве

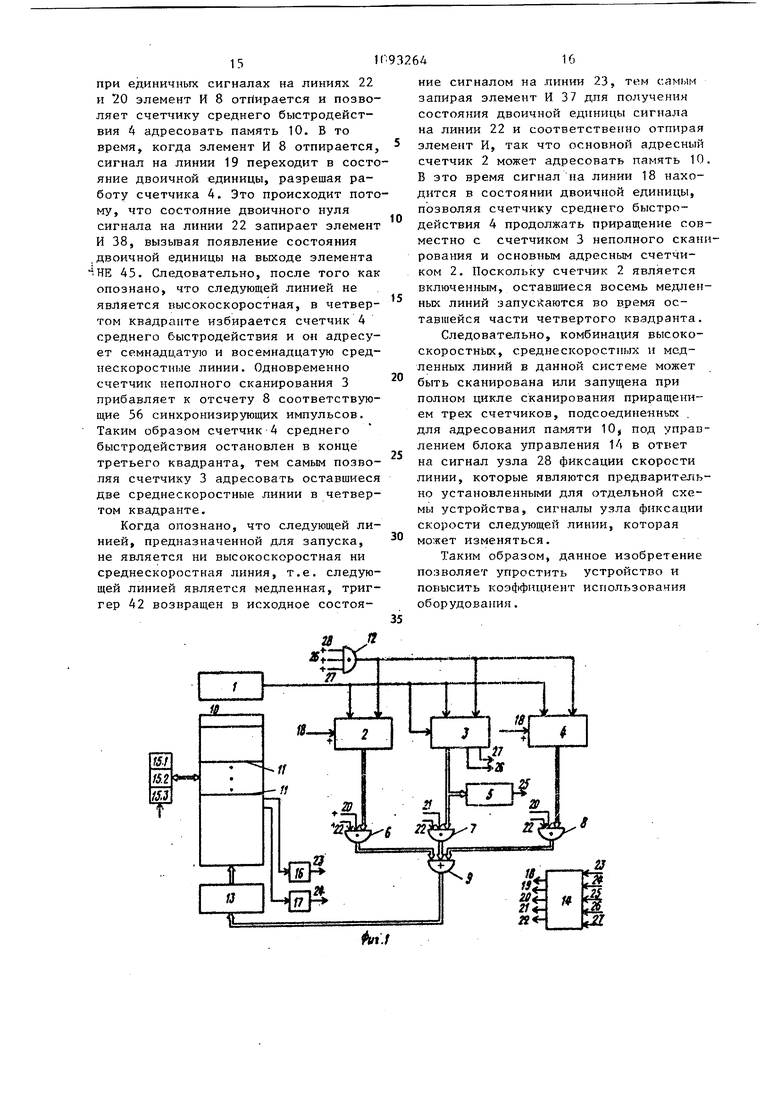

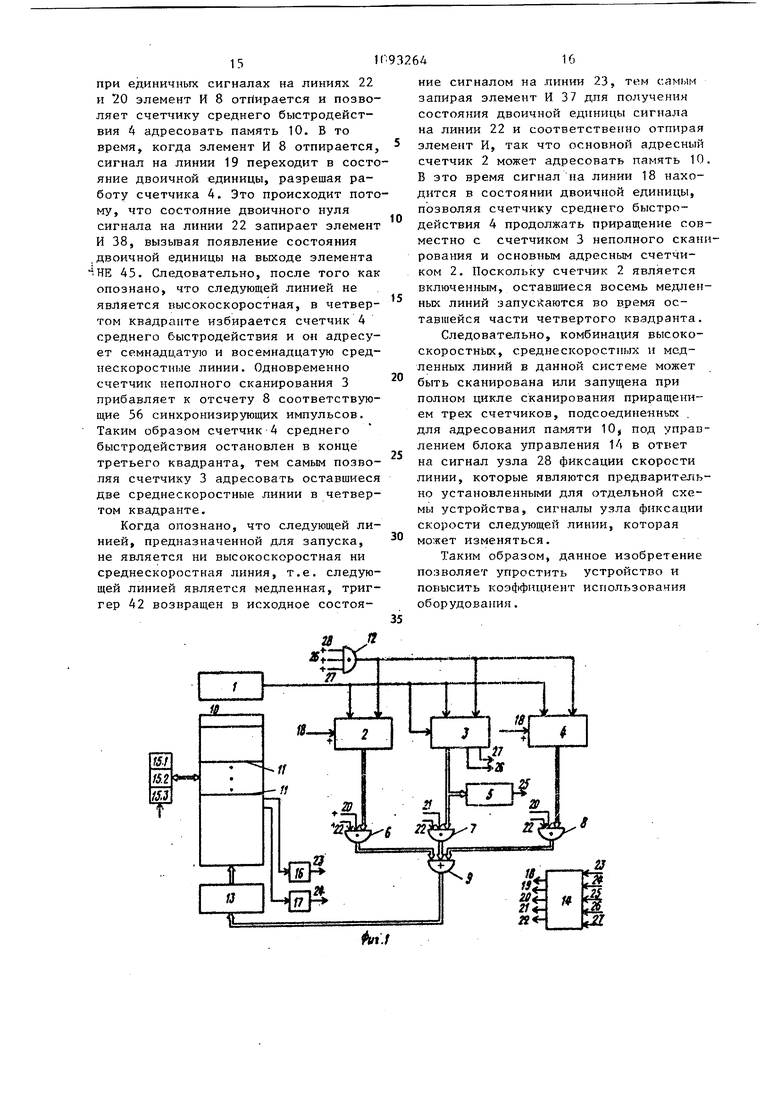

для сканирования линий, работающих с различными скоростями передачи, содержащем память, соединенную двусторонней связью с линиями передачи данных, поделенньми на группы в соответствии со скоростями передачи, адресный регистр, выход которого соединен с адресным входом памяти, генератор импульсов и блок управления, имеется три счетчика, дешифратор, элементы И, ИЛИ, триггеры, причем выход генератора импульсов соединен со счетными, входами первого, второго и третьего счетчиков, входы сброса которых соединены с выходом элемента И сброса, первьй, второй и третий входы которого соединены соответственно с выходом дещифратора и первым и вторым выходами второго счетчика, вход запуска которого соединен с выходомгенератора импульсов, разрядные выходы первого, второго и третьего счетчиков соединены соответственно с первыми входами первого, второго и третьего элементов И, выходы которых соединены с соответствующими входами элемента ИЛИ выход которого соединен с входом адресного регистра, первьй и второй выходы памяти соединены с входами первого и второго триггеров, выходы которых, а также выходы дешифратора и первый и второй выходы второ3го счетчика соединены соответственно с первым, вторым, третьим, четвертьтм и пятым входами блока управления, первый, второй, третий, четвертый и пятый выходы которого соединены соот ветственно с входами запуска первого третьего счетчиков, вторыми и третьи ми входами первого, второго и третье го элементов И, разрядные выходы второго счетчика соединены с входами дешифратора. Блок управления содержит десять элементов И, узел фиксации скорости линии, два триггера, два элемента ИЛИ и три элемента НЕ,- причем первые входы первого, второго, третьего, четвертого и пятого элементов И являются четверть1м входом блока, вторы входы первого, третьего и пятого эле ментов И являются пятым входом блока третий вход первого и пятого и второ вход второго элементов И являются третьим входом блока, третий вход третьего и четвертый вход пятого эле ментов И являются первым входом блока, второй вход четвертого элемента И является вторым входом блока, первый и второй выходы узла фиксации скорости линии, соединены соответственно с четвертым входом первого элемента И и третьим и первым входами второго и шестого элементов И, второй вход которого соединен с выходом пятого элемента И, выходы первого и второго элементов И соединены с первым и вторым входами первого элемента ИЛИ, выход которого соединен с первым входом первого триггера и через первый элемент НЕ - с первым входом седьмого элемента И, второй вход которого соединен с выходом второго элемента ИЛИ, первый, второй и третий входы которого соединены соответственно с выходами третьего, четвертого и шестого элементов И, выход седьмого элемента И соединен с вторым входом первого триггера, первьй выход которого является третьим выходом блока и подключен к первым входам восьмого и девятого элементов И, выход восьмого элемента И является первым выходом блока, а второй вход - через второй элемент НЕ соединен с выходом девятого элемента И, выход второго элемента НЕ являет,ся пятым выходом блока, второй вход девятого элемента И соединен с выходом второго триггера и первым входом 64 десятого элемента И, второй вход которого соединен с вторым выходом первого триггера,. который является четвертым выходом блока, выход десятого элемента И через третий элемент НЕ соединен с вторым выходом блока. На фиг. 1 изображено мультиплексное устройство для сканирования линий; на фиг. 2 - блок управления. Устройство ссэдержит генератор 1 импульсов, счетчики 2-4, дешифратор 5, элементы И 6-8, элемент ИЛИ 9,. память 10, ячейки 11 памяти, элемент И 12 сброса, адресный регистр 13, блок 14 управления, группы линий передачи данных 15.1-15.3, триггеры 16, 17, линии связи 18-27. Блок управления (фиг. 2) содержит узел 28 фиксации скорости линии эле- i менты И 29-38, элементы ИЛИ 39, 40, триггеры 41, 42, элементы -НЕ 43-45. Память 10 содержит.несколько ячеек 11, количество которых равно числу линий 13. Каждая ячейка 11 памяти 10 содержит информацию,относящуюся к принятьм данным, данным, предназначенным для передачи, битам управления и информации относительно скорости следующей линии, предназначенной для сканирования мультиплексным устройством. Это означает, что каждая ячейка 11 содер7кит по крайней мере три субъячейки, которые содержат соответ- -ственно данные, предназначенные для передачи.- Скорость следующей линии также содержится в субъячейке для каждой линии и эта информация передается в триггеры 16 и 17,посредством которых генерир- тотся сигналы управления по линиям 23. К памяти 10 также подсоединен адресный регистр 13, который подсоединяется для приема адреса, который выбирает одну из ячеек 11 в памяти 10, так что данные могут быть переданы по адресным линиям. Адрес ячейки принимается регистром 13 через элемент ИЛИ 9 и через элементы И 6, 7 и 8 от основного счетчика 2, счетчика 3 неполного сканирования и счетчика 4 средней скорости. Генератор импульсов 1 служит для обеспечения синхронизирующих импульсов, которые дополняют каждый из счетчиков 2-4, при работе устройства. Счетчик неполного сканирования 3 также отпирается сихронизирующими Импульсами и также дополняется, в то время как основной счетчик 2 и счетчик средней скорости 4 дополняются только после приема сигналов управления от блока управления 14, как показано на фиг. 2. Основной счетчик 2является счетчиком на шесть бит, который образует адрес, обладающий способностью адресации, например, 64-х линий. Основным назначением счетчика 2 является отпирание линии 15.1 малого быстродействия. Счетчик 3неполного сканирования является также счетчиком на шесть бит, которы образует адрес из четырех бит для адресации, например, до шестнадцати высокоскоростных линий 15.3. Пятый бит, образованный счетчиком неполног сканирования 3, образует сигнал на линии 26, тогда как шестой бит образует сигнал на линии 27. Эти сигналы соответственно используются для указания того, что первые четыре бита счетчика 3 сброшены. Эти сигналы указывают соответствующие интервалы или квадранты полного цикла сканирования; Когда четыре бита на выходе счетчика 3 находятся в состоянии дво ичной единицы, это декодируется дешифратором 5, который может быть просто элементом И, тем самым генери рун состояние бинарной единицы выхода квадрантного сигнала на линии 25 Среднескоростной счетчик 4 образует адрес из пяти бит, используется в особенности для формирования адреса например, до 32-х среднескоростных линий в течение интервала сканирования. Счетчик 4 используется для отпирания среднескоростных линий только при определенных условиях. Прохождение адресов со счетчиков 2-4 через элементы И 6,7 или 8 разрешается соответствующими состояниями сигналов управления на линиях 22, 20 и 21 (+ указывает на то, что состояние двоичной единицы отпирает устройство, а - на то, что состояние двоичного нуля отпирает устройство). Адрес затем принимается регистром 13, который выбирает одну из ячеек 11 памяти 10. Затем в зависимости от операций данные принимаются или передаются по адресной линии линий 15. Линии могут быть высокоскоростные, среднескоростные или медленные или могут быть сочетанием

таких скоростей. Может быть до 64 медленных линий, использованных с системой, если не используются высоприращения посредством генератора импульсов 1, одна ячейка 11 памяти 10 отпирается на время,достаточное коскоростные или среднескоростные линии, или до 32 среднескоростных, если нет медленных или высокоскоростных; линий, до 16 высокоскоростных, если нет медленных или среднескоростных линий. Следовательно, каждая из среднескоростных линий замещает две медленные, в то время как каждая высокоскоростная замещает четыре медленные. Медленные линии могут передавать или принимать данные в частотном диапазоне с максимальной частотой 2700 бит/с, среднескоростные 5400 бит/с и высокоскоростные 10.800 бит/с.Следовательно, имеет место взаимосвязь 2:1 и 4:1 частот соответствующих линий. Частота передачи является одной из трех максимальных частот, не взирая на частоту, требуемую для отдельной линии. Например, в случае самых высоких частот 5400-10. 800 бит/с, если частота передачи данных отдельной линии 9000 бит/с, то фактически эти данные будут переданы на максимальной частоте 10.800 бит/с. Частотное группирование различных линий может быть как больше, так и меньше указанных трех групп частот, и число линий, подсоединенных к устройству, может быть больше или меньше 64 линий. В течение одного полного сканирования линий высокоскоростные линии должны быть запущены четыре раза в равные интервалы, в то время как среднескоростные линии должны быть запущены два раза в течение полного сканирования. Линии медленной скорости требуют только одного запуска или эксплуатации во время полного сканирования всех линий. Следовательно, устройство использует сканирующее устройство, которое разделяет полное сканирование на четьфе подынтервала или квадранты. Может быть различное количество субинтервалов. Во время каждого квадранта высокоскоростные линии эксплуатируются один раз. В течение первого и третьего квадрантов эксплуатируются среднескоростные линии и медленные линии эксплуатируются в соответствующей последовательности, которая остается после того, как эксплуатируются высокоскоростные и среднескоростные линии. Каждый раз, как счетчики получают 71 для запуска передачи данных. Основно I счетчик 2 получает приращения 64 раза перед тем, как оно автоматически возвращается в исходное положение, а счетчик 4 для средних скоростей 32 раза. Счетчик неполного сканирования 3 является аналогичным основному счет.чику 2 в том, что он полностью возвращается в исходное положение по ле приращения 64 раза. Счетчики могут также быть установлены в положение О (в положение сброса) состоянием двоичной единицы, принятым от элемента И 12 сброса в конце четвертого квадранта. Четьфе младших разряда счетчика 3 возвращаются в исходное положение четьфе раза в течение 64 приращений счетчика 3. Следовательно, каждый раз, когда четыре младших разряда счетчика 3 устанавливаются в положение О,.происходит 16 приращений отсчетов счетчика 3. Каждый из 16 отсчетов определяют квадрант. После первых 16 отсчетов сигнал на линии 26 (переходит в состояние двоичной единицы, после вторых 16 отсчетов в состояние двоичного нуля, сигнал на выходе 27 переходит в состояние двоичной единицы и т.д. до тех пор, пока все биты не будут возвращены в исходное положение в конце четвертого квадранта. В конце каждого квадранта четьфе старших разряда -счетчика 3 являются двоичными единицами, которые затем генерируют сигнал на линии 25. В начале второго квадранта сигнал на линии 26 находится в состоянии двоичной единицы, которое указывает совместно с фактом, что сигнал на линии 27 находится в состоянии двоичного -нуля, что это является вторым квадрантом. Первый квадрант индицируется, когда оба сигнала на линиях 26 и 27 находятся в состоя нии двоичного нуля. В начале третьег квадранта сипнал SSCSA на линии 26 находится в состоянии двоичного нуля и сигнал SSCSB на линии 27 переходит в состояние двоичной единицы указывая, что это является третьим квадрантом. В начале четвертого квадранта сигналы на линиях 26 и 27 оба находятся в состоянии двоичной единицы указывая, что это является четвертым квадрантом.Прежде всего каждая из высокоскоростных линий запускается в каждом квадранте, после чего эксплуа 64 тируются среднескоростные линии и линии медленные в оставшееся время. В качестве примера рассмотрим устройство, в котором имеется шесть высокоскоростных линий, двенадцать среднескоростных и шестнадцать медленных. В течение первого квадранта вводятся в эксплуатацию шесть высокоскоростные, линий и десять среднескоростных. В течение второго квадранта эксплуатируются шесть высокоскоростных линий снова и две оставшиеся среднескоростные. Затем эксплуатируются восемь медленных линий. В течение третьего квадранта эксплуатируются гаесть высокоскоростных линий и десять среднескоростных. В течение четвертого квадранта шесть высокоскоростных линий четвертый раз, в товремя; как оставшиеся две среднескоростные линии эксплуатируются снова и затем восемь оставшихся медленных линий. Таким образом, в конце четьфех квадрантов, т.е. по окончании полного сканирования линий, шесть высокоскоростных линий эксплуатируются четьфе раза каждая, двенадцать среднескоростных дважды каждая, шестнадцать медленных каждая один раз. Основной счетчик адресов 2 иногда используется для адресования каждого типа линии, в то время как счетчик неполного сканирования 3 может быть использован для адресования высокоскоростных и среднескоростных типов линий.Среднескоростной счетчик запускается только для адресования памяти 10 в течение четвертого квадранта, если общее число высокоскоростных и среднескоростных линий больше шестнадцати. Каждый из счетчиков 2-4 повторно устанавливается в нулевое состояние в конце четвертого квадранта и полное сканирование осуществляется снова. Основной счетчик 2 обладает способностью счета от 1 до 64 (в действительности счетчик наращивает от О до 63, после чего возвращается в нулевое состояние,однако для пояснения принято, что каждый из счетчиков после установки в исходное положение указывает 1, тем самым определяя первую линию) и счетчик 2 соединяется с двумя медленными линиями. Счетчик 2 может быть остановлен блоком управления 14 для запоминания следующей медленной линии, предназначенной для эксплуатации. Счетчик 3 сое10диняется с высокоскоростными линиями и отсчитывает (самые меньшие значения четьфе биты) от 1 до 16 в течение каждого из четьфех квадрантов. Счетчиком 3 формируются два сигнала .на линиях 26 и 27, которые обозначают четыре квадранта. Среднескоростной счетчик 4 отсчитывает от 1 до 32 и может быть остановлен аналогичным образом, как и основной счетчик 2. Обычно в работе основной счетчик 2 всегда работает в первом квадранте и считает от 1 до 16. Одновременно счетчик неполного ск нирования 3 также отсчитьшает от 1 до 16. С целью упрощения схемы устройства высокоскоростные линии принимают самые низкие числовые обозначения, это значит,что высокоскоростные линии обозначаются числами 1, хотя в данном примере име ется шесть высокоскоростных линий,и среднескоростные линии затем обозначаются следующими числами 7-18, последовательно для 12 среднескоростных линий. Медленные линии принимают последующие числовые обозначения. В конце первого квадранта, если имеютс какие-либо высокоскоростные линии в системе, счетчик 3 выбирается на следующий отсчет. Также в этот момен основной счетчик 2 останавливается и нпадшие четыре разряда счетчика неполного сканирования 3 автоматически устанавливаются в исходное состояние Таким образом сканируются высокоскоростные линии и отсчет следующей Сре нескоростной линии или медленной линии запоминается. Во время второго квадранта счетчик неполного сканирования 3 работает до тех пор, пока не будет опознано, что следующей линией не является высокоскоростная линия, как указано сигналами на линиях 23 и 24, которые имеют соответственно следуюшзие двоичные состояния, для медленных линий 0,0; для среднескоростных 1,0; для высокоскоростных 1,1. Основной счетчик 2 затем включается, если следующей не является линия высокоскоростного диапазона. В конце второго квадранта, если имеются высокоскоростные или среднескоростные линии, счетчик неполного ска нирования 3 выбирается для запуска линий в начале квадранта три и основ ной счетчик 2 останавливается. Во время третьего квадранта счетчик неполного сканирования 3 работает до тех пор, пока сигнал на линии 23 не 410 укажет, что следующая линия не является высокоскоростной или среднескоростной. Для большинства систем счетчик неполного сканирования 3 управляет или отпирает обе среднескоростную и высокоскоростную линии, так что Среднескоростной счетчик 4 никогда не включается через элемент И 8 до тек пор, пока число высокоскоростных и среднескоростных линий в комбинации не превысит шестнадцати. Обычно в конце третьего квадранта основной счетчик 2 снова останавливается и счётчик 3 неполной развертки выбирается для сканирования высокоскоростных линий в начале четвертого квадранта. Однако если общее число высокоскоростных и среднескоростных линий больше 16, как в примере, требуется счетчик среднего быстродейстВИЯ. в этом случае будет несколько среднескоростных линий для эксплуатации в четвертом квадранте после того, как сначала эксплуатируются высокоскоростные линии. При этих условиях счетчик 3 избирается для полного третьего квадранта. В начале четвертого квадранта счетчик 3 неполного сканирования автоматически возвращается в исходное состояние и обслуживает высокоскоростные линии, счетчик среднего быстродействия в это время остановлен. Блок управления 14 запоминает, что имеются еще среднескоростные линии для эксплуатации. Когда сигнал на линии 24 указывает, что следующая линия не является высокоскоростной, счетчик среднего быстродействия 4 включается и адресует память 10 до тех пор, пока сигнал на линии 23 не укажет, что следующей является медленная линия. Наконец, основной счетчик 2 адресует оставшиеся медленные линии, предназначенные для передачи данных. Блок управления 14 содержит триггер 41, который после возвращения в исходное состояние генерирует состояние двоичной единицы на линии 20. В начале первого квадранта, т.е. при исходных условиях, сигналы на линиях 18 и 19 находятся в состоянии двоичной единицы. Основной счетчик 2 и счетчик среднего быстродействия 4 запускаются, счетчики 2 и 4 считают тактовые импульсы генератора 1, счетчик 3 неполного сканирования также запускается генератором 1 импульсов. Пр) исходных условиях сигнал на лиНИИ 20 находится в состоянии двоичной единицы и сигнал на линии 22 находится в состоянии двоичной единицы тем самым отпирая элемент И б н позволяя основному счетчику 2- адресо,вать память 10 через регистр 13 н элемент ИЛИ 9, Сигнал на линии 20 находится в состоянии двоичной единицы так как триггер 41 первоначаль но возвращен в исходное состояние в конце четвертого квадранта. Триггер 42 также возвращен в исходное состоя ние, тем генерируя состояние двоичного нуля на входе элемента И 37 и состояние двоичной единицы на выходе элемента НЕ 44. Соответственн во время первого отсчета синхронизирующих импульсов, как вщ1.но на указанном примере, основной счетчик 2 имеет на выходе сигнал 1, счетчик 4 среднего быстродействия и счетчик 3 неполного сканирования также имеют на выходах 1 и первая линия запускается для передачи данных по первой высокоскоростной линии. Выбранным счетчиком является основной счетчик адресов 2 и отсчет продолжается до 16 во время первого квадранта, В течение этого времени шесть высокоскоростных линий и десять из двенадцати среднескоростных запускаются для перед ахш данных. В конце первого квадранта сигнал на линии 20 переходит в состояние двоичного нуля. Это происходит поскольку триггер 41 установлен через элемент ЕПИ 39, так как элемент И 30 является открытьм. Отпирание элемента И 30 или 29 запирает элемент И 35 посредством элемента НЕ 43. Элемент И 30 отпирается, так как узел 28 фиксации скорости линии показывает, что линия является именно высокоскоростной и из-за генерирования сигналов на линиях 26 и 25. Узел 28 фиксации скорости линии (которым могут быть два триггера) первоначально фиксирует скорость самой быстродейст вующей линии. В примере самой быстро действующей линией является высокоскоростная и соответственно сигналы на его выходах находятся в состоянии двоичной единицы. Сигналы с первого и второго выходов узла 28 имеют соот ветственно следующие двоичные состоя ния: для медленных линий 0,0; для скоростных 0,1. Сигнал на линии 26 указывает, что это является первым или третьим квадрантом,в то время как , сигнал на линии 27 указывает, что это конец квадранта. Поскольку триггер 41 установлен в заданное состояние, сигнал на линии 18 переходит в состояние двоичного нуля вследствие (Запирания элемента И 36. Соответственно основной счетчик 2 остановлен. Следовательно, в начале второго квадранта основной счетчик 2 адресов запирается и счетчик 3 неполного сканирования избирается для адресования памяти 10 отпиранием элемента . И 7. Соответственно в начале второго квадранта синхронизирующие импульсы поступают на основной счетчик 2, счетчик 4 среднего быстродействия и счетчик 3 неполного сканирования шестнадцать раз и растр сканирования линий указьгоаат, что первые шесть линий отпираются посредством счетчика 3 неполного сканирования. Когда опознается, что следующей линией, предназначенной для отпирания, не является высокоскоростная, элемент И 32 отпирается благодаря сигналам на линиях 24 и 26, этим указывается, что это является вторым квадрантом, соответственно, поскольку элемент И 32 отпирается, триггер 41 устанавливается повторно в исходное состояние через элемент ИЛИ 40 и отпирает элемент И 35. Другие входные сигналы элемента И 35, которые являются выходными сигналами элемента НЕ 43, находятся в состоянии двоичной единицы, поскольку ни одно из условий для отпирания элементов И 30 или 29 полностью не удовлетворяется. Соответственно установкой в исходное состояние триггера 41 сигнал на линию 20 переходит в состояние двоичной единицы. Состояние двоичной единицы сигналов на линиях 20 и 22 затем запускает адресование памяти 10 через основной счетчик 2. Сигнал .на линии 18 тагаке переходит в состояние двоичной единицы вследствие.отпирания элемента И 36. , В течение первых семи отсчетов синхронизирующих импульсов второго квадранта, т.е. число отсчетов синхронизирующих импульсов 17-23, основной адресный счетчик 2 указывает адрес 17. Счетчик среднего быстродействия 4 указывает адрес 23 на седьмом отсчете второго квадранта, в то время как счетчик 3 неполного сканирования указывает адрес 7. Соответственно, поскольку основной адресный счетчик 2 выбирается, отпи131рается семнадцатая линия. Основной счетчик адресов 2 продолжает работать во время оставшейся части второго квадранта,в конце которого запускается линия связи. Нужно заметить, что семнадцатая и восемнадцатая линии являются оставшимися двумя среднескоростными, которые могут быть запущены во время первог о квадранта. Линии с девятнадцатой по двад цать шестую являются первыми восемью медленными линиями. Как будет видно, остальные восемь медленных линий адресованы в конце етвертого квадранта. В конце- второго квадранта, если имеются высокоскоростные или среднескоростные линии, счетчик неполного сканирования 3 адресует память 10 и основной счетчик 2 останавливается на адресе 27. Это происходит потому, что триггер 41 включен. Триггер 41 включается, так как элемент И 29 отпирается сигналами на линиях 26 и 27, которые указывают, что это второ квадрант; сигнал на линии 25 указывает, что это конец квадранта, и сигнал на первом выходе узла 28 указывает, что все линии не являются медленными. Поскольку сигнал на линии 20 находится в состоянии двоично го нуля, это запирает элемент И 36 и соответственно состояние сигнала на линии 18 является состоянием двоичного нуля, тем самым останавливающим основной адресный счетчик 2.Следовательно, в начале третьего квадранта счетчик неполного сканирования 3 запускается через элемент И 7 для адресования памяти 10. Основной адресный счетчик остановлен. Когда отсчет синхронизирующих импульсов осуществляется от 33 до 48, то счетчик 3 неполного сканирования и счетчик 4 среднего быстродействия приращиваются от единицы до шестнадцати в то время как основной адресньй счетчик 2 остановлен на отсчете 27. Линии, запущенные счетчиком неполного сканирования 3, являются высокоскоростными и первыми десятью среднескоростными линиями. В конце третьего квадранта элемент Н 30 снова открывается, посколь ку самой быстродействующей линией является высокоскоростная и поскольку это является концом третьего квадранта, тем самым устанавливается триггер 41 и сигнал на линии 20 4 переходит в состояние двоичной единицы, частично отпирая элемент И 33. Также в конце третьего квадранта элемент И 33 отпирается, так как генерируются сигналы на линиях 26 и 27, которые указывают, что это является именно третьим квадрантом, сигнал на линии 25 указывает на то, что это конец,третьего квадранта. Следующей линией является среднескоростная или высокоскоростная, как указано сигналом на линии 23. Отпирание элемента И 33 частично отпирает элемент И 34 и устанавливает триггер 42, чем полностью отпирает элемент И 38 и вызывает состояние двоичного нуля на выходе элемента НЕ 45. Сигнал на линии 18 вынуждает счетчик 4 среднего быстродействия остановиться. Поскольку сигнал на линии 20 находится в состоянии двоичной единицы и элемент И 37 запирается, сигнал на линии 22 находится в состоянии двоичной единицы, элемент И 7 отпирается и счетчик неполного сканирования 3 избирается в начале четвертого квадранта, тем самым позволяя счетчику 3 неполного сканирова-нуя адресовать память 10.В начале четвертого квадранта запускаются первые шесть линий, т.е. высокоскоростные. Во время запуска этих линий в четвертом квадранте отсчет синхронизирующих импульсов увеличивается от 49 до 54, основной адресньй счетчик 2 остается,остановленным на счете 27 и счетчик 3 неполного сканирования отсчитывает от 1 до 6, тем самым адресуя память 10 и запуская первые шесть линий. Счетчик 4 среднего быстродействия остается остановленным на семнадцатой линии. Когда опознается, что следующей линией не является высокоскоростная, элемент И 32 отпирается, так как сигнал на линии 24 находится в состоянии двоичного нуля и сигнал на линии 26 находится в состоянии двоичной единицы, указывая на то, что это является четвертым квадрантом. Это возвращает в исходное состояние триггер 41, принуждая сигнал на линии 20 перейти в состояние двоичной единицы. Поскольку сигнал на выходе триггера 42 остается в состоянии двоичной единицы, соответственно отпирается элемент И 37 и сигнал на линии 22 переходит в состояние двоичного нуля. Соответственно

при единичных сигналах на линиях 22 и 20 элемент И 8 отйирается и позволяет счетчику среднего быстродействия 4 адресовать память 10. В то время, когда элемент И 8 отпирается, сигнал на линии 19 переходит в состояние двоичной единицы, разрешая работу счетчика 4. Это происходит потому, что состояние двоичного нуля сигнала на линии 22 запирает элемент И 38, вызывая появление состояния двоичной единицы на выходе элемента НЕ 45. Следовательно, после того как опознано, что следующей линией не является 1 ысокоскоростная, в четвертом квадранте избирается счетчик 4 среднего быстродействия и он адресует семнадцатую и восемнадцатую среднескоростные линии. Одновременно счетчик неполного сканирования 3 прибавляет к отсчету 8 соответствующие 56 синхроршзирушщих импульсов. Таким образом счетчик 4 среднего быстродействия остановлен в конце третьего квадранта, тем самым позволяя счетчику 3 адресовать оставшиеся ве среднескоростные линии в четвертом квадранте.

Когда опознано, что следующей линией, предназначенной для запуска, не является ни высокоскоростная ни среднескоростная линия, т.е. следуюей линией является медленная, тригер 42 возвращен в исходное состояние сигналом на линии 23, тем самым запирая элемент И 37 для получения состояния двоичной единицы сигнала на линии 22 и соответственно отпирая элемент И, так что основной адресный счетчик 2 может адресовать память 10. В это время сигнал на линии 18 находится в состоянии двоичной единицы, позволяя счетчику среднего быстро0действия 4 продолжать приращение совместно с счетчиком 3 неполного сканирования и основным адресным счетчиком 2. Поскольку счетчик 2 является включенным, оставшиеся восемь медлен5ных линий запускаются во время оставшейся части четвертого квадранта. Следовательно, комбинация высокоскоростных, среднескоростных и медленных линий в данной системе может

0 быть сканирована или запущена при полном цикле сканирования приращением трех счетчиков, подсоединенных для адресования памяти 10, под управлением блока управления 14 в ответ

5 на сигнал узла 28 фиксации скорости линии, которые являются предварительно установленными для отдельной схемы устройства, сигналы узла фиксации скорости следующей линии, которая

0 может изменяться.

Таким образом, данное изобретение позволяет упростить устройство и повысить коэффициент использования оборудования.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3229259$ кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Полимерная композиция | 1983 |

|

SU1199770A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-05-15—Публикация

1973-10-15—Подача