истр 15, состоящий из триггеров 16 17.

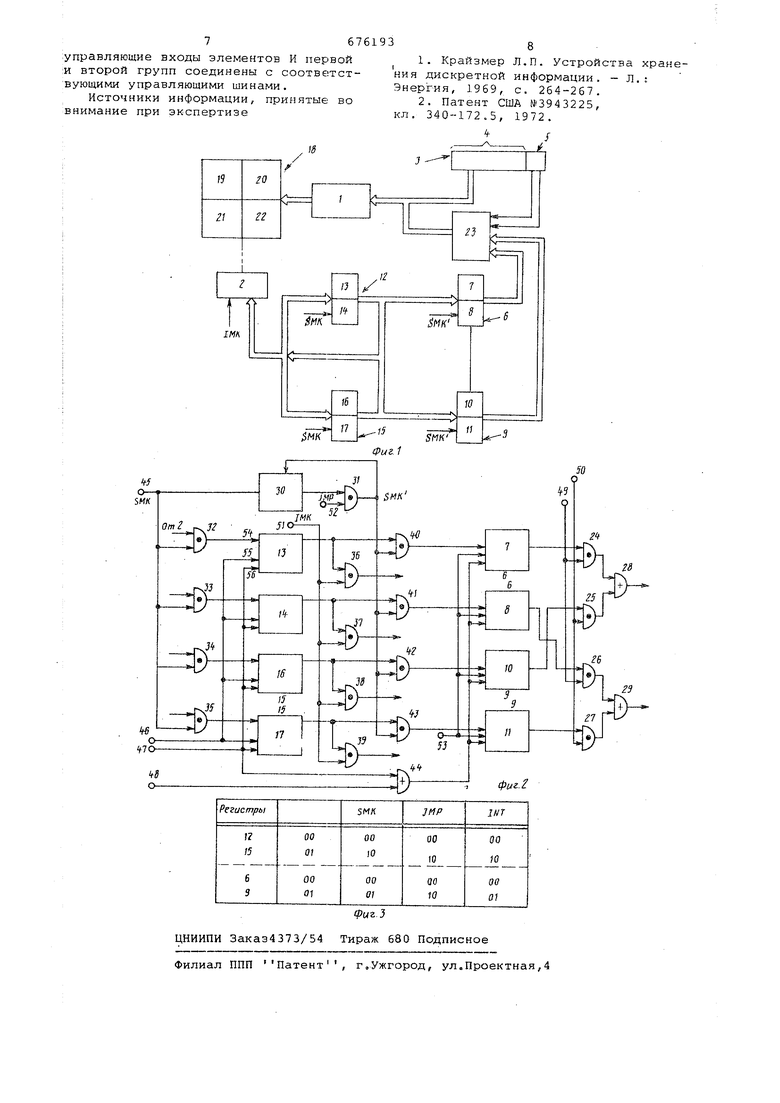

Регистры 1 и 2 подключаются к блоу памяти 18, состоящему из полей 9-22.

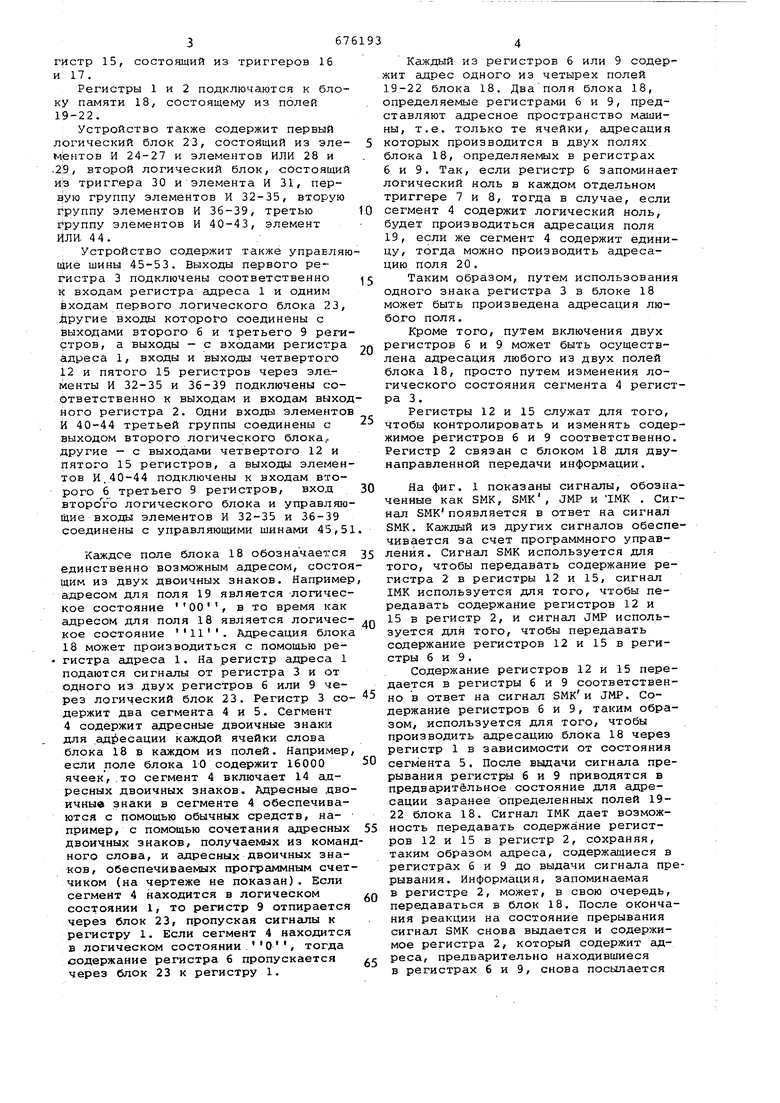

Устройство также содержит первый огический блок 23, состоящий из эле- 5 ентов и 24-27 и элементов ИЛИ 28 и 9, второй логический блок, состоящий э триггера 30 и элемента И 31, первую группу элементов И 32-35, вторую группу элементов И 36-39, третью 10 группу элементов И 40-43, элемент ИЛИ. 44.

Устройство содержит также управляющие шины 45-53. Выходы первого регистра 3 подключены соответственно 5 к входам регистра-адреса 1 и одним входам первого логического блока 23, ilpyrae входы которого соединены с выходами второго 6 и третьего 9 регистров, а выходы - с входами регистра п адреса 1, входы и выходы четвертого 12 и пятого 15 регистров через элементы И 32-35 и 36-39 подключены соответственно к выходам и входс1М выходного регистра 2. Одни входы элементов И 40-44 третьей группы соединены с выходом второго логического блока,, другие - с выходами четвертого 12 и пятого 15 регистров, а выходы элементов И. 40-44 подключены к входам второго б третьего 9 регистров, вход 30 BTOpoYo логического блока и управляющие входы элементов И 32-35 и 36-39 соединены с управляющими шинами 45,51,

Каждое поле блока 18 обозначается 35 единственно возможным адресом, состоящим из двух двоичных знаков. Например, адресом для поля 19 является логическое состояние 00 , в то время как адресом для поля 18 является логичес- Q кое состояние 11 . Адресация блока 18 может производиться с помощью регистра адреса 1. На регистр адреса 1 подаются сигналы от регистра 3 и от одного из двух регистров 6 или 9 через логический блок 23. Регистр 3 со- 5 держит два сегмента 4 и 5. Сегмент 4 содержит адресные двоичные знаки для адресации каждой ячейки слова блока 18 в каждом из полей. Например, если поле блока ГО содержит 16000 SO ячеек, .то сегмент 4 включает 14 адресных двоичных знаков. Адресные двоичные знаки в сегменте 4 обеспечиваются с помощью обычных средств, например, с помощью сочетания адресных 55 двоичных знаков, получаемых из командного слова, и адресных двоичных знаков, обеспечиваемых прогрг ммным счетчиком (на чертеже не показан). Если сегмент 4 находится в логическом Q состоянии 1, то регистр 9 отпирается через блок 23, пропуская сигналы к регистру 1. Если сегмент 4 находится

тогда

в логическом состоянии

содержание регистра 6 пропускается через блок 23 к регистру 1.

Каждый из регистров 6 или 9 содержит адрес одного из четырех полей 19-22 блока 18. Дваполя блока 18, определяемые регистрами 6 и 9, представляют адресное пространство машины, т.е. только те ячейки, адресация которых производится в двух полях блока 16, определяемых в регистрах 6 и 9. Так, если регистр 6 запоминает логический ноль в каждом отдельном триггере 7 и 8, тогда в случае, если сегмент 4 содержит логический ноль, будет производиться адресация поля 19, если же сегмент 4 содержит единицу, тогда можно производить адресацию поля 20.

Таким образом, путем использовани одного знака регистра 3 в блоке 18 может быть произведена адресация любого поли.

Кроме того, путем включения двух регистров 6 и 9 может быть осуществлена адресация любого из двух полей блока 18, просто путем изменения логического состояния сегмента 4 регистра 3.

Регистры 12 и 15 служат для того, чтобы контролировать и изменять содержимое регистров 6 и 9 соответственно Регистр 2 связан с блоком 18 для двунаправленной передачи информации.

На фиг. 1 показаны сигналы, обозначенные как SMK, SMK, JMP и ЧМК . Сигнал SMK появляется в ответ на сигнал SMK. Каждый из других сигналов обеспечивается за счет программного управления. Сигнал SMK используется для того, чтобы передавать содержание регистра 2 в регистры 12 и 15, сигнал IMK используется для того, чтобы передавать содержание регистров 12 и 15 в регистр 2, и сигнал JMP используется для того, чтобы передавать содержание регистров 12 и 15 в регистры 6 и 9.

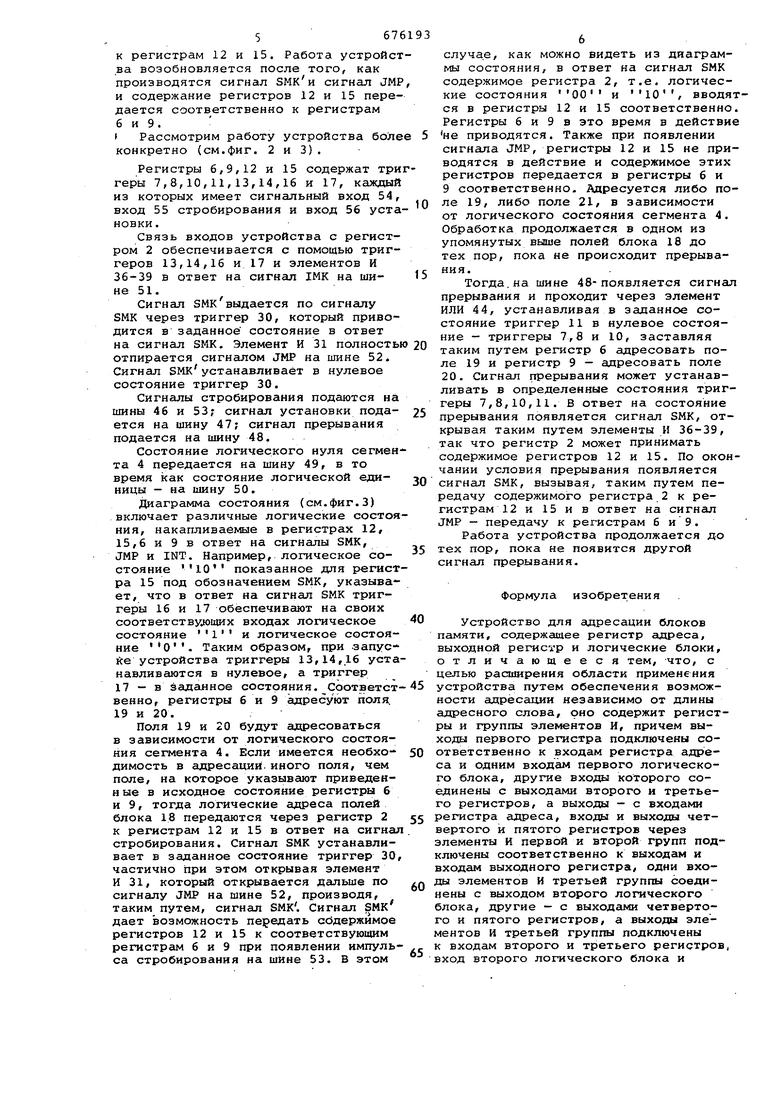

Содержание регистров 12 и 15 передается в регистры 6 и 9 соответственно в ответ на сигнал SMKи JMP. Содержание регистров 6 и 9, таким образом, используется для того, чтобы производить адресацию блока 18 через регистр 1 в зависимости от состояния сегмента 5. После выдачи сигнала прерывания регистры 6 и 9 приводятся в предварительное состояние для адресации заранее определенных полей 1922 блока 18. Сигнал IMK дает возможность передавать содержание регистров 12 и 15 в регистр 2, сохраняя, таким образом адреса, содержащиеся в регистрах 6 и 9 до выдачи сигнала прерывания. Информация, запоминаемая в регистре 2, может, в свою очередь, передаваться в блок 1В. После окончания реакции на состояние прерывания сигнал SMK снова выдается и содержимое регистра 2, который содержит адреса, предварительно находившиеся в регистрах 6 и 9, снова посылается 567 к регистрам 12 и 15. Работа устройс ва возобновляется после того, как производятся сигнал ЗМКи сигнал JM и содержание регистров 12 и 15 пере дается соответственно к регистрам 6 и 9. Рассмотрим работу устройства бол конкретно (см.фиг. 2 и 3). Регистры 6,9,12 и 15 содержат тр геры 7,8,10,11,13,14,16 и 17, кажды из которых имеет сигнальный вход 54 вход 55 стробирования и вход 56 уст новки. Связь входов устройства с регист ром 2 обеспечивается с помощью триг геров 13,14,16 и17 и элементов И 36-39 в ответ на сигнал IMK на шине 51. Сигнал SMK выдается по сигналу SMK через триггер 30, который приво дится в заданное состояние в ответ на сигнал SMK, Элемент И 31 полность отпирается сигналом JMP на шине 52. Сигнал SMK устанавливает в нулевое состояние триггер 30. Сигналы стробирования подаются на шины 46 и 53; сигнал установки подается на шину 47; сигнал прерывания подается на шину 48. Состояние логического нуля сегмен та 4 передается на шину 49, в то время как состояние логической единицы - на шину 50. Диаграмма состояния (см.фиг.З) включает различные логические состоя ния, накапливаемые в регистрах 12, 15,6 и 9 в ответ на сигналы SMK, JMP и INT. Например, логическое состояние 40 показанное для регист ра 15 под обозначением SMK, указывает, что в ответ на сигнал SMK триггеры 16 и 17 обеспечивают на своих соответству.ю1цих входах логическое и логическое состоясостояниеt п ние О. Таким образом, при запусйе устройства триггеры 13,14,16 уста навливаются в нулевое, а триггер 17 - в заданное состояния. Соответст венно, регистры 6 и 9 адресуют поля. 19 и 20. Поля 19 и 20 будут адресоваться в зависимости от логического состояния сегмента 4. Если имеется необходимость в адресации, иного поля, чем поле, на которое указывают приведенн ые в исходное состояние регистры 6 и 9, тогда логические адреса полей блока 18 передаются через регистр 2 к регистрам 12 и 15 в ответ на сигна стробирования. Сигнал SMK устанавливает в заданное состояние триггер 30 частично при этом открывая элемент И 31, который открывается дальше по сигналу JMP на шине 52, производя, таким путем, сигнал SMK. Сигнал SMK дает возможность передать содержимое регистров 12 и 15 к соответствующим регистрам 6 и 9 при появлении импуль са стробирования на шине 53. В этом случае, как можно видеть из диаграммы состояния, в ответ на сигнал SMK содержимое регистра 2, т.е. логические состояния ОО и 10, вводятся в регистры 12 и 15 соответственно. Регистры 6 и 9 в это время в действие не приводятся. Также при появлении сигнала JMP, регистры 12 и 15 не приводятся в действие и содержимое этих регистров передается в регистры 6 и 9 соответственно. Адресуется либо поле 19, либо поле 21/ в зависимости от логического состояния сегмента 4. Обработка продолжается в одном из упомянутых выше полей блока 18 до тех пор, пока не происходит прерывания. Тогда.на шине 48-появляется сигнал прерывания и проходит через элемент ИЛИ 44, устанавливая в заданное состояние триггер 11 в нулевое состояние - триггеры 7,8 и 10, заставляя таким путем регистр 6 гщресовать поле 19 и регистр 9 - адресовать поле 20. Сигнал прерывания может устанавливать в определенные состояния триггеры 7,8,10,11. В ответ на состояние прерывания появляется сигнал SMK, открывая таким путем элементы И 36-39, так что регистр 2 может принимать содержимое регистров 12 и 15. По окончании условия прерывания появляется сигнал SMK, вызывая, таким путем передачу содержимого регистра 2 к регистрам 12 и 15 и в ответ на сигнал JMP - передачу к регистрам 6 и 9. Работа устройства продолжается до тех пор, пока не появится другой сигнал прерывания. Формула изобрет:ения Устройство для адресации блоков памяти, содержащее регистр адреса, выходной регистр и логические блоки, отличающееся тем, -что/ с целью расширения области применения устройства путем обеспечения возможности адресации независимо от длины адресного слова, оно содержит регистры и группы элементов И, причем выходы первого регистра подключены соответственно к входам регистра адреса и одним входам первого логического блока, другие входы которого соединены с выходами второго и третьего регистров, а выходы - с входами егистра адреса, входы и выходы четвертого и пятого регистров через лементы И первой и второй групп подлючены соответственно к выходам и ходам выходного регистра, одни вхоы элементов И третьей группы соедиены с выходом второго логического лока, другие - с выходами четвертоо и пятого регистров, а выходы элеентов И третьей группы подключены входам второго и третьего регистров, ход второго логического блока и 76761 ;управляющие входы элементов И первой :И второй групп соединены с соответствующими управляющими шинами. Источники информации, принятые во внимание при экспертизе 1.Крайзмер Л,П. Устройства хранения дискретной информации. - Л.г Энергия, 1969, с. 264-267. 2.Патент США №3943225, кл. 340-172.5, 1972. / ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексное устройство для сканирования линий, работающих с различными скоростями передачи | 1973 |

|

SU1093264A3 |

| Устройство для уплотнения каналов связи | 1973 |

|

SU650526A3 |

| Устройство для обмена информацией | 1989 |

|

SU1702378A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1987 |

|

SU1451768A1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Многопроцессорная вычислительная система | 1987 |

|

SU1792540A3 |

| Устройство управления каналами | 1972 |

|

SU545983A1 |

| СЕТЬ ДЛЯ ОБЕСПЕЧЕНИЯ ЧУВСТВИТЕЛЬНОСТИ, ДВУСТОРОННЕЙ СВЯЗИ И УПРАВЛЕНИЯ | 1988 |

|

RU2090926C1 |

| Устройство для сопряжения периферийного устройства с ЭВМ | 1988 |

|

SU1596339A1 |

Авторы

Даты

1979-07-25—Публикация

1973-04-12—Подача