Изобретение относится к технике связи и может использоваться в системах нередачи цифровых сигналов, представляющих отдельные статические характеристики такие, как видеосигналы, например видеозаиись.

Известно устройство для передачи и приема цифровых сигналов связи, содержащее на передающей стороне на входе дифференциальный кодер, один выход которого через последовательно соединенные кодер слов переменной длины и коммутатор подключен к входам блока уплотнения, а другой выход - через генератор синхронизации - к синхронизирующему входу блока уплотнения, выходы которого через блок переменной памяти подключены к управляющему входу коммутатора, а на приемной стороне - блок переменной памяти, выход которого подключен к входам детектора синхронизации и декодера, причем на вход считывания блока переменной памяти на передающей стороне и на входы записи блока переменной памяти на приемной стороне поданы тактовые сигналы передачи, а пилотсигнал с выхода дифференциального кодера подан на соответствхаощий вход кодера слов переменной длины и генератора синхронизации.

Однако в этом устройстве имеются большие искажения сигнала.

Цель изобретения - уменьшение искажений сигнала.

Для этого в устройство для передачи и приема цифровых сигналов связи, содержщее на передающей стороне на входе дифференциальный кодер, один выход которого через последовательно соединенные кодер слов переменной длины и коммутатор подключен к входам блока управления, а другой выход - через генератор синхронизации - к синхронизирующему входу блока уплотнения, выходы которого через блок переменной памяти подключены к управляющему входу коммутато.ра, а на приемной стороне - блок переменной памяти, выход которого подключен к входам детектора синхронизации и декодера, причем на вхо считывания блока переменной памяти на передающей стороне и на входы записи блока переменной памяти на приемной стороне поданы тактовые сигналы передачи, а пилот-сигнал с выхода дифференциального кодера подан на соответствующий вход кодера слов переменной длины и генератора синхронизации, на передающей стороне введен блок сравнения фаз, на входы которого поданы соответственно пплот-сигнал и тактовый сигнал передачи, а выход разност); фаз блока сравнения фаз подключен к дополнительному входу блока уплотнения, а

на приемной стороне введены запирающий блок и последовательно соединенные детектор разности фаз, блок буферной памяти и генератор, выход которого подключен к соответствующему входу блока буферной памяти, на управляющий вход которого подан тактовый сигнал передачи. Кроме того, другой выход детектора разности фаз подключен к дополнительному входу декодера и к одному входу запирающего блока, выход которого подключен к соответствующим входам детектора синхронизации и детектора разности фаз, вход которого соединен с другим входом запирающего блока, причем выход пилот-сигнала генератора подключен к соответствующим входам декодера, блока переменной памяти, детектора синхронизации и детектора разности фаз, к соответствующему входу которого подключен выход блока переменной памяти.

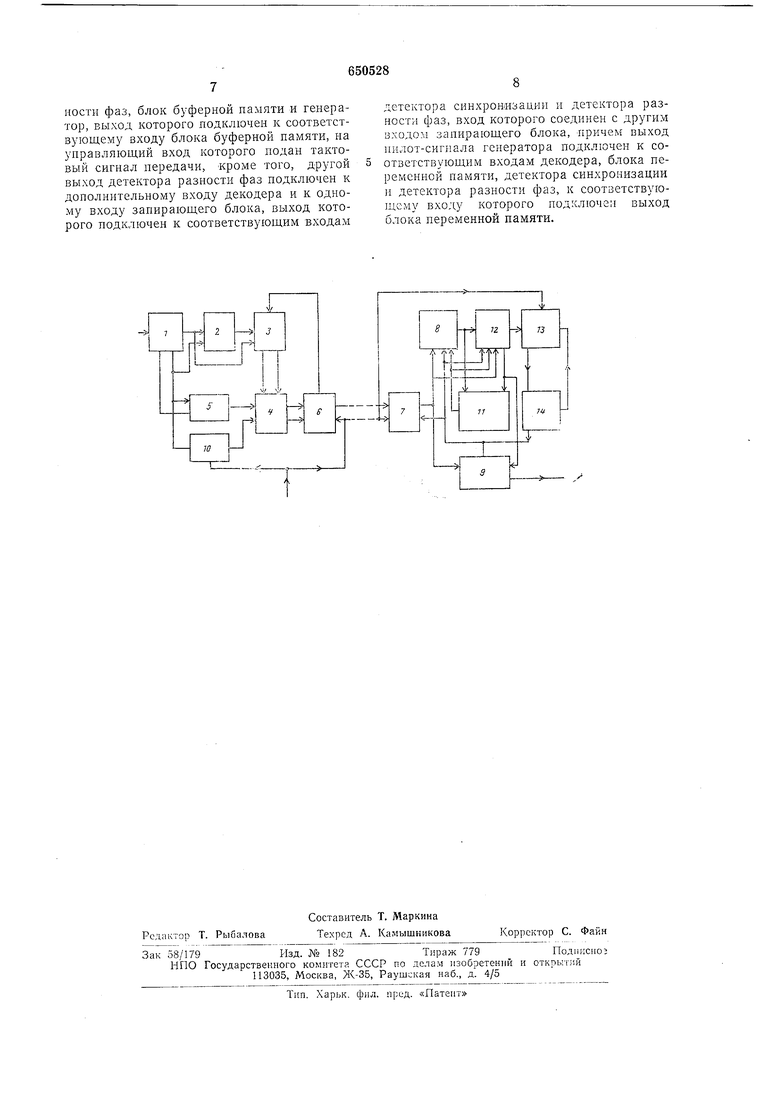

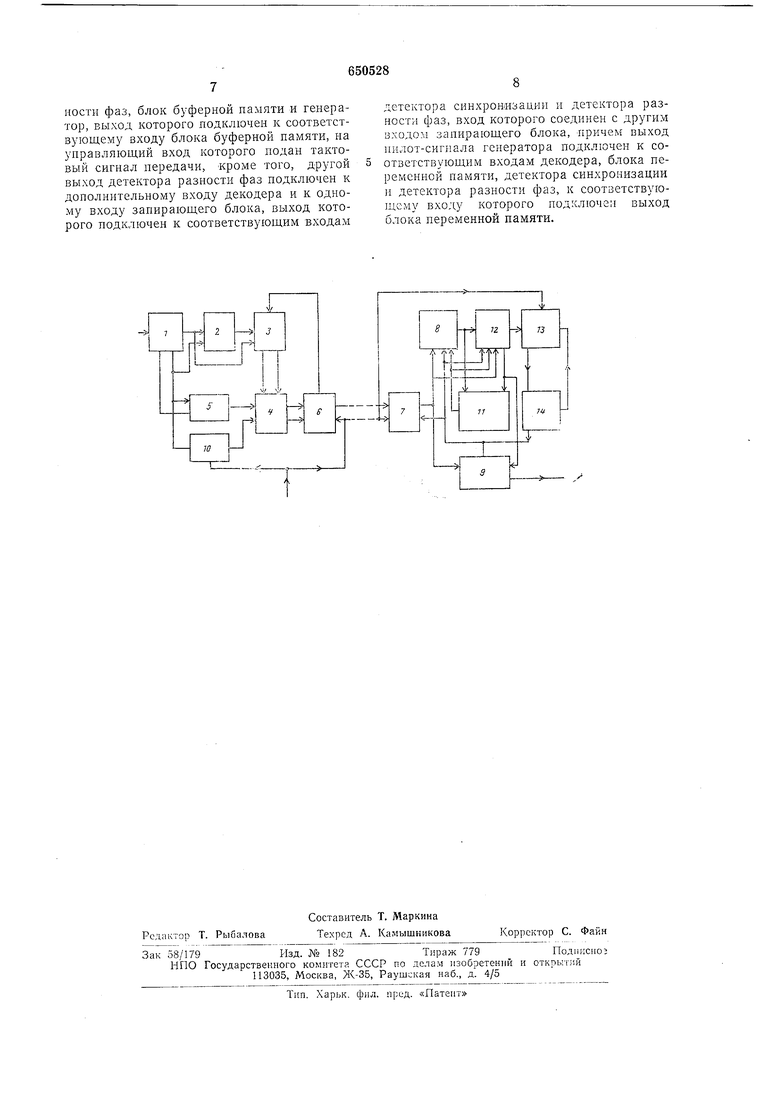

На чертел е изображена структурная электрическая схема предложенного устройства.

Устройство для передачи .и приема цифровых сигналов связи содержит на передающей стороне на входе дифференциальный кодер 1, один выход которого через последовательно соединенные кодер 2 слов переменной длины и коммутатор 3 подключен к входам блока 4 уплотнения, а другой выход через генератор 5 синхронизации - к синхронизирующему входу блока уплотнения, выходы которого через блок 6 переменной памяти подключены к управляющему входу коммутатора 3, а на приемной стороне - блок 7 переменной памяти, выход которого подключен к входам детектора 8 синхронизации и декодера 9, причем на вход считывания блока 6 переменной памяти на передающей стороне и на входы записи блока 7 переменной памяти на приемкой стороне поданы тактовые сигналы передачи, а пилот-сигнал с выхода дифференциального кодера ./ нодан на соответствующий вход кодера 2 слов переменной длины и генератора 5 синхронизации.

Кроме того, на передающей стороне включен блок 10 сравнения фаз, на входы которого поданы соответственно пилот-сигнал и тактовый сигнал передачи, а выход разности фаз блока сравнения фаз подключен к дополнительному входу блока 4 уплотнения. На приемной стороне включены запирающий блок // и последовательно соединенные детектор 12 разности фаз, блок 13 буферной памяти и генератор 14, выход которого подключен к соответствующему входу блока 13 буферной памяти, на управляющий вход которого подан тактовый сигнал передачи. Другой выход детектора 12 разности фаз подключен к дополнительному входу декодера Р и к одному входу запирающего блока 11, выход которого подключен к соответствующим

входам детектора 8 синхронизации и детектора 12 разности фаз, вход которого соединен с другим входом запирающего блока //, причем выход пилот-сигнала генератора 14

подключен к соответствующим входам декодера 9, блока 7 переменной памяти, детектора 8 синхронизации и детектора 12 разности фаз, к соответствующему входу которого подключен выход блока 7 переменпой памяти.

Устройство работает следующим образом.

Сигнал видеозаписи поступает в дифференциальный кодер /, который кодирует

разницу амплитуд двух последовательных образцов и выдает слова из трех бинарных элементов, каждое слово соответствует одной точке изображения в ритме тактового пилот-сигнала, выдающего частоту

2,048 Мгц. Следовательно, дебит декодирующего кодера / равен 3X2,048 6,144 Megabits/s (Mbis).

Кодер 2 преобразует слова из трех бинарных элементов, выдаваемых дифференциальным кодером 1 в слова, содержащие переменное число элементов, а именно от 1 до 8. Длина слова, выдаваемого кодером 2, является функцией вероятности появления слова, выдаваемого дифференциальным кодером 1, наиболее вероятные слова соответствуют наиболее коротким (1 или 2 элемен,та) на выходе кодера 2. При видеосигнале отдельные сигналы имеют неодинаковую вероятность, потому что слабые выбросы,

соответствующие слабым колебаниям яркости, являются более частыми, чем значительные выбросы, соответствующие резким колебаниям. Кодер 2 выдает, например, сигналы 0,01, 011 . . . 01111111 (каждый О,

следовательно, соответствует началу слова). Кодер 2 выдает слова в ритме тактового сигнала, поэтому дебит может иметь от 2,048 Mb/s до 8X2,048 Mbls.

Слова с выхода кодера 2 записываются

в блок 6 переменной памяти при помощи коммутатора 3 и блока 4 уплотнения. Блок 6 переменной памяти вместе с коммутатором 3 позволяет регулировать дебит, который очень нерегулярен на выходе кодера 2.

Коммутатор 3 имеет вход, непосредственно связанный с дифференциальным кодером 1 и может прерывать передачу во время движения строки. Он управляется сигналом, представляющим заполнение переменной

памяти.

Средний числовой дебит на выходе блока 6 переменной памяти составляет порядка двух бинарных элементов в слове. Однако, если память не полностью заполнена,

возможны ощибки при считывании, ком.мутатор 3 передает слова из трех элементов с выхода дефференциального кодера /. Когда блок в переменной памяти переполнен, коммутатор 3 прерывает передачу на строке, этот перерыв вызывает повторение поедыдущей строки. Кроме того, коммутатор 3 подает на блок 4 уплотнения пнформацню, характеризующую отбор, произведенный им. На блок 4 уплотнения поступают также слова синхронизации, выдавае.мые генератором 5 в ритме тактового сигнала. Слово синхронизации образовано псевдослучайБым сигналом из ,15 двоичных элементов и выдается генератором 5 один раз за строку при появлении фронта сигнала синхронизации, содержащего в дополнительном сигнале. Блок 4 уплотнения вставляет информацию вслед за словом синхронизации, выдаваемым генератором 5, которая располагается во время затухания дополнительного сигнала. Умноженный сигнал записывается в блок 6 переменной памяти с дебитом слов, выдаваемых тактовым сигналом, и информация передается с блока 6 переменной памяти (на блок 7 переменной памяти в ритме тактового сигнала передачи, зависяцдего от канала передачи. Так как длина слов изменяется в зависимости от транскодирования, частота передачи независима от частоты пилот-сигнала, и необходимо восстановить частоту пилот-сигнала при приеме для восстановления сигнала и для синхронизации заннси в блок 6 неременной памяти и считывания в блоке 7 переменной памяти. Для этого блок 4 уплотнения получает информацию, характеризующую уход частоты пилот-сигнала по отношению к частоте, связанной с частотой передачи. Эта информация выдается блоком 0 сравнения и вводится в блок 4 уплотнения вслед за информацией отбора, выдаваемой коммутатором 3. При приеме сигнал прочитывается в блоке 7 переменной памяти в ритме частоты пилот-сигнала, восстановленной генератором 14. Затем детектор 8 отыскивает момент синхронизации, детектируя число совпадений между двоичными элементами и словом синхронизации, помещенным в блок 7 переменной памяти. Восстановление частоты пилот-сигнала производится следующим образом. При передаче информация ухода d прочитывается в блоке 7 переменной памяти на собственной частоте Л генератора 14, затем детектируется так же, как и информация отбора, в детекторе 12 после определения слова синхронизации в детекторе 8, который посылает сигнал 5. Информация d записывается в блоке 13 буферной иамяти в ритме частоты FP, выдаваемой генератором 14, которая соответствует частоте строки передачи и прочитывается в ритме k НТ. В зависимости от величины информации ухода d, импульс отсекается на частоте тактового сигнала, помещенной в память. Полученный сигнал воздействует на генератор 14. Определение слова синхронизации производится с помощью запирающего блока 11. Детектор S отыскивает первую группу, содержащую то количество двоичных элементов, что и слово синхронизации. Однако для слов с переменной длиной больше невозможно считать количество тактовых сигналов для определения момента синхронизации и нужно декодировать иринятый сигнал для запирания синхронизации. Отыскивают синхронизацию внутри оцределенного окна при помощи запирающего блока //, который включает временную базу, возвращающуюся на нуль, когда детектор 8 выдает на запирающий блок // сигнал 5, соответствующий детектированию. Окно выбирается как компромисс между узким окном, предохраняющим от отыскания ложной синхронизации, и широким окном, которое предохраняет от потери синхронизации при возможных ошибках в пакете слов. Для уменьшения влияния ошибок передачи допускают колебания плюс-минус четыре слова, ожидаемого положения синхронизации. Декодер-9 выдает двоичные элементы с дебитом трех двоичных элементов в слова, с частотой 2,048 Мгц, слова код 1руются в дифференциальной форме. Введение дополнительных блоков позволяет уменьшить искажение сигналов. Формула изобретен и я Устройство для передачи и приема цифровых сигналов связи, содержащее на передающей стороне на входе дифференциальный кодер, один выход которого через последовательно соединенные кодер слов переменной длины и коммутатор подключен к входам блока уплотнения, а др}той выход - через генератор синхронизации - к синхронизирующему входу блока уплотнения, выходы которого через блок переменной памяти подключены к управляющему входу коммутатора, а на приемной стороне - блок переменной памяти, выход которого подключен к входам детектора синхронизации -и декодера, причем на вход считывания блока переменной памяти на передающей стороне и на входы записи блока переменной памяти «а приемной стороне иоданы тактовые сигналы передачп, а пилотсигнал с выхода дифференциального кодера подан на соответствующий вход кодера слов переменной длины и генератора cniiхронизации, отличающееся тем, что, с целью уменьшения искажений сигнала, на передающей стороне введен блок сравнения фаз, на входы которого поданы соответственно пилот-сигнал п та товый сигнал передачи, а выход разности фаз блока сравнения фаз подключен к дополнительному входу блока уплотнения, а на приемной стороне введены запирающий блок ц последовательно соединенные детектор разности фаз, блок буферной памяти и генератор, выход которого подключен к соответствующему входу блока буферной памяти, на управляющий вход которого подан тактовый сигнал передачи, кроме того, другой выход детектора разности фаз подключен к дополнительному входу декодера и к одному входу запирающего блока, выход которого подключен к соответствующим входам

детектора синхронизации и детектора разности фаз, вход которого соединен с другим входом запирающего блока, причем выход иилот-сигиала генератора подключен к соответствующим входам декодера, блока переменной памяти, детектора синхронизации и детектора разности фаз, к соответствующему входу которого подключен выход блока иеременной памяти.

Авторы

Даты

1979-02-28—Публикация

1976-04-16—Подача