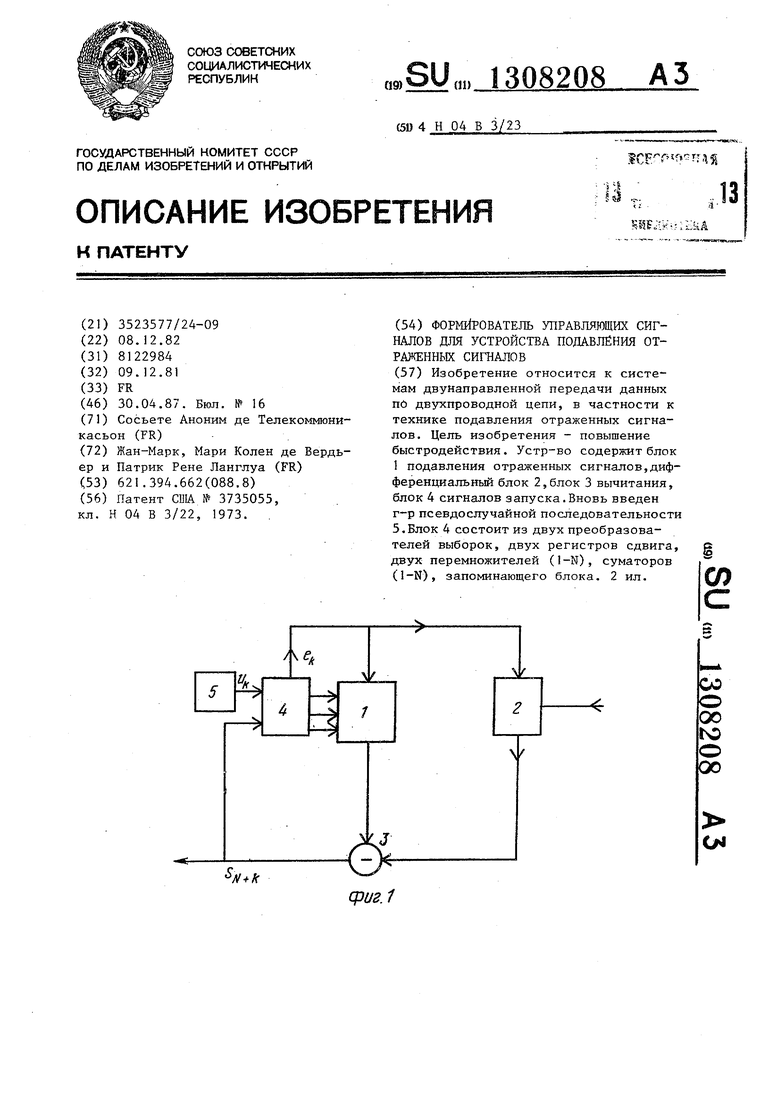

Изобретение относится к системам двунаправленной передачи данных по двухпроводной цепи и, в частности, относится к технике подавления отраженных сигналов.

Целью изобретения является повышение быстродействия.

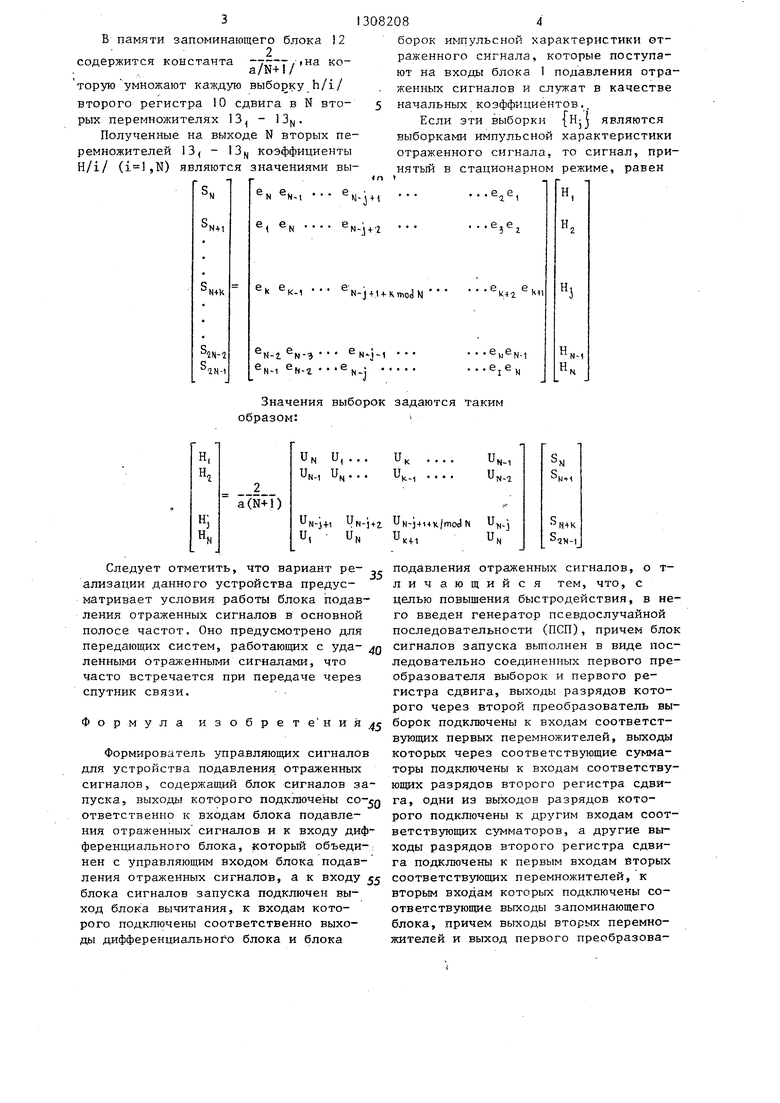

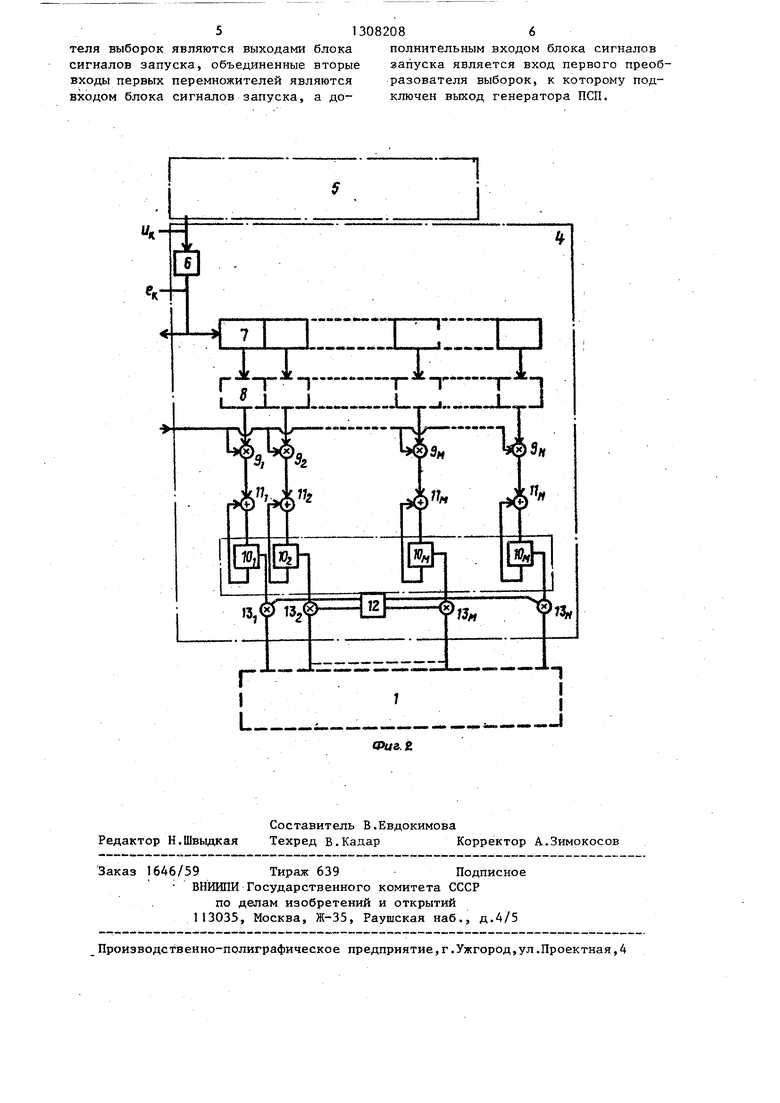

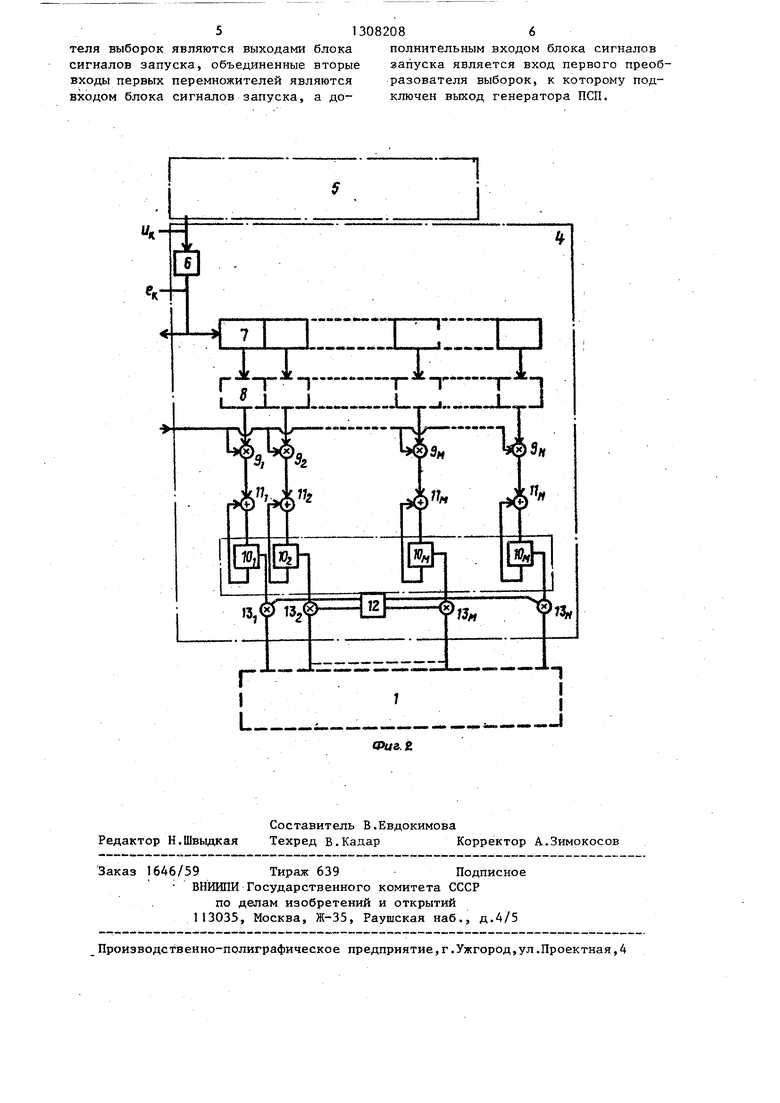

На фиг.1 представлена блок-схема формирователя управляющих сигналов для устройства подавления отраженных сигналов; на фиг.2 - блок сигналов запуска.

. Формирователь управляющих сигналов содержит блок 1 подавления отраженных сигналов, дифференци альный блок 2, блок 3 вычитания, блок 4 сигналов запуска и генератор 5 псевдо- случайной последовательности (ПСП), причем блок 4 сигналов запуска состоит из первого преобразователя 6 выборок, первого регистра 7, сдвига,второго преобразователя 8 выборок,первы перемножителей 9 9 , второго регистра 10 сдвига, сумматоров llj-il,j запоминающий блок 12 и вторые перем- ) ножи т ел и 13, - 13|ii.

Формирователь управляющих сигнало работает следующим образом,

В случа,е, когда блок 1 подавления отраженных сигналов осуществляют обработку в основной полосе частот, обновление коэффициентов согласйо грдиентному алгоритму в момент времени описывается следующим образом:

Cj,/n+i/ C /n/+ ye/n/a/n-k/, где Y - действительная положительная постоянная.

Дифференцирующий блок 2 обеспечивает соединение лийии с модемом при передаче и приеме.

На вход блока 4 сигналов запуска поступает сигнал U последовательности запуска, а также сигнал S, оцениваемого приема.

Генератор ПСП 5 обеспечивает поступление сообщения { Оц сна вход блока 4 сигналов запуска, которое вырабатывает на выходе коэффициенты, не-, посредственно используемые блоком 1 подавления отраженных сигналов в качестве начальных коэффициентов С , причем выборки, образующие последовательность , являются псевдослучайными и их период равен -1)1.

Сообщение первом преобразователе 6 выборок преобразуется в сообщение е, которое образуется из выборок /а, -а/, т.е. каждая выборка

08208 е

ц выводится из выборки Ик с помощью соотношения е a/2U, /. На практике величину а желательно выбирать равной 1.

5 Сообщение е j с одной стороны

передается в линию, а с другой стороны поступает на вход первого регистра 7 сдвига, состоящего из N ячеек, каждая из которых вносит задержку Т.

to В первой ячейке содержится е,, во второй ячейке - еу.. , а в М ячейке - (N-M+K-n) по модулю М и наконец в N ячейке первого регистра 7 сдвига содержится е, . Затем все N выборок

f5 параллельно поступают на-входы второго преобразователя 8 выборок, также содержащего N ячеек, на выходах которых из входных сигналов образуются выборки и.д.. , а именно, на выходе первой ячейки вырабатывается выборка Кц, а на выходе N ячейки - выборка U, .

В общем виде на вход ячейки М поступает выборка .jN а на выходе вырабатывается выборки U(«-M4.k-n)moc) N Полученные Ы выборок UK- U ц+14к-мV к+1 поступают на вход N первых перемножителей 9( -9/, в которых каясдая выборка перемножается- с выборкой S, , принятой с линии передачи с выхода блока 3 вычитания. Поступающие с N пер- вЫх перемножителей 9/ - 9fj N результатов , ,N/ посту35 пают на входы второго регистра 10 сдвига, которые были установлены в нулевое состояние посредством N сум- маторов 11, - 11М Операции перемножения и суммирования осуществляются

40 с момента NT., т.е. по приходу выборки Sfg и в общем виде по приходу выборок, где к меняется от О до N-1.

20

25

30

Применение N сумматоров

11,11

и

0

позволяет накопить в рассматриваемый момент /N+K/T содержимое N второго преобразователя 8. Тогда содержимое второго рег истра 0 сдвига в момент /N+K/T будет выборки , где

Ьк/1/ Ь к,/1/+8м+к или ,.., /1/+3„4к )mociN,

Затем в момент времени /N+K+1/Т содержимое первого регистра 7 стано- 5 вится равным ,, , принятая: выборка равняется .. , тогда выполняется следующее вычисление, поступающее на второй регистр 10 сдвр1га:

Kti NtK4i UtK-j+i jmodN

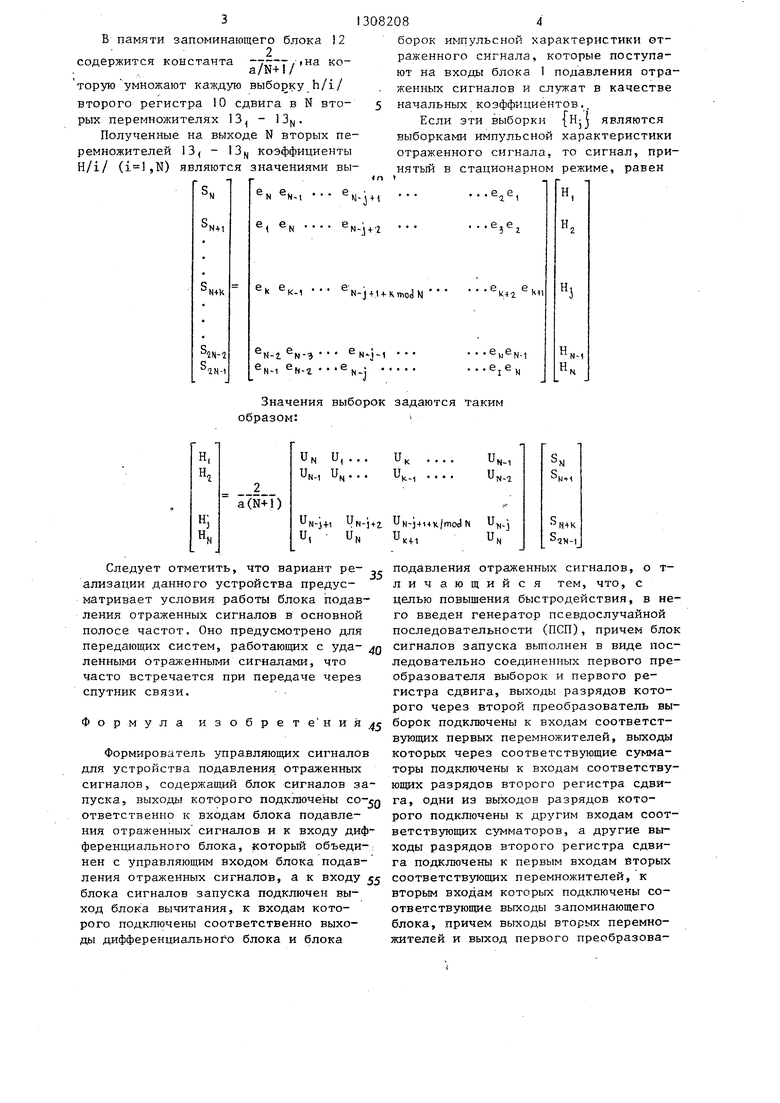

в памяти запоминающего блока 12

2

содержится константа коa/N+l/

торую умножают каждую выборку h/i/ второго регистра 10 сдвига в N вторых перемножителях 13, - 13).

Полученные на выходе N вторых перемножителей 13, - 13| коэффициенты H/i/ (,N) являются значениями вы-N-1

N41

е, е„

N+K

К-1

е

N-1 N-3

h-г

N4

Значения выборок задаются таким образом:

и,.,.

и, ... и.

и,.... и,

К

Un-i+2 UN-J4i4K/mojN U,j

и

кн-1

и

N

Следует отметить, что вариант ре35

ализации данного устройства предусматривает условия работы блока подавления отраженных сигналов в основной полосе частот. Оно предусмотрено для передающих систем, работающих с уда- д ленными отраженными сигналами, что часто встречается при передаче через спутник связи.

Формула изобрете ния

Формирователь управляющих сигналов для устройства подавления отраженных сигналов, содержащий блок сигналов запуска, выходы которого подключены со-гп ответственно к входам блока подавления отраженных сигналов и к входу дифференциального блока, который объеди-; нен с управляющим входом блока подавления отраженных сигналов, а к входу 55 блока сигналов запуска подключен выход блока вычитания, к входам которого подключены соответственно выходы дифференциального блока и блока

082084

борок импульсной характеристики отраженного сигнала, которые поступают на входы блока 1 подавления отраженных сигналов и служат в качестве 5 начальных коэффициентов..

Если эти выборки (HJ являются выборками импульсной характеристики отраженного сигнала, то сигнал, принятый в стационарном режиме, равен

-Г

.,

Н.

-N-j4;2

...е,е

N-J4.H-KmoJN

Ktl

HI

....

Н.

N-t

N-1 N-1

SNI-A

U,j

и

N

N + K

аи-1

подавления отраженных сигналов, о т- личающийся тем, что, с целью повышения быстродействия, в него введен генератор псевдослучайной последовательности (ПСП), причем блок сигналов запуска выполнен в виде последовательно соединенных первого преобразователя выборок и первого регистра сдвига, выходы разрядов которого через второй преобразователь выборок подключены к входам соответствующих первых перемножителей, выходы которых через соответствующие сумматоры подключены к входам соответствующих разрядов второго регистра сдвига, одни из выходов разрядов которого подключены к другим входам соответствующих сумматоров, а другие выходы разрядов второго регистра сдвига подключены к первым входам вторых соответствующих перемножителей, к вторым входам которых подключены соответствующие выходы запоминающего блока, причем выходы вторых перемножителей и выход первого преобразователя выборок являются выходами блока сигналов запуска, объединенные вторые входы первых перемножителей являются входом блока сигналов запуска, а дополнительным входом блока сигналов запуска является вход первого преобразователя выборок, к которому подключен выход генератора ПСП.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема кодированного сигнала изображения | 1976 |

|

SU784816A3 |

| ПРИЕМНИК СЛОЖНЫХ ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ С ПОДАВЛЕНИЕМ УЗКОПОЛОСНЫХ ПОМЕХ | 2003 |

|

RU2249913C1 |

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1983 |

|

SU1840276A1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

| Цифровой приемник многочастотных сигналов в системах с импульсно-кодовой модуляцией | 1982 |

|

SU1233821A3 |

| Устройство формирования и обработки широкополосных сигналов | 2018 |

|

RU2691733C1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Устройство поиска псевдослучайных последовательностей | 1981 |

|

SU1042199A1 |

| Устройство для корреляционного приема фазоманипулированных псевдослучайных сигналов | 1986 |

|

SU1317683A1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНЫХ СИГНАЛОВ | 1985 |

|

SU1840044A1 |

Изобретение относится к системам двунаправленной передачи данных пи двухпроводной цепи, в частности к технике подавления отраженных сигналов. Цель изобретения - повышение быстродействия. Устр-во содержит блок 1 подавления отраженных сигналов,диф- ференциальньш блок 2, блок 3 вычитания, блок 4 сигналов запуска.Вновь введен г-р псевдослучайной последовательности 5.Блок 4 состоит из двух преобразователей выборок, двух регистров сдвига, двух перемножителей (1-N), суматоров

Редактор Н.Швыдкая

Составитель В.Евдокимова

Техред В.Кадар Корректор А.Зимокосов

Заказ 1646/59 Тираж 639Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.А/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

| Патент CUIA № 3735055, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-04-30—Публикация

1982-12-08—Подача