(54) ФАЗОВЫЙ ДИСКРИМИНАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазовый дискриминатор | 1976 |

|

SU799103A1 |

| Фазовый дискриминатор | 1982 |

|

SU1070684A1 |

| Фазовый дискриминатор | 1988 |

|

SU1598109A1 |

| Фазовый дискриминатор | 1983 |

|

SU1450074A1 |

| Устройство для формирования импульсных сигналов | 1990 |

|

SU1800599A1 |

| Фазовый дискиминатор | 1974 |

|

SU497708A1 |

| УСТРОЙСТВО УСКОРЕННОЙ СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2011 |

|

RU2446560C1 |

| Устройство для автоматического выбора квадранта и фазирования сигнала | 1976 |

|

SU670905A1 |

| Фотоэлектрический преобразователь угол-код | 1984 |

|

SU1197081A1 |

| Устройство дискретной автоподстройки фазы тактовых импульсов | 1986 |

|

SU1389005A2 |

1

Изобретение относится к импульсной технике и может быть использовано в системах, предназначенных для синхронизации с дискретным управлением.

Известен фазовый дискриминатор, содержащий первый элемент И, один из входов которого соединен с входом линии задержки и является опор ым входом фазового дискриминатора, 4 другой - с выходом первого инвертора, второй и третий элементы И, первые входы которых соединены с входом второго инвертора и являются сигнальным входом фазового дискриминатора, третий инвертор, выход которого соединен с вторым входом третьего элемента И, и триггер, к одному из входов которого подключен выход второго элемента И, а к прямому выходу - первый вход четвертого элемента Ц, выход которого является выходом сигнала опережения 1.

Однако известный фазовый дискриминатор очень чувствителен к -изменениям частотыопорного сигнала.

Целью изобретения является снижение чувствительности к изменениям частоты опорного сигнала.

Для этого в фазовый дискриминатор, содержащий первый элемент Ц, один из входов которого соединен с входЪм линии задержки и является опорным входом фазового дискриминатораf а другой - с выходом первого инвертора, второй и третий элементы И, первые входы которых соединены с входом второго инвертора и ; являются

0 сигнальным входом фазового дискриминатора, третий инвертор, выход которого соединен с вторым входом третьего элемента И, триггер, к одному из входов которого подключен выход втоSрого элемента И, а к прямому выходу первый вход четвертого элемента И, выход которого является выходом сигнала опережения, введены пятый и шестой элементы И и второй триггер,

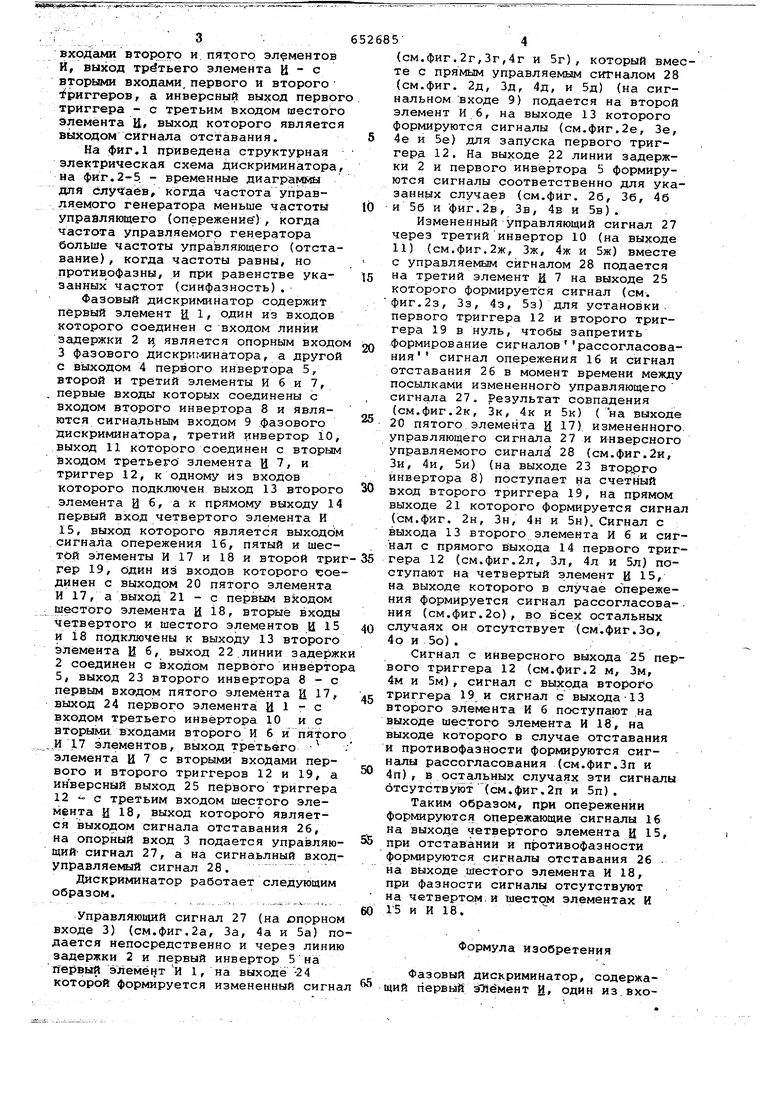

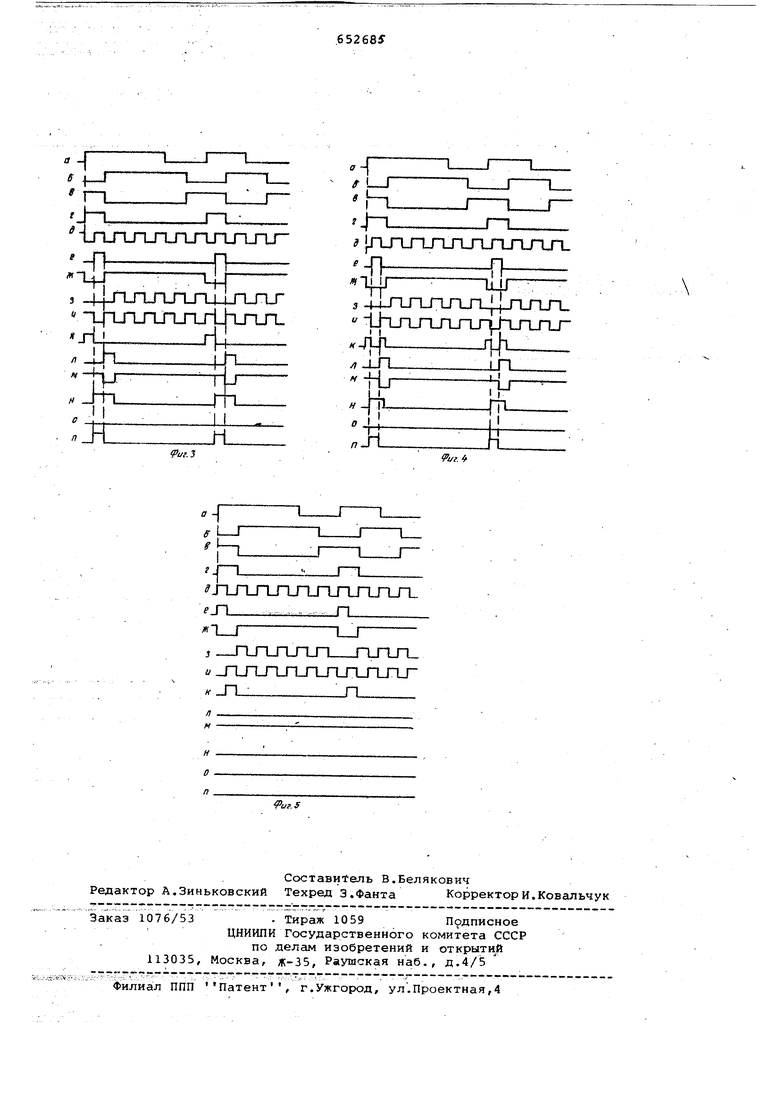

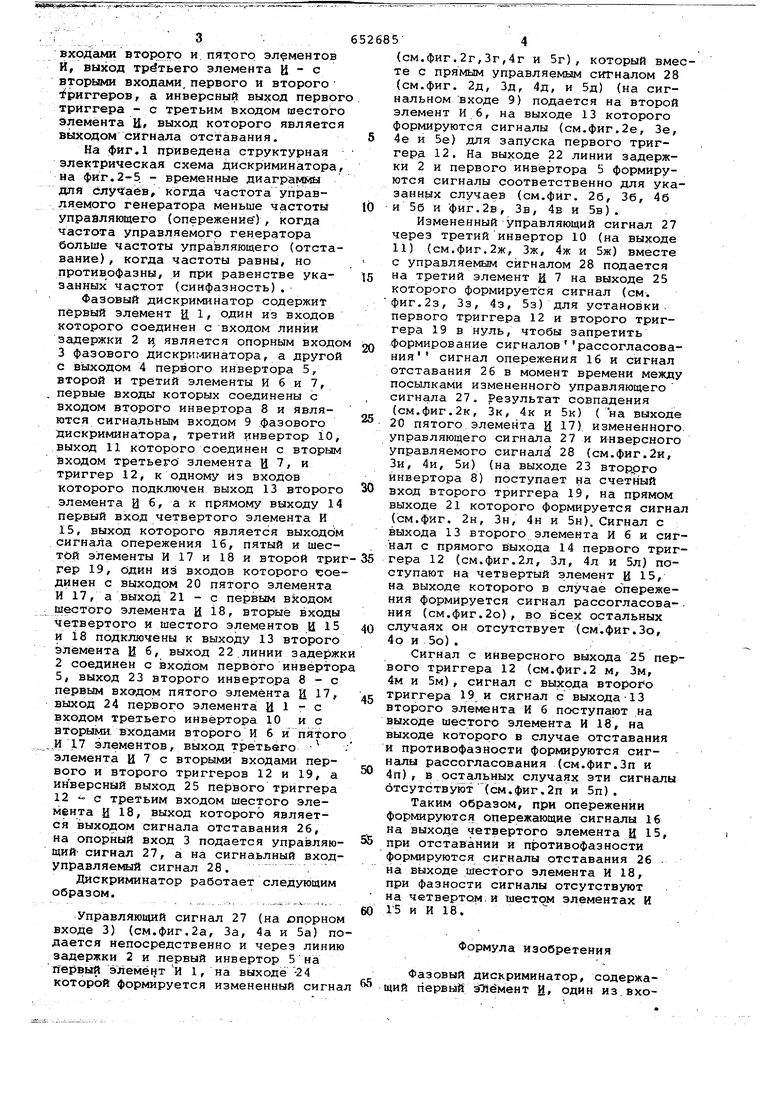

0 один из входов которого соединен с выходом пятого элемента Ц, а выхоД с первым входом шестого элемента Ц, вторые входы четвертого и шестого элементов Д подключены к выходу второго элемента- И, выход линии задержки соединен с входом первого инвертора, выход второго инвертора - с первым входом пятого элемента И выход первого элемента И - с вхо8дом третьего инвертора и с вторьоЛн входами второго и пятого элементов И, выход третьего элемента Ц - с вторьали входами, первого и второго о риггеров, а инверсный выход первого триггера - с третьим входом шестого Элемента И выход которого является выходом сигнала отставания. На фиг.1 приведена структурная электрическая схема дискриминатора, на фиг.2-5 - временные диагракош для , когда частота управляемого генератора меньше частоту управляющего (опережение) , когда частота управляемого генератора больше частоты управляющего (отставание) , когда частоты равны, но противофазны, и при равенстве указанных частот (синфазность). Фазовый дискриминатор содержит первый элемент I, один из входов которого соединен с входом линии задержки 2 ii является опорным входом 3 фазового дискриг-етнатора, а другой с выходом 4 первого инвертора 5, второй и третий элементы И б и 7, первые входы которых соединены с входом второго инвертора 8 и являются сигнальным входом 9 .фазового дискриминатора, третий инвертор 10, выход 11 которого соединен с вторым входом третьего элемента И 7, и триггер 12, к одному из входов которого подключен выход 13 второго элемента и б, а к прямому выходу 14 первый вход четвертого элемента И 15, выход которого является выходом сигнала опережения 16, пятый и шестой элементы И 17 и 18 и второй триг гер 19, один из входов которого «сое динен с выходом 20 пятого элемента И 17, а выход 21 - с первым входом шестого элемента И 18, вторые входы четвертого и шестого элементов И 15 и is подключены к выходу 13 второго элемента И б, выход 22.линии задержк 2 соединен с входом первого инвертор 5, выход 23 второго инвертора 8 - с первым вхсудом пятого элемента И 17, выход 24 первого элемента И 1 с входом третьего инвертора 10 и с вторыми входами второго И б и пя:того ..И 17 элементов, выход третьего элемента И 7 с вторыми входами первого и второго триггеров 12 и 19, а инверсный выход 25 первого триггера 12 с третьим входом шестого элемента И 18, выход которого является выходом сигнала отставания 26, на опорный вход 3 подается управляющий- сигнал 27, а на сигнаьлный входуправляемый сигнал 28. . Дискриминатор работает следующим образом. Управляющий сигнал 27 (на опорном входе 3) (см.Фиг.2а, За, 4а и 5а) п дается непосредственно и через линию задержки 2 и первый инвертор 5на первый элемент И 1, на выходе -24 которой формируется измененный сигн

652685 (см.фиг.2г,3г,4г и 5г), который вместе с прямым управляемым сигналом 28 (см.фиг. 2д, Зд, 4д, и 5д) (на сигнальном входе 9) подается на второй элемент И 6, на выходе 13 которого формируются сигналы (см.фиг.2е, Зе, 4е и 5е) для запуска первого триггера 12. На выходе 22 линии задержки 2 и первого инвертора 5 формируются сигналы соответственно для указанных случаев (см.фиг. 26, Зб, 46 и 5б и фиг.2в, Зв, 4в и 5в) . Измененный управляющий сигнал 27 через третий инвертор 10 (на выходе 11) (см.фиг.2ж, Зж, 4ж и 5ж) вместе с управляемым сигналом 28 подается на третий элемент И 7 на выходе 25 которого формируется сигнал (см. фиг.2з, Зз, 4з, 5з) для установки, первого триггера 12 и второго триггера 19 в нуль, чтобы запретить формирование сигналоврассогласования сигнал опережения 16 и сигнал отставания 26 в момент времени между посылками измененного управляющего сигнала 27. результат совпадения (см.фиг.2к, Зк, 4к и 5к) ( на выходе 20 пятого элемента И 17) измененного, управляющего сигнала 27 и инверсного управляемого сигнал 28 (см.фиг.Зи, Зи, 4и, 5и) (на выходе 23 вторрго инвертора 8) поступает на счетный вход второго триггера 19, на прямом выходе 21 которого формируется сигнал (см.фиг. 2н, Зн, 4н и 5н), Сигнал с выхода 13 второго элемента И 6 и сигнал с прямого выхода 14 первого триггера 12 (см.фиг.2л, 3л, 4л и 5л) поступают на четвертый элемент и 15, на выходе которого в случае оЪережения формируется сигнал рассогласова-. ния (см.фиг.2о), во всех остальных случаях он отсутствует (см.фиг.Зо, 4о и 5о).. Сигнал с инверсного выхода 25 первого триггера 12 (см.фиг.2 м, 3м, 4м и 5м), сигнал с выхода второго триггера 19. и сигнал с выхода-13 второго элемента И б поступают на выходе шестого элемента И 18, на выходе которого в случае отставания и противофаэности формируются сигналы рассогласования (см.фиг.Зп и 4п), в остальных случаях эти сигналы отсутствуют (см.фиг,2п и 5п). Таким образом, при опережении формируются опережающие сигналы 16 на выходе четвертого элемента и 15, при отставании и противофазности формируются сигналы отставания 26 . на выходе шестого элемента И 18, при фазнрсти сигналы отсутствуют на четвертом.и шестом элементах И 15 и И 18. Формула изобретения Фазовый дискриминатор, содержащий первый эТ1ёМент И, один из.вхоДОВ которого соединен с входом линии задержки и является опорным входом дискриминатора, а другой - с выходом первого инвертора, второй и третий элементы И, первые входы которых соединены с входом второго инвертора и являются сигнальным входом фазового дискриминатора, тре тий инвертор, выход которого соединен с вторим входом третьего элемен та И, и триггер, к одному из входов которого подключен выход второг элемента И, а к прямому выходу первый вход четвертого элемента и, выход которого является выходом сигнала опережения, отличающий с я тем, что, с целью снижения Чувствительности к изменениям частоты опорного сигнала, в него введены пятый и шестой элементы и и второй триггер, один из входов которого соединен с выходом

-г

rf OCfcr jj { 6 , ПЯТОГО элемента И, а выход - с первйм входом шестого элемента Н вторые входы четвертого и шестого элементов И подключены к выходу второго элемента И, выход линии задержки соединен с входом первого инвертора, выход второго инвертора - с первым входом пятого элемента И, выход первого, элемента И - с входом третьего инвертора и с вторыми входами второго и пятого элементов И, выход третьего элемента И - с вторыми входами первого и второго триггеров, а инверсный выход первого триггера - с третьим входом шестого элемента Jif выход которого является выходом сигнала отставания. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 497708, кл. Н 03D 13/00, 07.06.74.

а .

-TLf fljT

т 1-LjI l|

3 -JjiJTJTJTjnji4ii-n rLr

« J |friJl njnjljHiriJ-LrL / П1.. rjl

.An:

4b-

JL

- t

ЪтJгrulJnJ LrLГLnJ

u

v-f

,

3 4Jj4JTJlJTJT4aJTJ Lr nJlJlJlJTJT riJlJ LrL

j-ijH

IrLnjnjnJTJTrLrLrLTL

-П..TMT

,

- . -- - I 7 ™

TJTjnj- J-LrLTLr

TIJL

n

if

ii

3 (,

.. . . П

j

njTJTXUTJl n rLrLr

V ПП

Авторы

Даты

1979-03-15—Публикация

1976-09-29—Подача