(54) ФАЗОВЫЙ ДИСКРИМИНАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазовый дискриминатор | 1976 |

|

SU652685A1 |

| Фазовый дискриминатор | 1982 |

|

SU1070684A1 |

| Фазовый дискриминатор | 1983 |

|

SU1450074A1 |

| Фазовый дискриминатор | 1988 |

|

SU1598109A1 |

| Устройство для приема сигналов | 1982 |

|

SU1100744A1 |

| Система цикловой синхронизации для многоканальных систем связи | 1988 |

|

SU1598193A1 |

| Устройство формирования синхронизирующих последовательностей | 1982 |

|

SU1166331A1 |

| Фазовый дискиминатор | 1974 |

|

SU497708A1 |

| Цифровое устройство для управления инвертором | 1983 |

|

SU1127067A1 |

| Адаптивный регенератор | 1986 |

|

SU1363490A1 |

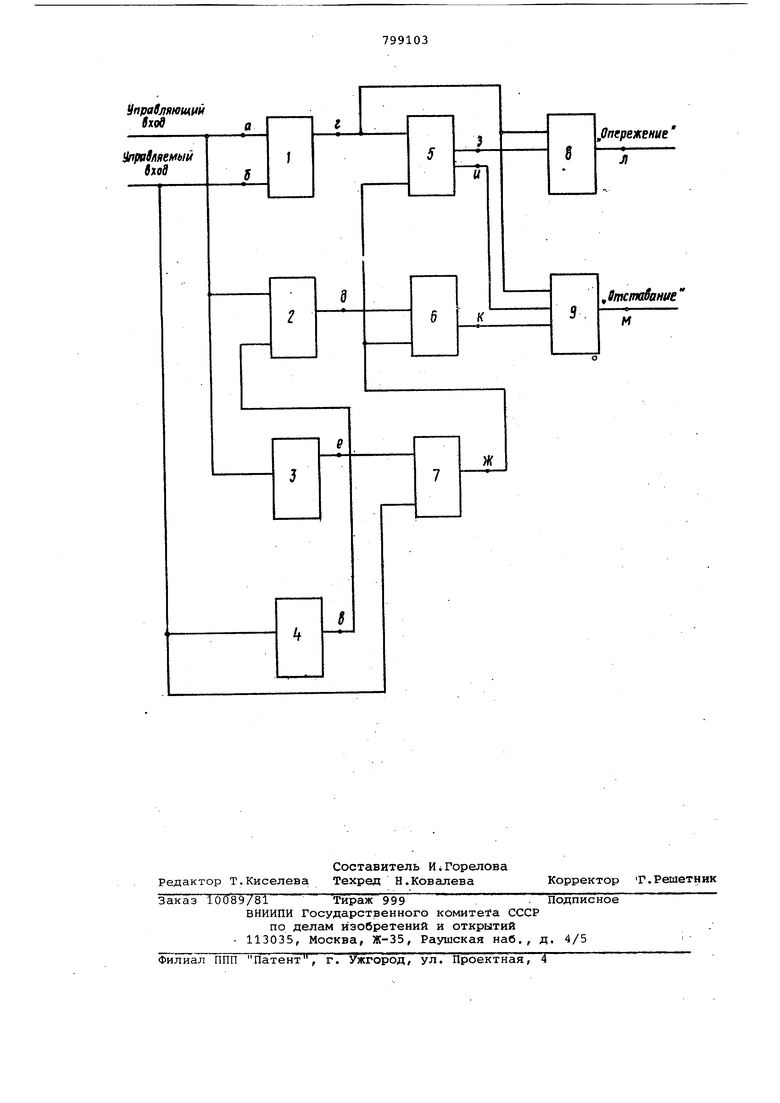

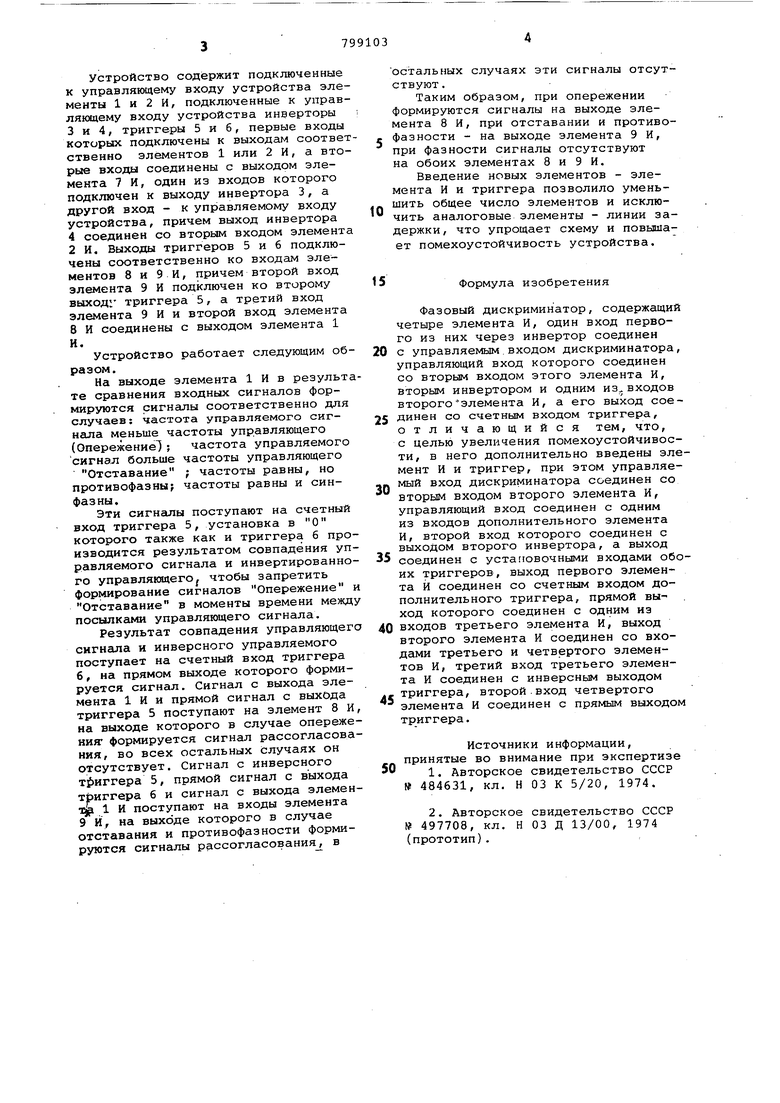

Изобретение относится к автомати ке и радиоэлектронике, в частности к области передачи данных, и предназначено для работы в системах син ронизации с дискретным управлением частотой управляемого генератора. Известны фазовые дискриминаторы с прямоугольной характеристикой; выполненные на бистабиЛьных и логических элементах 1 . Однако такие элементы не обладают достаточным быстродействием. Наиболее близким к предлагаемому по технической сущности является фа зовый дискриминатор, состоящий из эд1ементов И, элементов ИЛИ, линий задержек и триггера. При этом на двух элементах И производится сравнение входных сигналов, а с помощью управляющего триггера на двух других элементах И производится выделе ние сигналов рассогласования опере жение и отставание f2j . Недостаток данного устройства низкая помехоустойчивость вследстви налйадя-линий задержек. Цель изобретения - увеличение по мехоустойчивости . Цель достигается тем, что в фазо вый дискриминатор, содержащий четыр элемента И, один вход первого из них через инвертор соединен с управляемым входом дискриминатора, управляющий вход которого соединен со вторым входом этого элемента И, вторым инвертором и одним из входов -второго элемента И, а его выход соединен со счетным входом триггера, дополнительно введены элемент И и триггер, при этом управляемый вход дискриминатора соединен со вторым входом второго элемента И, управляющий вход соединен с одним из входов дополнительного элемента И, второй вход которого соединен с выходом второго инвертора, а выход соединен с установочными входами обоих триггеров, выход первого элемента И соединен со счетным входом дополнительного триггера, прямой выход которого соединен с одним из входов третьего элемента И, выход второго элемента И соединен со входами третьего и четвертого элементов И, третий вход третьего элемента И соединен с инверсным выходом триггера, второй вход четвертого элемента И соединен с прямым выходом триггера. На чертеже приведена функциональная блок-схема фазового дискриминатора.

Устройство содержит подключенные к управляющему входу устройства элементы 1 и 2 И, подключенные к управляющему входу устройства инверторы

3и 4, триггеры 5 и 6, первые входы которых подключены к выходам соответственно элементов 1 или 2 И, а вторые входы соединены с выходом элемента 7 И, один из входов которого подключен к выходу инвертора 3, а другой вход - к управляемому входу устройства, причем выход инвертора

4соединен со вторым входом элемента 2 И. Выходы триггеров 5 и б подключены соответственно ко входам элементов 8 и 9 И, причем второй вход элемента 9 И подключен ко второму выходу триггера 5, а третий вход элемента 9 И и второй вход элемента

8И соединены с выходом элемента 1 И.

Устройство работает следующим образом.

На выходе элемента 1 И в результате сравнения входных сигналов формируются сигналы соответственно для случаев: частота управляемого сигнала меньше частоты управляющего (Опережение ; частота управляемого сигнал больше частоты управляющего

Отставание ; частоты равны, но противофазны частоты равны и синфазны.

Эти сигнсшы поступают на счетный вход триггера 5, установка в О которого также как и триггера б производится результатом совпадения управляемого сигнала и инвертированного управлякядего чтобы запретить формирование сигналов Опережение и Отставание в моменты времени между посылками управляющего сигнала.

Результат совпадения управляющего сигнала и инверсного управляемого поступает на счетный вход триггера 6, на прямом выходе которого формируется сигнал. Сигнал с выхода элемента 1 И и прямой сигнал с выхода триггера 5 поступают на элемент 8 И на выходе которого в случае опережения формируется сигнал рассогласования, во всех остальных случаях он отсутствует. Сигнал с инверсного триггера 5, прямой сигнал с выхода триггера б и сигнал с выхода элеменф 1 И поступают на входы элемента

9И, на выходе которого в случае отставания и противофазности формируются сигналы рассогласования, в

остальных случаях эти сигналы отсутствуют.

Таким образом, при опережении формируются сигналы на выходе элемента 8 И, при отставании и противофазности - на выходе элемента 9 И, при фазности сигналы отсутствуют на обоих элементах 8 и 9 И.

Введение новых элементов - элемента И и триггера позволило уменьшить общее число элементов и исключить аналоговые элементы - линии задержки , что упрощает схему и повышает помехоустойчивость устройства.

Формула изобретения

Фазовый дискриминатор, содержащий четыре элемента И, один вход первого из них через инвертор соединен

0 с управляемым входом дискриминатора, управляющий вход которого соединен со вторым входом этого элемента И, вторым инвертором и одним из, входов второго элемента И, а его выход соединен со счетным входом триггера, отличающийся тем, что, с целью увеличения помехоустойчивости, в него дополнительно введены элемент И и триггер, при этом управляеQ мый вход дискриминатора соединен со вторым входом второго элемента И, управляющий вход соединен с одним из входов дополнительного элемента И, второй вход которого соединен с выходом второго инвертора, а выход

5 соединен с установочными входами обоих триггеров, выход первого элемента И соединен со счетным входом дополнительного триггера, прямой выход которого соединен с одним из

0 входов третьего элемента И, выход второго элемента И соединен со входами третьего и четвертого элементов И, третий вход третьего элемента И соединен с инверсным выходом триггера, второй.вход четвертого элемента И соединен с прямым выходом триггера.

Источники информации, принятые во внимание при экспертизе

УпраИляюмий бходд

Иправляемый бход

JSnepexenue

Отстаивание

Авторы

Даты

1981-01-23—Публикация

1976-07-06—Подача