соответственно с четными и нечетными выходами дешифратора младших разрядов входного кода; Выходы первого и второго элементов ИЛИ являются вторым и третьим выходами блока преобразования младших разрядов входного кода. Входы -го (i-1 4 П/2) элемента ИЛИ группы соединены с (25 -1)-ым и выходами дешиф-г ратора младших разрядов входного кода, а выходы группы элементов ИЛИ являются выходами блока преобразования младших .разрядов входного кода.

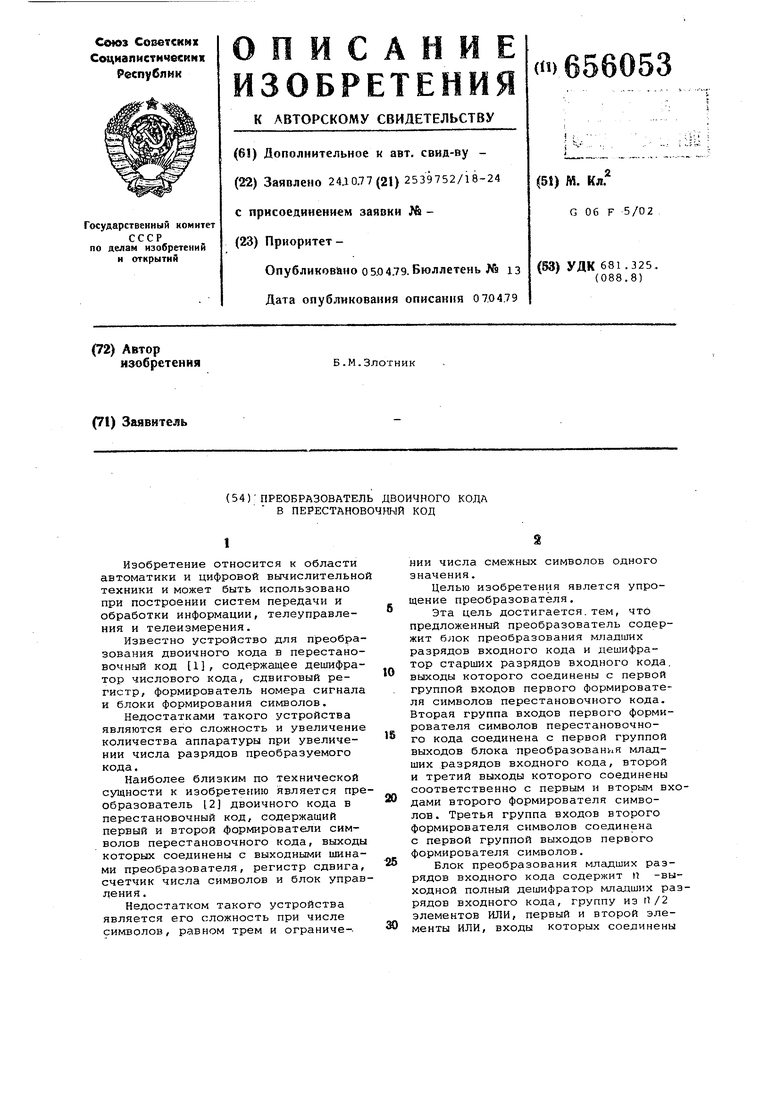

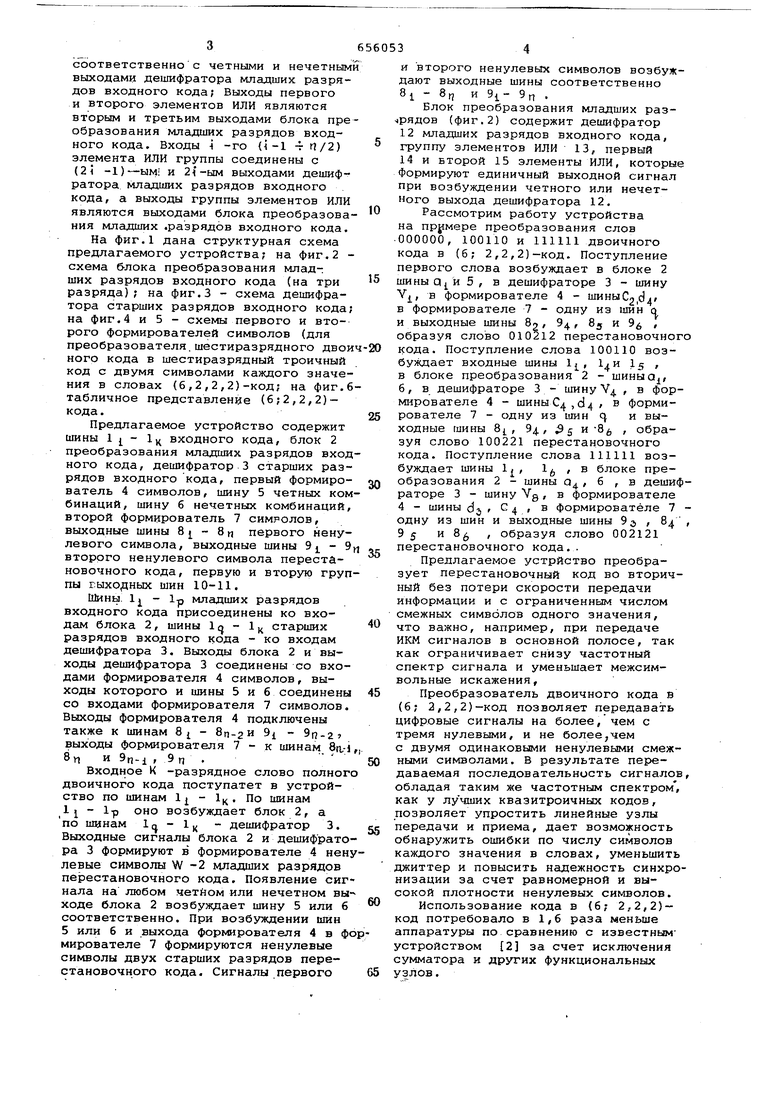

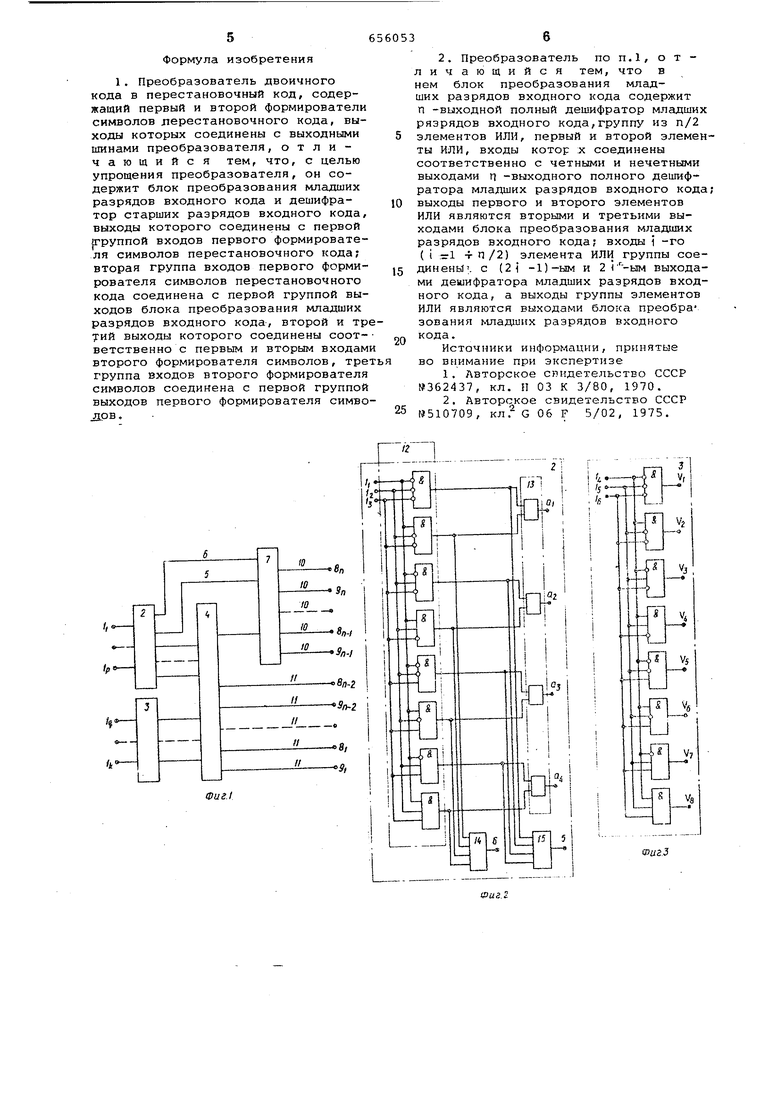

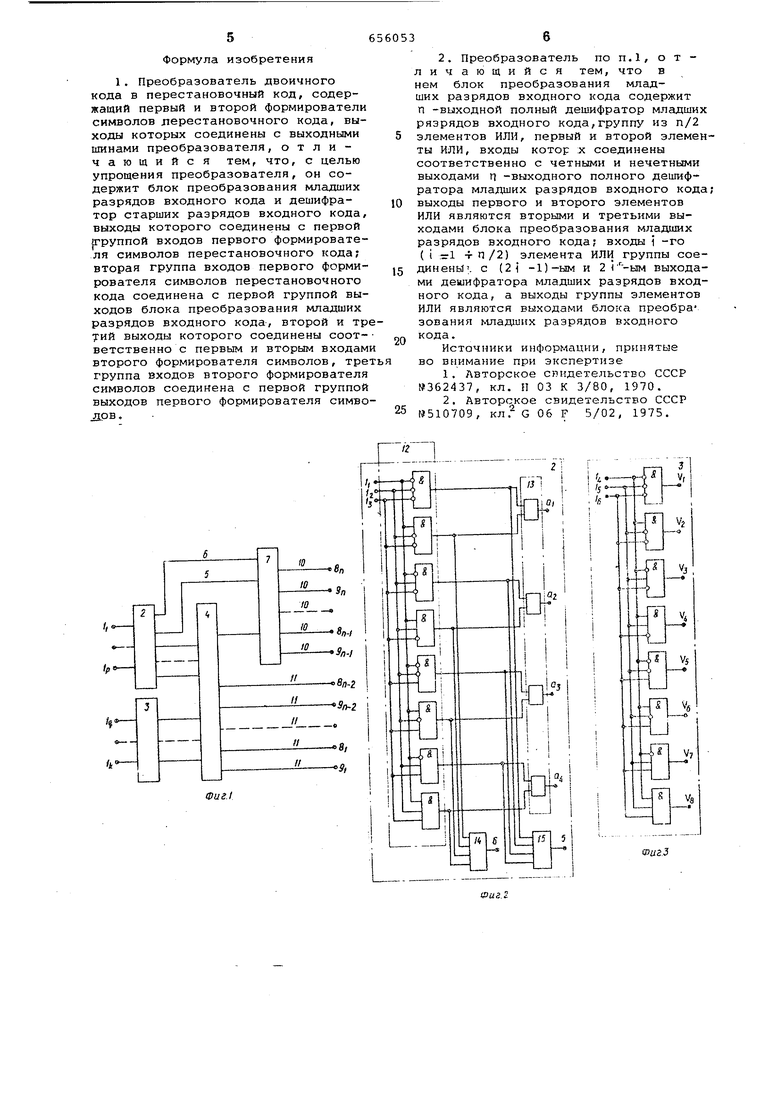

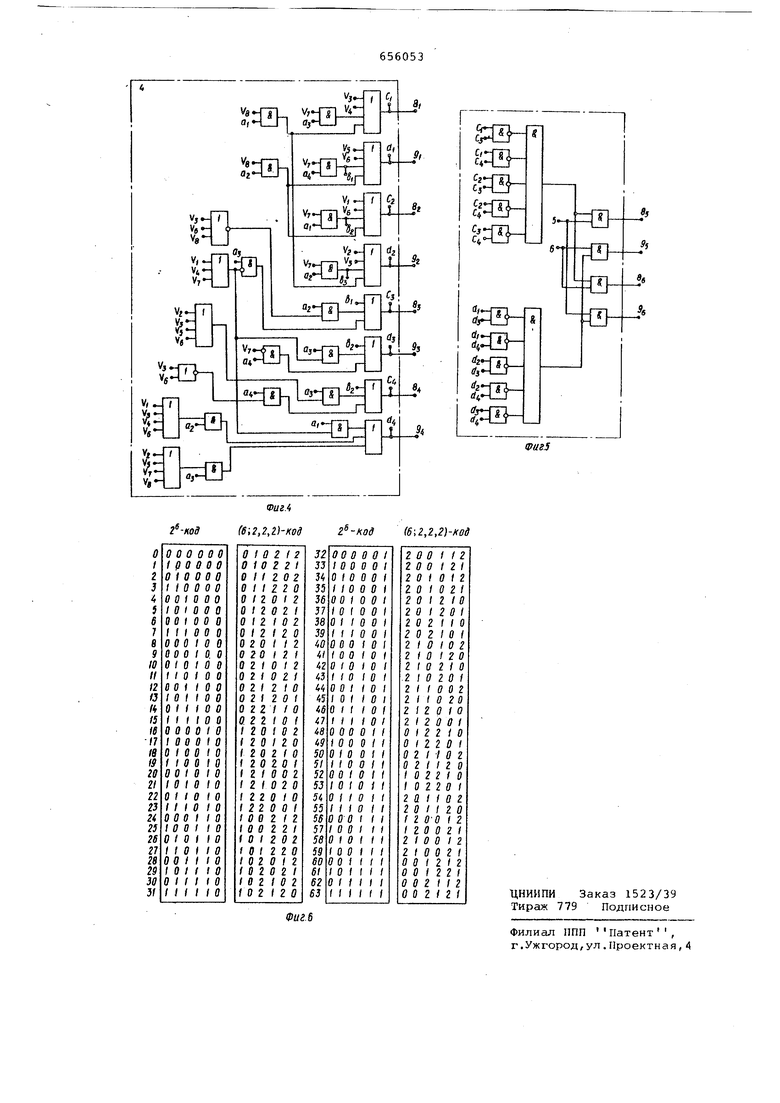

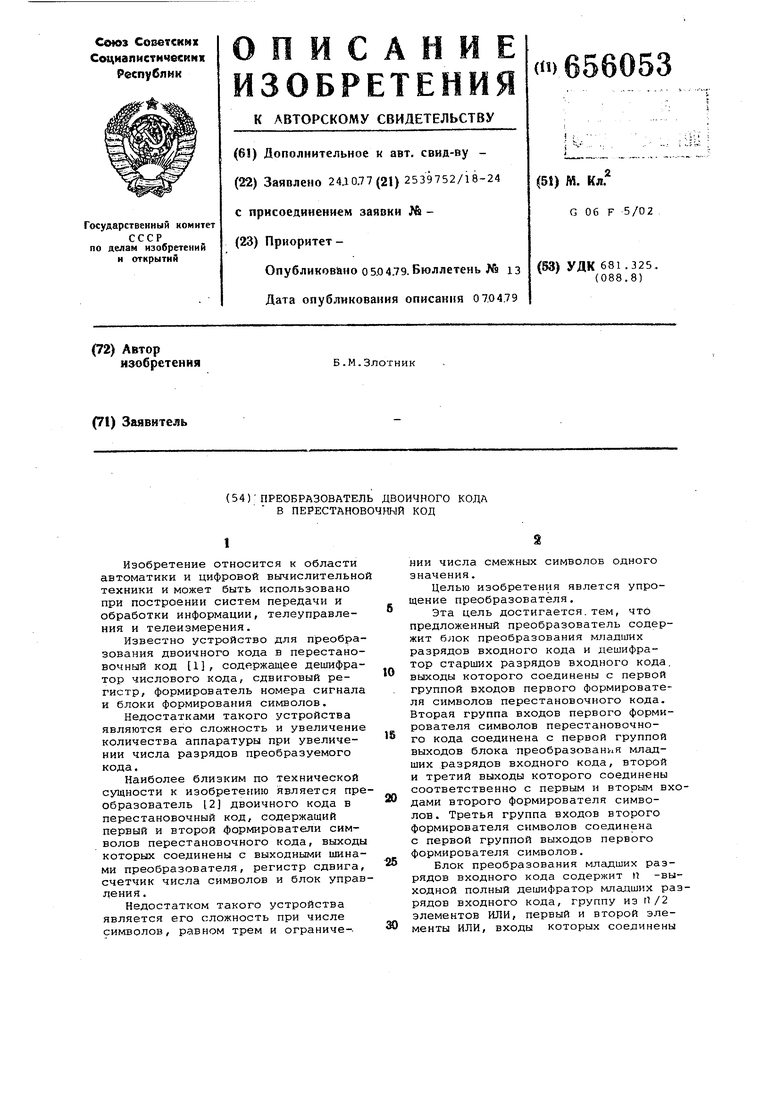

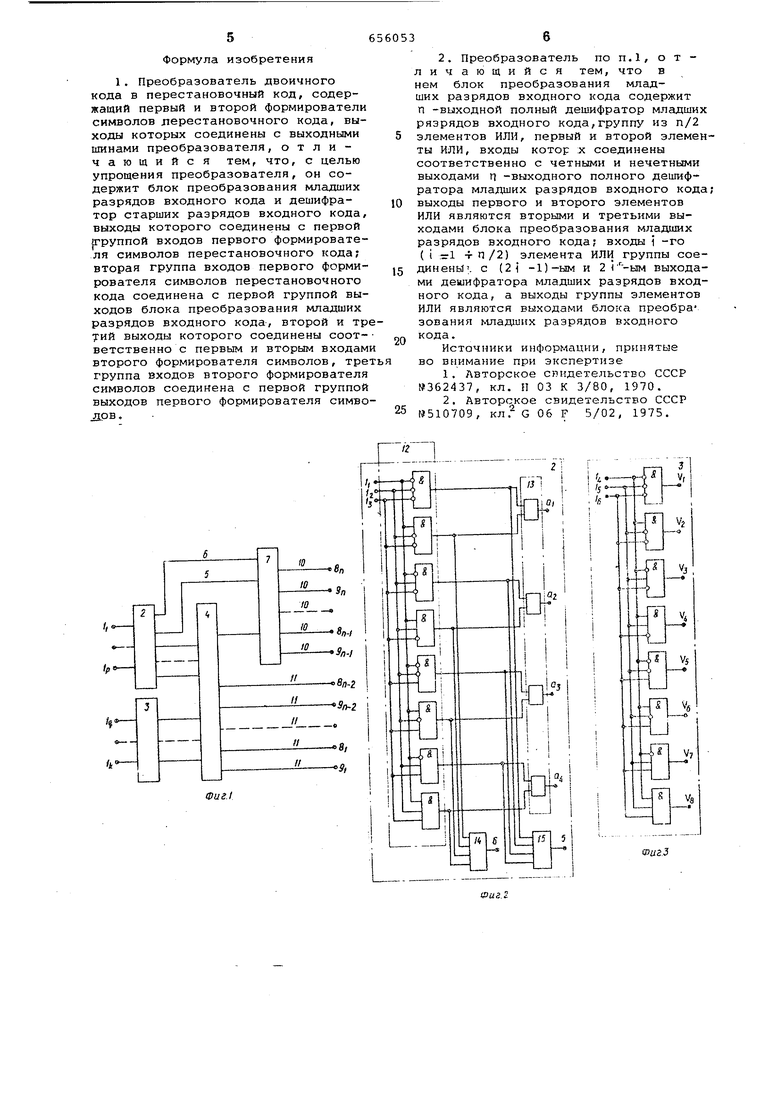

На фиг.1 дана структурная схема предлагаемого устройства; на фиг.2 схема б-лока преобразования младших разрядов входного кода (на три разряда); на фиг.З - схема дешифратора старших разрядов входного кода; на фиг.4 и 5 - схемы первого и второго формирователей символов (для преобразователя,шестиразрядного двоич ного кода в шестиразрядный троичный код с двумя символами каждого значения в словах (6,2,2,2)-код; на фиг.6табличное представление (6;2,2,2)кода.

Предлагаемое устройство содержит шины входного кода, блок 2 преобразования младших разрядов входного кода, дешифратор 3 старших разрядов входного кода, первый формирователь 4 символов, шину 5 четных комбинаций, шину 6 нечетных комбинаций, второй формирователь 7 символов, выходные шины 8 j - 8 ц первого ненулевого символа, выходные шины 9 - 9 второго ненулевого символа перестановочного кода, первую и вторую группы Г:ЫХО 1НЫХ шин 10-11.

Шины Ij - 1р младших разрядов входного кода присоединены ко входам блока 2, шины 1q IK старших разрядов входного кода - ко входам дешифратора 3. Выходы блока 2 и выходы дешифратора 3 соединены со входами формирователя 4 символов, выходы которого и шины 5 и 6 соединены со входами формирователя 7 символов, Выходы формирователя 4 подключены также к шинам 8 - Вп-ги 9 - выходы формирователя 7 - к шинам 8а.-1 8у1 и 9n-i , 9rj .

Входное И -разрядное слово полного двоичного кода поступатет в устройство по шинам 1| - 1. По шинам 1 - 1р оно возбуждает блок 2, а по шинам Icj - 1ц - дешифратор 3. Выходные сигналы блока 2 и дешифратора 3 формируют в формирователе 4 ненулевые символы W -2 младших разрядов перестановочного кода. Появление сигнала на любом четйом или нечетном вы ходе блока 2 возбу едает шину 5 или 6 соответственно. При возбуждении шин 5 или б и выхода формирователя 4 в фомирователе 7 формируются ненулевые символы двух старших разрядов перестановочного кода. Сигналы первого

я второго ненулевых символов возбуждают выходные шины соответственно 8 - 8f, и 9п .

Блок преобразования младших раз.)рядов (фиг, 2) содержит дешифратор 12 младших разрядов входного кода, группу элементов ИЛИ 13, первый 14 и второй 15 элементы ИЛИ, которы Формируют единичный выходной сигнал при возбуждении четного или нечетного выхода дешифратора 12.

Рассмотрим работу устройства на примере преобразования слов 000000, 100110 и 111111 двоичного кода в (6; 2,2,2)-код. Поступление первого слова возбуждает в блоке 2 шины а 1 и 5, в дешифраторе 3 - шину Vj, в формирователе 4 - шиныC2,d4 в формирователе 7 - одну из шин о и выходные шины 80, 9, 85 и 9 , образуя слово 010212 перестановочно кода. Поступление слова 100110 возбуждает входные шины Ij, 15 , в блоке преобразования 2 - шиныа, 6, в дешифраторе 3 - шину V. , в формирователе 4 - шиныC,d4 в формирователе 7 - одну из шин CJ и выходные шины 8 , 9., 5 и -Qf, , образуя слово 100221 перестановочного кода. Поступление слова 111111 возбуждает шины 1J. , 1 , в блоке преобразования 2 - шины Q, 6 , в дешираторе 3 - шину Yg, в формирователе 4 - шины dj f С 4 , в формирователе 7 одну из шин и выходные шины 9 , 84 95 и 8, , образуя слово 002121 перестановочного кода. .

Предлагаемое устрйство преобразует перестановочный код во вторичный без потери скорости передачи информации и с ограниченным числом смежных символов одного значения, что важно, например, при передаче ИКМ сигналов в основной полосе, так как ограничивает снизу частотный спектр сигнала и уменьшает межсимвольные искажения.

Преобразователь двоичного кода в (6; 2,2,2)-код позволяет передавать цифровые сигналы на более, чем с тремя нулевыми, и не более,чем с двумя одинаковыми ненулевыми смежными символами. В результате передаваемая последовательность сигнало обладая таким же частотным спектром как у лучших квазитроичных кодов, позволяет упростить линейные узлы передачи и приема, дает возможность обнаружить ошибки по числу символов каждого значения в словах, уменьшит джиттер и повысить надежность синхрнизации за счет равномерной и высокой плотности ненулевых символов.

Использование кода в (6; 2,2,2)код потребовало в 1,6 раза меньше аппаратуры по сравнению с известнымустройством 2 за счет исключения сумматора и других функциональных узлов. Формула изобретения 1. Преобразователь двоичного кода в перестановочный код, содержащий первый и второй формирователи символов лерестановочного кода, выходы которых соединены с выходными шинами преобразователя, отличающийся тем, что, с целью упрощения преобразователя, он содержит блок преобразования младших разрядов входного кода и дешифратор старших разрядов входного кода, выходы которого соединены с первой рруппой входов первого формирователя символов перестановочного кода; вторая группа входов первого формирователя символов перестановочного кода соединена с первой группой выходов блока преобразования младших разрядов входного кода, второй и тр тий выходы которого соединены соответственно с первым и вторым входам второго формирователя символов, тре группа входов второго формирователя символов соединена с первой группой выходов первого формирователя симво Лрв.

Фиг.1

,ji:iii

Фиг.З 2. Преобразователь по п.1, о т личающийся тем, что в нем блок преобразования младших разрядов входного кода содержит п -выходной полный дешифратор младших рязрядов входного кода,группу из п/2 элементов ИЛИ, первый и второй элементы ИЛИ, входы котор X соединены соответственно с четными и нечетными выходами п -выходного полного дешифратора младших разрядов входного кода; выходы первого и второго элементов ИЛИ являются вторыми и третьими выходами блока преобразования младших разрядов входного кода; входы i -го ( i 1 -f п/2) элемента ИЛИ группы соединены, с (2 -1)-ым и 2 выходами дешифратора младших разрядов входного кода, а выходы группы элементов ИЛИ являются выходами блока преобразования младших разрядов входного кода. Источники информации, принятые во внимание при экспертизе 1.Авторское очидетельстЕО СССР W362437, кл. П 03 К 3/80, 1970. 2.Авторское свидетельство СССР W510709, кл.- G 06 F 5/02, 1975.

Фаг.

(е;2,2,г)-код (6;2,2,2}-код

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования разрядного -символьного перестановочного кода в числовой код | 1973 |

|

SU511586A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для преобразования числового кода в -разрядный символьный перестановочный код | 1973 |

|

SU510709A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Устройство сопряжения интерфейсов разной разрядности | 1989 |

|

SU1689962A1 |

| Делитель частоты следования импульсов | 1988 |

|

SU1596453A1 |

| УСТРОЙСТВО для ПЕРЕКОДИРОВАНИЯ ДВОИЧИОГО КОДА В ДВОИЧНЫЙ код с постоянным ВЕСОМ | 1967 |

|

SU191895A1 |

| Устройство для преобразования последовательного десятичного кода в последовательный двоичный код | 1974 |

|

SU636606A2 |

| Устройство для считывания графической информации | 1976 |

|

SU605223A1 |

| Способ преобразования аналогового сигнала в цифровой код и устройство для его осуществления | 1980 |

|

SU1005304A2 |

Авторы

Даты

1979-04-05—Публикация

1977-10-24—Подача