Изобретение относится к вычислительной технике и может быть использовано для сопряжения устройств разной разрядности, а именно когда одно устройство имеет шины большей разрядности, чем второе, и не обязательно разрядности их кратны, в частности для преобразования кода в код интерфейса.

Цель изобретения - упрощение устройства.

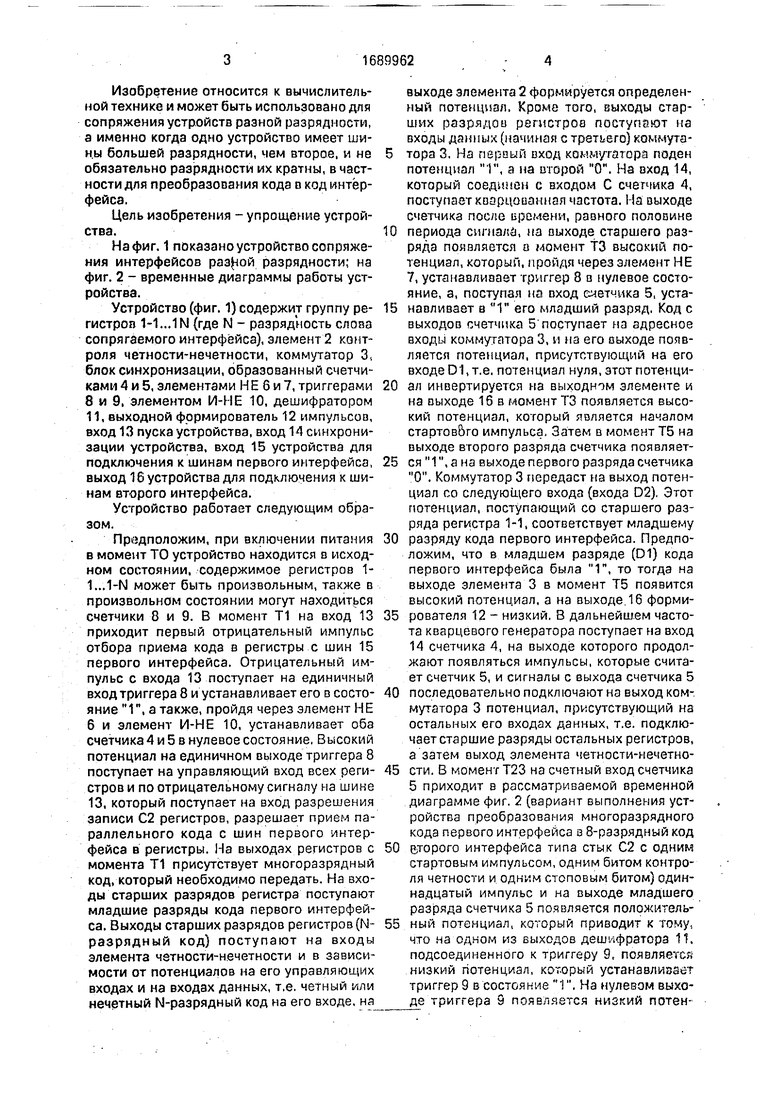

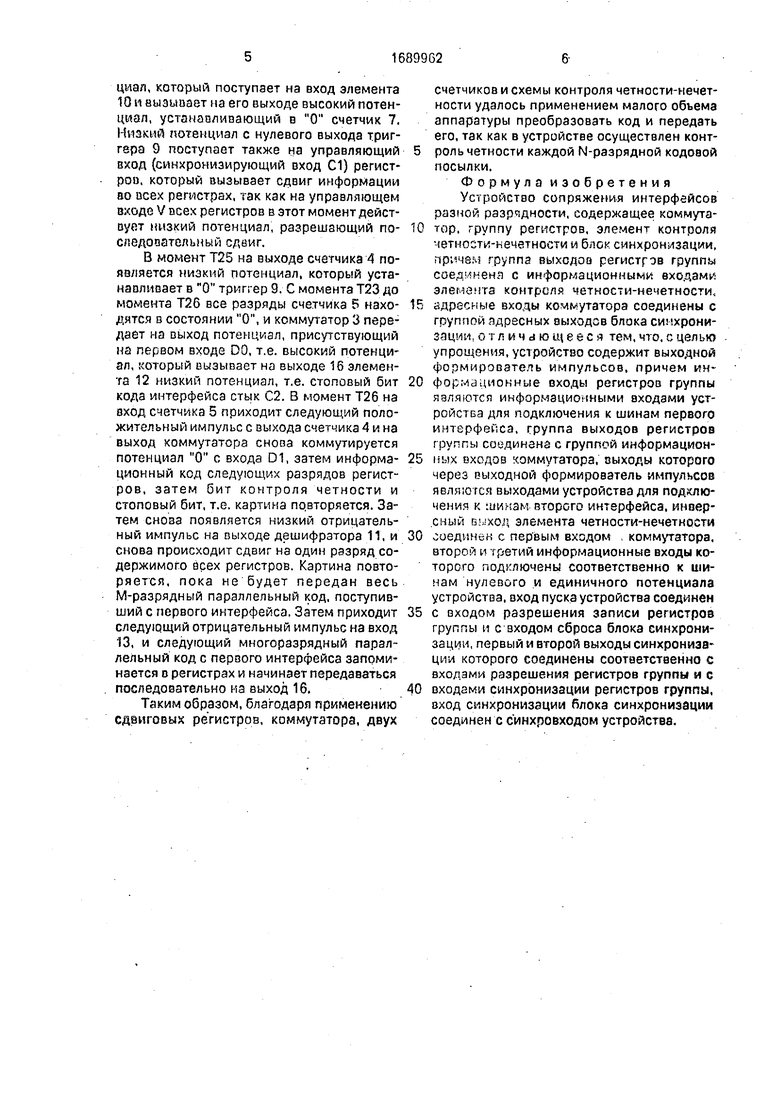

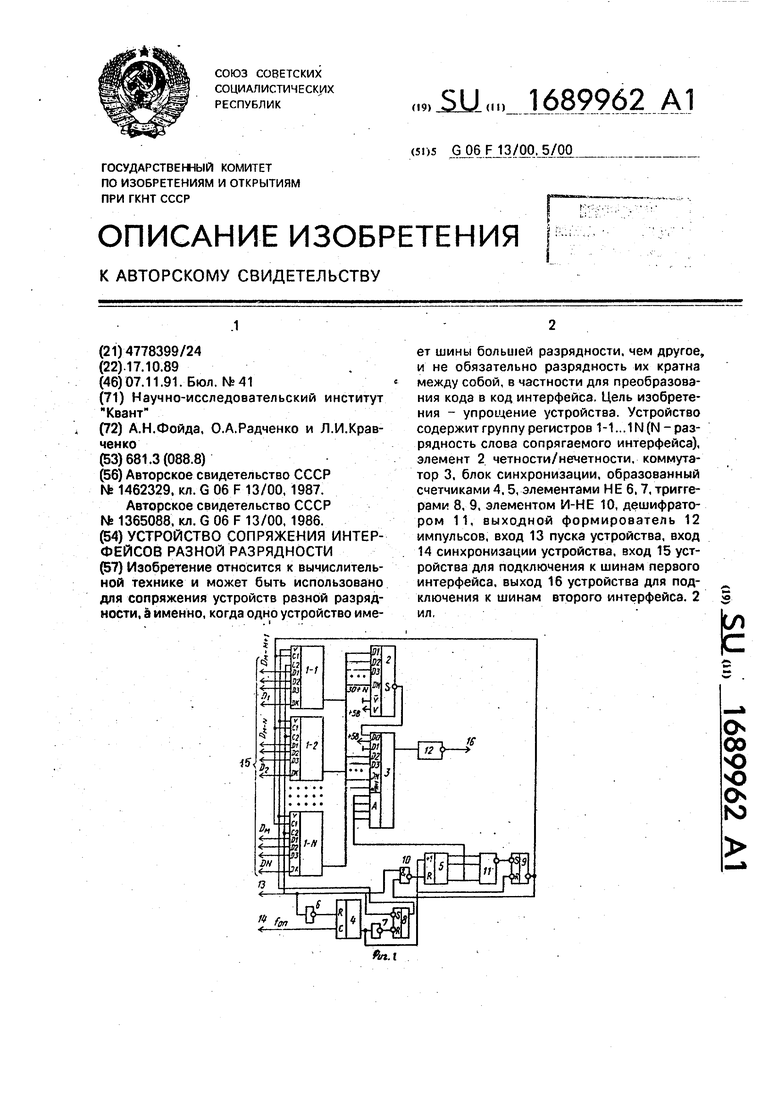

На фиг. 1 показано устройство сопряжения интерфейсов разной разрядности; на фиг. 2 - временные диаграммы работы устройства.

Устройство (фиг. 1) содержит группу регистров 1-1...1N (где N - разрядность слова сопрягаемого интерфейса), элемент 2 контроля четности-нечетности, коммутатор 3, блок синхронизации, образованный счетчиками 4 и 5, элементами НЕ 6 и 7, триггерами 8 и 9, элементом И-НЕ 10, дешифратором 11, выходной формирователь 12 импульсов, вход 13 пуска устройства, вход 14 синхронизации устройства, вход 15 устройства для подключения к шинам первого интерфейса, выход 16 устройства для подключения к шинам второго интерфейса.

Устройство работает следующим образом.

Предположим, при включении питания в момент ТО устройство находится в исходном состоянии, содержимое регистров 1- 1...1-N может быть произвольным, также в произвольном состоянии могут находиться счетчики 8 и 9. В момент Т1 на вход 13 приходит первый отрицательный импульс отбора приема кода в регистры с шин 15 первого интерфейса. Отрицательный импульс с входа 13 поступает на единичный вход триггера 8 и устанавливает его в состояние 1, а также, пройдя через элемент НЕ 6 и элемент И-НЕ 10, устанавливает оба счетчика 4 и 5 в нулевое состояние, Высокий потенциал на единичном выходе триггера 8 поступает на управляющий вход всех регистров и по отрицательному сигналу на шине 13, который поступает на вход разрешения записи С2 регистров, разрешает прием параллельного кода с шин первого интерфейса в регистры. На выходах регистров с момента Т1 присутствует многоразрядный код, который необходимо передать. На входы старших разрядов регистра поступают младшие разряды кода первого интерфейса. Выходы старших разрядов регистров (N- разрядный код) поступают на входы элемента четности-нечетности и в зависимости от потенциалов на его управляющих входах и на входах данных, т.е. четный или нечетный N-разрядный код на его входе, на

выходе элемента 2 формируется определенный потенциал. Кроме того, выходы старших разрядов регистров поступают на входы данных (начиная с третьего) коммутатора 3, На nepaufi вход коммутатора поден потенциал 1, а на второй 0й. На вход 14, который соединен с входом С счетчика 4, поступает кварцоианнал частота. На выходе счетчика после временя, равного полопине

0 периода сигнала, на выходе старшего разряда появляется о момент ТЗ высокий потенциал, который, пройдя через элемент НЕ 7, устанавливает триггер 8 в нулевое состояние, а, поступал на вход счетчика 5, уста5 навливает в 1 его младший разряд. Код с выходов счетчика 5 поступает на адресное входы коммутатора 3, и на его выходе появляется потенциал, присутствующий на его входе D1,т.е. потенциал нуля, этот потенци0 ал инвертируется на выходном элементе и на выходе 16 в момент ТЗ появляется высокий потенциал, который является началом стартового импульса, Затем в момент Т5 на выходе второго разряда счетчика появляет5 ся Г .а на выходе первого разряда счетчика О. Коммутатор 3 передаст на выход потенциал со следующего входа (входа D2), Этот потенциал, поступающий со старшего разряда регистра 1-1, соответствует младшему

0 разряду кода первого интерфейса. Предположим, что в младшем разряде (D1) кода первого интерфейса была 1, то тогда на выходе элемента 3 в момент Т5 появится высокий потенциал, а на выходе 16 форми5 рователя 12 - низкий. В дальнейшем частота кварцевого генератора поступает на вход 14 счетчика 4, на выходе которого продолжают появляться импульсы, которые считает счетчик 5, и сигналы с выхода счетчика 5

0 последовательно подключают на выход коммутатора 3 потенциал, присутствующий на остальных его входах данных, т.е. подключает старшие разряды остальных регистров, а затем выход элемента четности-нечетно5 сти. В момент Т23 на счетный вход счетчика 5 приходит в рассматриваемой временной диаграмме фиг. 2 (вариант выполнения устройства преобразования многоразрядного кода первого интерфейса в 8-разрядный код

0 второго интерфейса типа стык С2 с одним стартовым импульсом, одним битом контроля четности и одним стоповым битом) одиннадцатый импульс и на выходе младшего разряда счетчика 5 появляется положитель5 ный потенциал, который приводит к гаму, что на одном из выходов дешифратора 11, подсоединенного к триггеру 9, появляетсй низкий потенциал, который устанавливает триггер 9 в состояние 1. На нулевом выходе триггера 9 появляется низкий потенцмал, который поступает на вход элемента 10 и вызывает на его выходе высокий потенциал, устанавливающий в О счетчик 7. Низкий потенциал с нулевого выхода триггера 9 поступает также на управляющий вход (синхронизирующий вход С1) регистров, который вызывает сдвиг информации во псех регистрах, так как на управляющем входе V всех регистров в этот момент действует низкий потенциал, разрешающий последовательный сдвиг.

В момент Т25 на выходе счетчика 4 появляется низкий потенциал, который устанавливает в О триггер 9. С момента Т23 до момента Т26 все разряды счетчика 5 находятся в состоянии О, и коммутатор 3 передает на выход потенциал, присутствующий на первом входе DO, т.е. высокий потенциал, который вызывает на выходе 16 элемента 12 низкий потенциал, т.е. столовый бит кода интерфейса стык С2. В момент Т26 на вход счетчика 5 приходит следующий положительный импульс с выхода счетчика 4 и на выход коммутатора снова коммутируется потенциал О с входа D1, затем информационный код следующих разрядов регистров, затем бит контроля четности и столовый бит, т.е. картина повторяется. Затем снова появляется низкий отрицательный импульс на выходе дешифратора 11, и снова происходит сдвиг на один разряд содержимого есех регистров. Картина повторяется, пока не будет передан весь М-разрядный параллельный код. поступивший с первого интерфейса. Затем приходит следующий отрицательный импульс на вход 13, и следующий многоразрядный параллельный код с первого интерфейса запоминается в регистрах и начинает передаваться последовательно на выход 16.

Таким образом, благодаря применению сдвиговых регистров, коммутатора, двух

счетчиков и схемы контроля четности-нечетности удалось применением малого объема аппаратуры преобразовать код и передать его, так как в устройстве осуществлен контроль четности каждой N-разрядной кодовой посылки.

Формула изобретения Устройство сопряжения интерфейсов разной разрядности, содержащее коммутатор, группу регистров, элемент контроля четности-нечетности и блок синхронизации, примем группа выходов регистров группы соединена с информационными входами элемента контроля четности-нечетности,

адресные входы коммутатора соединены с группой адресных выходов блока синхронизации, отличающееся тем, что. с целью упрощения, устройство содержит выходной формирователь импульсов, причем информсыионные входы регистров группы являются информационными входами устройства для подключения к шинам первого интерфейса, группа выходов регистров группы соединена с группой информационних входов коммутатора, выходы которого через выходной формирователь импульсов являются выходами устройства для подключения к юииам второго интерфейса, инверсный &:. ход элемента четности-нечетности

соединен с первым входом коммутатора. второй и третий информационные входы которого подключены соответственно к шинам нулевого и единичного потенциала устройства, вход пуска устройства соединен

с входом разрешения записи регистров группы и с входом сброса блока синхронизации, первый и второй выходы синхронизации которого соединены соответственно с входами разрешения регистров группы и с

входами синхронизации регистров группы, вход синхронизации блока синхронизации соединен с синхровходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь | 1983 |

|

SU1152091A1 |

| Устройство сопряжения интерфейсов | 1989 |

|

SU1817097A1 |

| Устройство для сопряжения интерфейсов | 1991 |

|

SU1798791A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1989 |

|

SU1683022A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| Устройство для разделения коррелограмм | 1987 |

|

SU1432558A1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения устройств разной разрядности, а именно, когда одно устройство имеет шины большей разрядности, чем другое, и не обязательно разрядность их кратка между собой, в частности для преобразования кода в код интерфейса. Цель изобретения - упрощение устройства. Устройство содержит группу регистров 1-1... 1N (N - разрядность слова сопрягаемого интерфейса), элемент 2 четности/нечетности, коммутатор 3, блок синхронизации, образованный счетчиками 4,5, элементами НЕ 6,7, триггерами 8, 9, элементом И-НЕ 10, дешифратором 11, выходной формирователь 12 импульсов, вход 13 пуска устройства, вход 14 синхронизации устройства, вход 15 устройства для подключения к шинам первого интерфейса, выход 16 устройства для подключения к шинам второго интерфейса. 2 ил, Ё О 00 Ч) Ч) с ю

| Устройство для сопряжения двух магистралей | 1987 |

|

SU1462329A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения магистралей | 1986 |

|

SU1365088A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-11-07—Публикация

1989-10-17—Подача