(54) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1981 |

|

SU1003355A2 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Дробный делитель частоты следования импульсов | 1981 |

|

SU993480A1 |

| Делитель частоты с переменным коэффициентом деления | 1976 |

|

SU657619A1 |

| Устройство для деления число-импульсного кода на константу | 1981 |

|

SU1012443A1 |

| Делитель частоты следования импульсов | 1978 |

|

SU766018A1 |

| Устройство для деления чисел | 1981 |

|

SU1013948A1 |

| Пересчетное устройство | 1982 |

|

SU1051698A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1978 |

|

SU786010A1 |

| Делитель частоты следования импульсовС пЕРЕМЕННыМ КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU822377A1 |

Изобретение относится к импульсной технике и может бытьиспользовано в дискретных системах автоматического регулирования, в измерительных устройствах ядерной радиоэлектроники, а- также в схемах селекции импульсов.

Известен делитель частоты периодических импульсов, содержащий пересчетную схему, вентили, триггер, генератор случайных чисел и блок сравнения кодов . 1 .

Недостаток этого устройства - низкая надежность,

Наиболее близким по технической сущности к изобретению является делитель частоты с дррбным переменным коэффициентом деления, содержащий в каждом дробном разряде управляемый делитель, выход которого соединен с еДиниЗсным входом триггера соседнего старшего дробного разряда, второй вход второго вентиля соединен со входом -управляемого делителя своего разряда, выход пересчетной схемы - со входом пересчетнОй схемы соседнего старшего дробного разряда через элемент ИЛИ, выход управляемого делителя целых с единичным входо триггера младшего дробного разряда, первый

входвентиля на входе управляемого делителя целых - с единичным выходом дополнительного триггера, нулевой вход которого связан: с выходом пересчетной схемы старшего дробного разряда, а единичный - со входной шиной и вторым входом вентиля на входе управляемого делителя целых 2.

Недостатком данного устройства яв0ляется его сложность и, вследствие этого, низкая надежность.

Цель изобретения - повышение надежности устройства.

Цель достигается тем, что в дели5тель частоты следования импульсов с переменным коэффициентом деления, содержащий делитель целой части, элементы ИЛИ, триггер и делитель дробной части, введены инвертор, дешифра0тор нуля и формирователь импульсов, выход которого соединен со входом установки нуля делителя целой части и входсм делителя дробной части, а входы - с выходами элементов ИЛИ,

5 первый вход первого из которых соединен с выходом делителя целой части и перв.ыг. входом второго элемента ИЛИ, второй - через инвертор со входом устройства и входом делителя целой

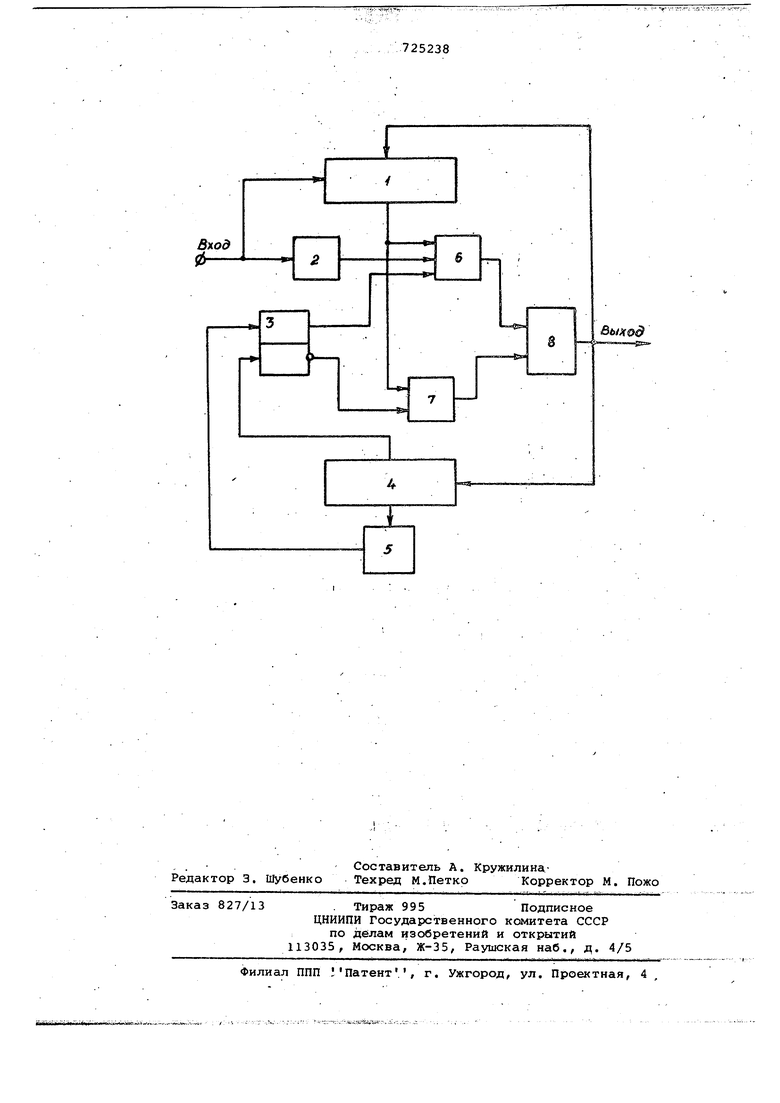

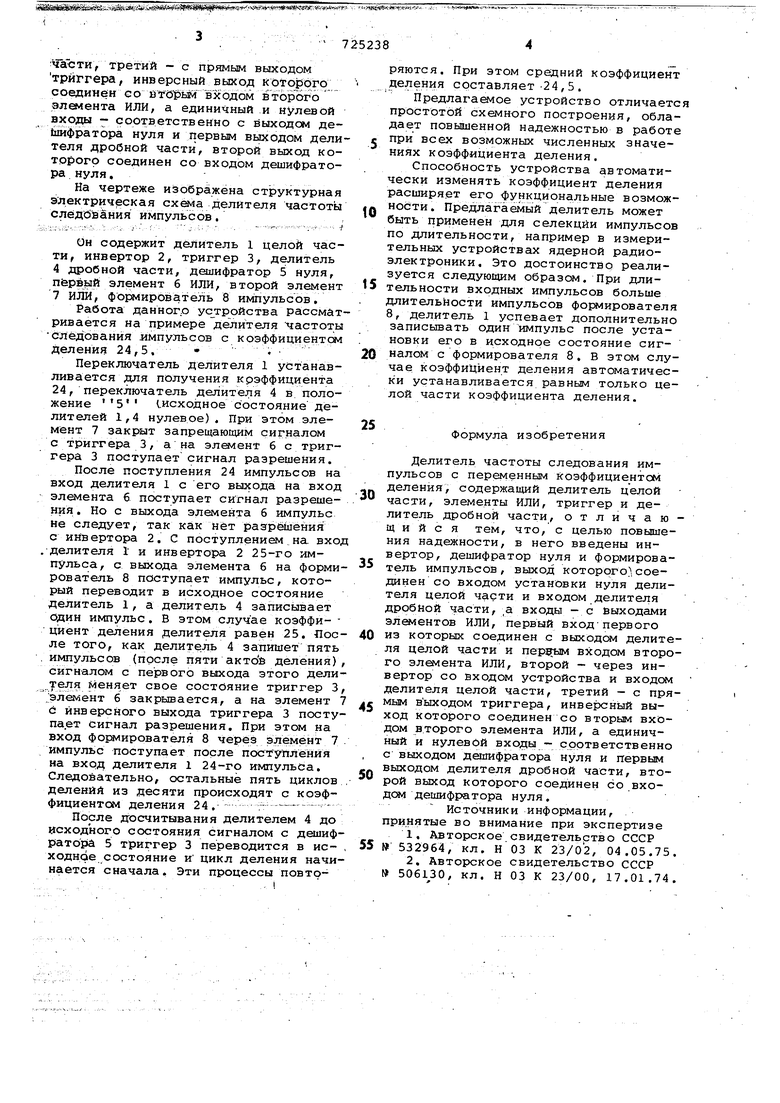

725238 :частиу третий - с прямым выходом триггера, инверсный выход которого соединен со втОрШ входом йторого элемента или, а единичный и нулевой входы - соответственно с выходом дейифратора нуля и первым выходом делителя дробной части, второй выход которого соединен со входом дешифратора нуля, На чертеже изображена структурная электрическая схема делителя частоты слёдйвания импульсов. Он содержит делитель 1 целой части, инвертор 2, триггер 3, делитель 4 дробной части, дешифратор 5 нуля, первый элемент б ИЛИ, второй элемент 7 ИЛИ, фо1 4ирователь 8 импульсов, Работа данного устройства рассмат ривается на примере делителя частоты следования импульсов с коэффициентом деления 24,5. Переключатель делителя 1 устанавливается для получения крэффициента 24, переключатель делителя 4 в положение 5 исходное состояние делителей 1,4 нулевое). При этом элемент 7 закрыт запрещающим сигналом с триггера 3, а на элемент 6 с триггера 3 поступаетсигнал разрешения. После поступления 24 импульсов на вход делителя 1 с его выхода на вход элемента б поступает сигнал разрешения . Но с выхода элемента б импульс не следует, так как нет разрешения с инвертора 2. С поступлением на. вхо .делителя 1 и инвертора 2 25-го импульса, с выхода элемента б на форми рователь 8 поступает импульс, который переводит в исходное состояние делитель 1, а делитель 4 записывает один импульс. В этом случае коэффициент деления делителя равен 25. Пос ле того, как делитель 4 запишет пять . импульсов (после пяти деления) сигналом с первого выхода этого дели теля йеня:ет свое состояние триггер 3 ;элемент б закрывается, а на элемент с Инверсного выхода триггера 3 посту пает сигнал разрешения. При этом на вход фО1 1ирователя 8 через элемент 7 импульс поступает после пост уплёнИя на вход делителя 1 24-го импульса. Следовательно, остальные пять циклов делений из десяти происходят с коэффициентом деления 24,- :---:После досчитывания делителем 4 до исходного состояния сигналом с дешиф ратора 5 триггер 3 переводится в исходнае состояние и цикл деления начи нается сначала. Эти процессы повтояются. При этом средний коэффициент еления составляет 24,5. Пpeдлaгaвvloe устройство отличается простотой схемного построения, облаает повышенной надежностью в работе при всех возможных численных значениях коэффициента деления. Способность устройства автоматиески изменять коэффициент деления асширяет его функциональные возможности. Предлагаемый делитель может быть применен для селекции импульсов о длительности, например в измерительных устройствах ядерной радиоэлектроники. Это достоинство реализуется следующим образом. При длиельности входных импульсов больше лительности импульсов фориирователя 8, делитель 1 успевает дополнительно записывать один импульс после установки его в исходное состояние сигналом с формирователя 8. В этом случае коэффициент деления автоматически устанавливается равным только целой части коэффициента деления. Формула изобретения Делитель частоты следования импульсов с переменным коэффициентом деления, содержащий делитель целой части, элементы ИЛИ, триггер и делитель дробной части, отличающийся тем, что, с целью повышения надежности, в него введены инвертор, дешифратор нуля и формирователь импульсов , выход которого}, соединен со входом установки нуля делителя целой части и входом делителя дробной части, ,а входы - с выходами элементов ИЛИ, первый входпервого из которых соединен с выходом делителя целой части и перггым входом второго элемента ИЛИ, второй - через инвертор со входом устройства и входом делителя целой части, третий - с прямым выходом триггера, инвегкгный выход которого соединен со вторым входом второго элемента ИЛИ, а единичный и нулевой входы - соответственно с выходом дешифратора нуля и первым выходом делителя дробной части, второй выход которого соединен со входсм дешифратора нуля. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельртво СССР № 532964, кл. И 03 К 23/02, 04.05.75. 2.Авторское свидетельство СССР 506130, кл. И 03 К 23/00, 17.01.74.

Авторы

Даты

1980-03-30—Публикация

1978-11-02—Подача