(54) ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейно-круговой интерполятор | 1977 |

|

SU741234A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Интерполятор для систем программного управления | 1977 |

|

SU658528A1 |

| Цифровой интегратор | 1978 |

|

SU698017A1 |

| Устройство для числового программного управления | 1983 |

|

SU1124251A1 |

| Линейно-круговой интерполятор | 1978 |

|

SU746431A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

| Линейно-круговой интерполятор | 1984 |

|

SU1215090A2 |

| Цифровой интерполятор | 1984 |

|

SU1238033A1 |

| Цифровой интерполятор | 1981 |

|

SU1003022A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах программного управления станками. Известен линейно-круговой интерполятор, построенный на основе цифровых дифференциаль:ьгх анализаторов (ЦДА) параллельного действия, в котором для повышения точности интерполяции окружности за счет исключения погрешности интегрирования работа каждого из двух охваченных обратной связью интеграторов происходит последовательно 1. Недостатком этого устройства является низкое быстродействие (в два раза меньше, чем у интерполяторов с одновременно работающими интеграторами а также сложность схем синхронизации . Известен также интерполятор с одно временно работающими интеграторами системы числового программного управления H33-IM, содержащий блок задания программы, блок задания скорости, блок выделения приращений, коммутатор, два интегратора 2. Недостатками устройства являются болыш е затраты оборудования, низкая точность, сложность схем синхронизации. Наиболее близким по технической сущности к предлагаемому является линейно-круговой интерполятор, содержаЕ{ий блок задания программы, блок задания скорости, элементы И, блок выделения приращений, коммутатор и два интегратора, каждый из которых содержит счетчик перемещения, первый и второй сдвиговые регистры, первый, второй и третий сумматоры, элемент ИЛИ, причем первые входы всех сдвиговых регистров каждого интегратора соединены с выходами блока задания скорости, зторые входы первых сдвиговых регистров соединены с первыми выходами блока задания программы, их третьи входы соединены с выходами первых сумматоров и первыми входами вторых сумматоров, выходы первых сдвиговых регистров соединены с первыми входами первых сумматоров, втот рой выход блока задания программы соединен с первым входом коммутатора, третьи выходы блока задания программы соединены с первыми входами счетчиков перемещений, вторые входы которых соединены со вторыми входами коммутатора, выходами блока выделения приращений и выходами линейнокругового интерполятора, выходы

счетчиков перемещений соединены со.„

щ.

входами элемента И, выход которого связан с первым входом блока задания скорости, второй вход которого соединен с четвертым выходом блока задания прохраммы, а первые выходы вторых сумматоров соединены со входами блока выделения приращений, вторые выхода, вторых сумматоров соединены со вторыми входами вторых сдвиговых регистров, первые входы третьих сумматоров- соединены с выходами вторых сдвиговых регистров, вторые входы третьих сумматоров и первые входы элементов ИЛИ соединены с первыми выходами коммутатора, вторые входы элементов ИЛИ соединены со вторыми выходами коммутатора, выходы элементов ИЛИ соединены со вторыми входами первых сумматоров, а выходы третьих сумматоров - со вторыми входами вторых сумматоров L 3J.

Недостатком этого интерполятора являются большие затраты оборудования и сложность схем синхронизации.

Цель изобретения - сокращение обо.рудования и упрощение интерполятора.

Указанная цель достигается тем, что линейно-круговой интерполятор, содержащий первый и второй вычислительные блоки, каждый из которых содерлсит первый, второй и третий сумматоры, элемент ИЛ11 и счетчик перемещения , причем первый вход первого сумматора соединен с первым входом элемента ИЛИ, выход которого соедине с первым входом второго сумматора, соединенного выходом с первым входом третьего сумматора, второй вход которого подключен к выходу первого сумматора, первые выходы третьих сумматоров соединены соответственно с первым и вторым входами блока выделения приращений, первые входы элементов ИЛИ подключены к первому и второму выходам коммутатора, вторые входы элементов ИЛИ соединены соответственно с третьим и четвертым выходами коммутатора, первый и второй входы которого соединены соответственно с, первым и вторым выходом блока выделения приращений и с первыми входами счетчиков перемещений, выходы которы соединены с первым и вторым входами элементов И, выход которого соединен с первым входом блока задания скорости, второй вход которого соединен с первым выходом блока задания программы, второй и третий выходы которого соединены со вторыми входами счетчиков перемещений, а четвертый выход с третьим входом коммутатора, содержит блок памяти и счетчик адреса, управляющий и установочный входы которого соединены с первым и вторым выходами блока задания.скорости соответственно, выходы счетчика адреса соединены с адресными входами блока памяти, первый и второй управляющие входы которого соединены соответственно с третьим и четвертым выходами блоКур задания скорости, первый и третий {зазрядные входы блока памяти соединены со вторыми выходами соответствующих третьих сумматоров, второй и четвертый разрядные входы блока памяти соединены с выходами вторых сумматоров, а также с пятым и шестым выходами блока задания программы соответственно, первый и второй разрядные- выходы блока памяти соединены со вторыми входами первых сумматоров, а третий и четвертый разрядные выходы - со вторыми входами вторых сумматоров.

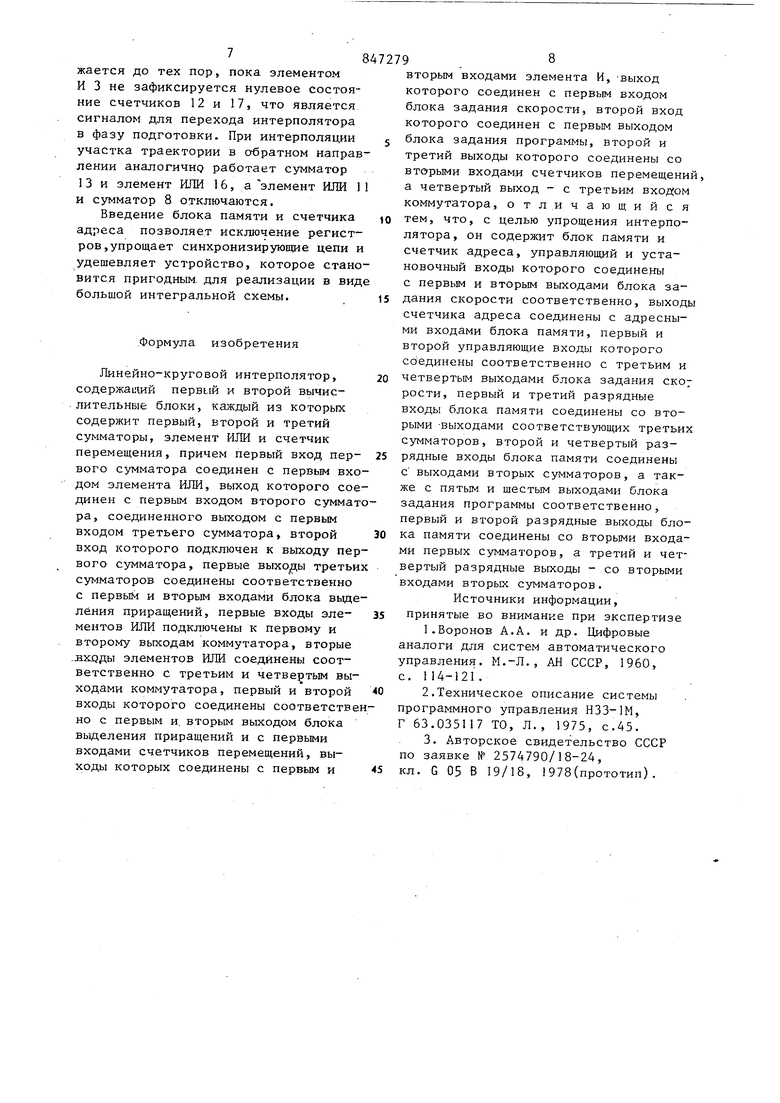

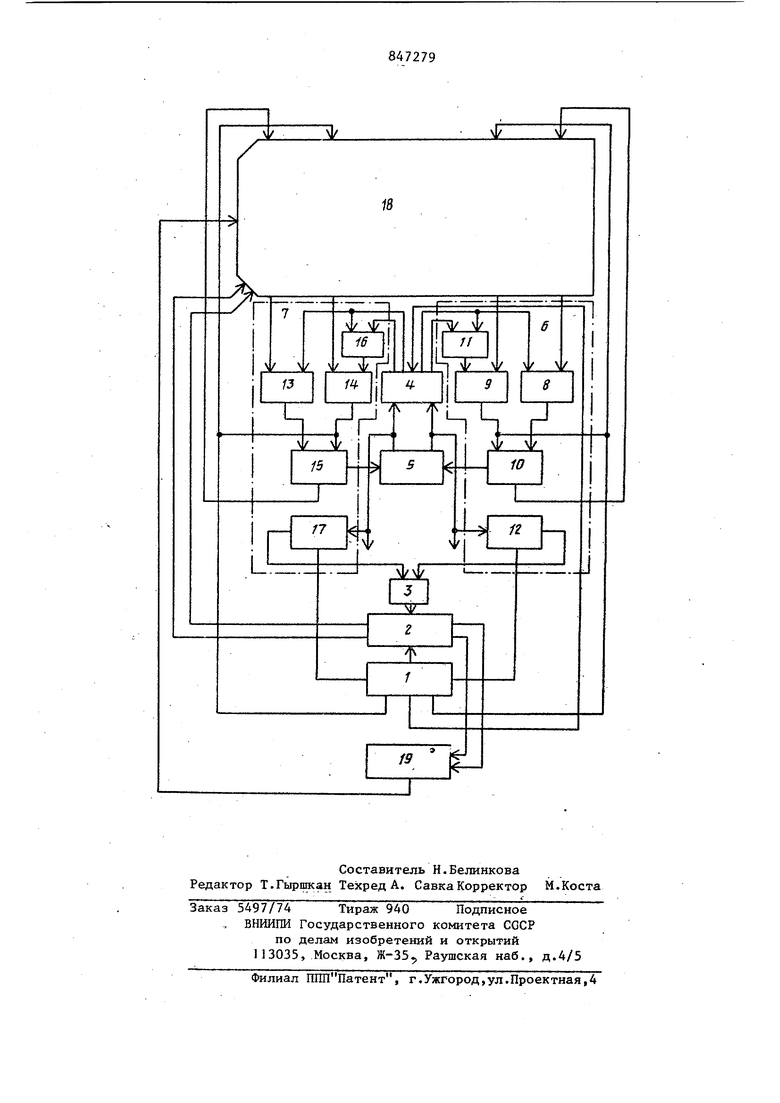

На чертеже представлена функциональная схема линейно-кругового интерполятора .

Интерполятор содержит блок 1 задания программы, блок 2 задания скорости, элемент И 3, коммутатор 4, блок 5 выделения приращений, вычислительные блоки 5 и 7. Блок 6 содержит первый 8, второй 9 и третий 10 сумматоры, элемент ИЛИ 11, счетчик 12 перемещений. Блок 7 содержит первый 13, второй 14 и третий 15 сумматоры, элемент ИЛИ 16, счетчик 17 перемещений. Устройство содержит также блок 18 памяти и счетчик 19 адреса.

Блок 18 памяти представляет собой оперативное запоминающее устройство. Сумматоры 8-10 и 13 - 15 представляют собой одноразрядные комбинационные сумматоры, счетчики 12,17 и 19 суммирующие счетчики, причем разрядность счетчиков 12 и 17 определяется максимальной разрядностью приращений а разрядность счетчикоординат19 - как log п, так как информакация в блоке 18 располагается по принципу разряд на ячейку, т.е. вертикальным образом. Так, например в первом информационном сечении (ИС) блока 18 происходит накопление подынтегральной функции, которая располагается во втором ИС (ИС2). Совместно с блоком 6 ИС1 и ИС2 образуют первый интегратор, а ИСЗ и ИС4 совместно с обрабатывающим блоком 7 образуют второй интегратор. Элементы И 3, ИЛИ 11 и 1 6 представляют собой элементы,реализующие логические функции И и ИЛИ соответственно. Коммутатор 4 организо ван в виде шифратора, блок 5 осуществляет выделение и хранение переноса со старшего значащего разряда информации, хранимой в ИС1 и ИС4, и включает необходимые комбинационные схемы и два триггера. Блок 2 задания скорости определяет работу устройства, управляет работой блока 18 памяти и счетчиком 19 и представляет собой генератор тактовых сигналов. Блок 1 задания программы необходим для хранения программы, загрузки ИС блок 18 памяти и управления коммутатором. Он включает фотосчитывающее устройство с необходимыми логическими схемами Функционирование интерполятора рас падается на две фазы. Б фазе подготовки блок 2 по установочному входу обнуляет счетчик 19, что соответствует установлению адреса нулевой ячейки. С выходов блока 1 в ИС2 и ИСЗ записываются младшие разряды приращений координат j|v X и л у при линейной интерполяции или координаты начальной точки дуги х, у при круговой, при .этом подается сигнал Запись в блок 18 по выходу блока 2 задания скорости Блок 2 увеличивает содержимое счетчика 19 на I и происходит запись еле- дуюшлх разрядов в ИС2 и ИСЗ. После записи всех разрядов чисел в ИС2 и ИСЗ с выходов блока 1 в счетчики 12 и 17 записываются приращение координат X, лу при линейной интерполяции и Хц,уц - при круговой, а счетчик 19 обнуляется. После интерполятор переходит в рабочую фазу, в которой осу894 ществляется либо линейная, либо круговая интерполяция. В режиме линейной интерполяции , поступившей из блока 1, коммутатор 4 блокируется, поэтому суь маторы 8п9, 13и 14, а также элементы ИЛИ 11 и 16 на работу интерполя тора влияния не оказывают. Приращении Дх и ду . хранимые в ИС2 и ИСЗ после довательно суммируются с содержимым ИС и ИС4 соответственно, суммирование производится последовательно по разрядам на сумматорах 10 и 15 при по даче сигнала Чтение с блока 2. После суммирования одноименных разрядов подается сигнал запись р. блока 2, и в соответствующий разряд ИС1 записывается сумма данных разрядов. Выделенные после сложения блоком 5 переносы поступают на выход интерполятора и на вычитающие входы счетчиков 12 и 17. При обнулении счетчиков 12 и 17 элемент И 3 вырабатывает сигнал,свидетельствующий об окончании отработки участка траектории. После этого устройство вновь переходит в фазу подготовки и процесс повторяется. В режиме круговой интерполяции в зависимости от команды, поступившей из блока 1 и определяющей четверть окружности и направление движения, устанавливается порядок работы интеграторов . Если подынтегральная функция интегратора, образованного обрабатывающим блоком 6 и ИС1, ИС2 увеличивается, то подынтегральная функция интегратора, образованного обрабатывающим блоком 7 и ИСЗ, ИС4,уменьшается. В этом случае происходит суммирование С1 и ИС2, а также ИСЗ и ИС4, как и при линейной интерполяции. Выделенный перенос поступает с выхода блока 5 через коммутатор 4 на вход ИЛИ 11 и вход сумматора 8. Относительно начала сложения сигнал переноса эквивалентен коду 000...01, который поступает на входы сумматоров 8 и 9 и обеспечивает эффект попеременной работы интеграторов, а также коррекцию подынтегральной функции в ИС2 на сумматоре 9 на +1. Перенос, возникающий с первого выхода блока 5, поступает через коммутатор 4 на вход элемента ИЛИ 16 и на вход сумматора 14 в виде 11 Г.. . 1, и обеспечивает коррекцию подынтегральной функции в ИСЗ на -} на сумматоре 14. Интерполяция дуги, таким образом, продолжается до тех пор, пока элементом И 3 не зафиксируется нулевое состояние счетчиков 12 и 17, что является сигналом для перехода интерполятора в фазу подготовки. При интерполяции участка траектории в обратном направлении аналогично работает сумматор 13 и элемент ИЛИ 16, а элемент ИЛИ II и сз матор 8 отключаются.

Введение блока памяти и счетчика адреса позволяет исключение регистров,упрощает синхронизирующие цепи и удешевляет устройство, которое становится пригодным, для реализации в виде большой интегральной схемы.

Формула изобретения

Линейно-круговой интерполятор, содержаний первый и второй вычислительные блоки, каждый из которых содержит первый, второй и третий сумматоры, элемент ИЛИ и счетчик перемещения, причем первый вход первого сумматора соединен с первым входом элемента ИЛИ, выход которого соединен с первым входом второго сумматора, соединенного выходом с первым входом третьего сумматора, второй вход которого подключен к выходу первого сумматора, первые третьих сумматоров соединены соответственно с первым и вторым входами блока выделения приращений, первые входы элементов ИЛИ подключены к первому и второму выходам коммутатора, вторые .входы элементов ИЛИ соединены соответственно с третьим и четвертым выходами коммутатора, первый и второй входы которого соединены соответственно с первым и. вторым выходом блока выделения приращений и с первыми входами счетчиков перемещений, выходы которых соединены с первым и

вторым входами элемента И, -выход которого соединен с первым входом блока задания скорости, второй вход которого соединен с первым выходом блока задания программы, второй и третий выходы которого соединены со вто-рыми входами счетчиков перемещени а четвертый выход - с третьим входом коммутатора, о тли чающийся тем, что, с целью упрощения интерполятора, он содержит блок памяти и счетчик адреса, управляющий и установочный входы которого соединены с первым и вторым выходами блока задания скорости соответственно, выход счетчика адреса соединены с адресными входами блока памяти, первый и второй управляющие входы которого соединены соответственно с третьим и четвертым выходами блока задания ско рости, первый и третий разрядные входы блока памяти соединены со вторыми -выходами соответствующих третьи сумматоров, второй и четвертый разрядные входы блока памяти соединены с выходами вторых сумматоров, а также с пятым и шестым выходами блока задания программы соответственно, первый и второй разрядные выходы блока памяти соединены со вторыми входами первых с-умматоров, а третий и четвертый разрядные выходы - со вторыми входами вторых сумматоров.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-07-15—Публикация

1979-06-26—Подача