Изобретение относится к области автоматики и вычислительной техники и может быть использовано в системах программного управления станками. Известны линейно-круговые интерпо ляторы, построенные на основе цифровых дифференциальных анализаторов (ЦЦА) параллельного действия, в кото рых для повышения точности интерполя ции окружности эа счет исключения погрешности интегрирования, работа каждого из двух охваченных обратной связью интеграторов происходит последовательно 1. Недостатком этих устройств является двойное снижение быстродействия (по сравнению с устройствами с синхронно работающими интеграторами) компенсация которого эквивалентна увеличению объема электронного обору дования в два раза. Наиболее близким техническим решением к данному изобретению является линейно-круговой интерполятор на основе ЦДЛ последовательного действи с синхронно работающими интегратора ми системы числового программного управления, содержащий блок задания програмкш, блок задания скорости, элемент И, блок памяти координатных приращений, коммутатор, два интегратора, каждый из которых содержит счетчик, первый и второй регистры, первый и второй сумматоры, блок памяти старшего разряда, преобразователь последовательно-параллельного кода в последовательный, схему блокировки уменьшения номера старыего разряда, причем первые входы всех регистров каждого интегратора соединены с выходами блока задания скорости, вторые входы первых регистров связаны с первыми выходами блока задания программы и входами блоков памяти, третьи входы первых сдвиговых регистров связаны с выходами первых сумматоров и первыми входами вторых сумматоров, выходы первых сдвиговых регистров связаны с первыми входами первых сумматоров, второй выход блока задания программа соединен с пер-, вым входом коммутатора, третьи выходы блока задания программы соединены с первыми входами счетчиков, вторые входы которых связаны со вторыми входами коммутатора, подключены к выходам блока памяти координатных приращений и выходам интерполятора, счетчиков связаны со входами элемента И, выход которого связан с первым входом блока задания скорости, второй вход которого связан с четвертым выходом блока задания nporpaMNtJ, а первые выходы вторых сумматоров соединены через преобразователи последовательно-параллельного кода в последовательный со входом блока памяти координатных приращений, вторые входы которого соединены с выходами схем блокировки уменьшения номера старшего разряда, вторые выходы вторых сумматоров соединены со вторыми входами вторых ре гистров, а выходы блоков памяти старшего разряда связаны со, входами схем блокировки уменьшения номера старшего разряда и третьими входами блока памяти координатных приращений 2.

Недостатком этого интерполятора является его низкая точность, а увеличение точности такого интерполятора за счет последовательной работы интеграторов вызывает также снижение быстродействия вдвое, что учитывая многотактность работы последовательного интегратора, приводит к недопустимому снижению быстродействия. Действительно, при использовании 24-разрядных чисел цикла операция увеличивается на 25 тактов.

Целью изобретения является повышение точности, а стродействия интерполятора и уменьшение затрат оборудования.

Поставленная цепь достигается тем, что в линейно-круговом интерполяторе, содержащем коммутатор, первые входы которого соединены с выходами блока памяти координатных приращений, а второй вход - с первым выходом блока задания программы, подключенного вторым выходом к первому входу блока задания скорости, второй вход которого подсоединён к выходу элемента И, и координатные интеграторы, каждый из которых состоит из сче тчика и последовательно соединенных первого регистра, первого сумматора, .второго сумматора и второго регистра, второй вход которого подключен к соответствующему выходу блока задания скорости и первому входу первого регистра/ соединенного вторым входом с выходом первого сумматора, а третьим входом - с соответствующим третьим выходом блока задания программы, соответствующий четвертый выход которого подключен к первому входу счетчика, соединенного выходом с соответствующим входом элемента И, а вторым входом - с выходом интерполятора и с соответствующим выходом блока памяти координатных приращений, подключенного одним из входов ко второму выходу второго сумматора, каждый координатный интегратор содержит элемент ИЛИ и третий сумматор, выход которого подключен ко второму входу второго сумматора, первый вход -I к выходу второго регистра, а второй вход - к соответствующему первому выходу коммутатора и к первому входу элемента ИЛИ, выход которого соединен со вторым входом первого сумматора, а второй вход - с соответствующим вторым выходом коммутатора.

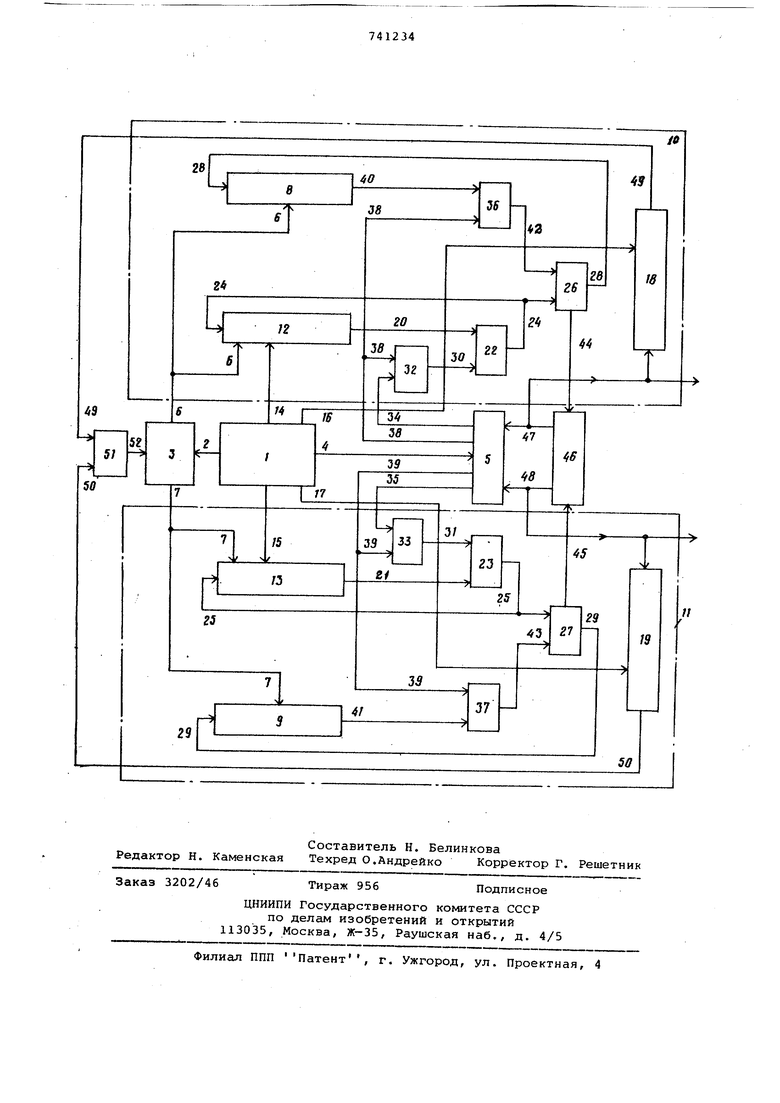

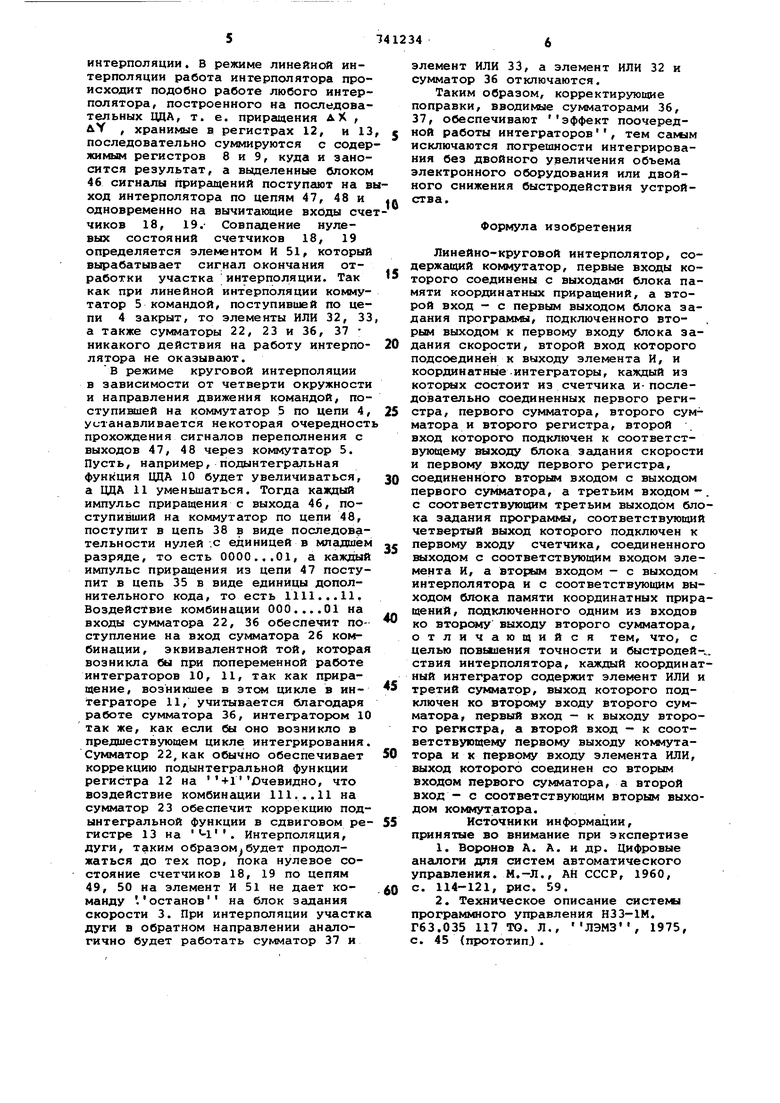

На чертеже показана структурная схема интерполятора.

0 Интерполятор состоит из блока задания программы 1, с выхода которого информация о величине подачи по цепи 2 поступает в блок задания скорости 3, а по цепи 4 информация, определяющая направление движения при круговой интерполяции, поступает в коммутатор 5 сигналов обратной связи. С выходов блока задания скорости 3 по цепям 6 и 7 тактовые импульсы поступают во вторые регистры 8 и 9 координатных интеграторов 10 и 11. В первые регистры 12 и 13 с выходов блока задания nporpaMjAd 1 по цепям 14 и 15 заносятся величины приращений дХ. / л при линейной интерполяции или коорди.наты начальной точки дуги окружности н/Ifn при круговой, а по цепям 16, 17 в счетчики 18, 19 заносятся приращения координат дХ , лЧ при линейной интерполяции и ЛХ ,ЛХ - при круговой.

0 Выходы младших разрядов регистров 12 и 13 цепями 20, 21 связаны с первыми сумматорами 22, 23, служащими для коррекции значений подынтегральных функций, а их выходы по цепям 24, 25

5 связаны со входами старших разрядов регистров 12 и 13 и входами вторых сумматоров 26, 27, выходы которых подключены по цепям 28, 29 к старшим разрядам регистров 8 и 9. Вторые вхо0 ДЫ сумматоров 22, 23 по цепям 30, 31 связаны с выходами элементов ИЛИ 32, 33, входы которых по цепям 34, 35 соединены с выходами коммутатора 5. Первые входы элементов ИЛИ 32, 33 и вторые входы сумматоров 36, -37 по цепям

38, 39 соединены с коммутатором 5. Первые входы третьих сумматоров 36, 37 цепями 40, 41 связаны с младшими разрядами регистров 8 и 9, а выходы сумматоров 36, 37 по цепям 42, 43 0 со вторыми входами сумматоров 26, 27. Выходы сигналов переполнения сумматоров 26 и 27 цепями 44 и 45 связаны со входами блока памяти координатных приращений 46, с выходов которого по

5 цепям 47, 48 сигналы приращений соответствующих координат поступгиот на входы коммутатора 5, счетчиков 18, 19 и выход интерполятора. Сигналы нулевого состояния счетчиков 18, 19 по

ft цепям 49, 50 поступают на входы элемента И 51, выход которого цепью 52 подключен ко входу блока задания скорости 3.

Интерполятор может работать в двух

, режимах; в режиме линейной и круговой интерполяции. В режиме линейной интерполяции работа интерполятора происходит подобно работе любого интерполятора, построенного на последовательных ОДА, т. е. приращения АХ , ЛУ , хранимые в регистрах 12, и 13 последовательно суммируются с содер жимым регистров 8 и 9, куда и заносится результат, а вьщеленные блоком 46 сигналы приращений поступгиот на в ход интерполятора по цепям 47, 48 и одновременно на вычитакяцие вхбды сче чинов 18, 19.- Совпадение нулевых состояний счетчиков 18, 19 определяется элементом И 51, который вырабатывает сигнал окончания отработки участка интерполяции. Так как при линейной интерполяции коммутатор 5 командой, поступившей по цепи 4 закрыт, то элементы ИЛИ 32, 33 а также сумматоры 22, 23 и 36, 37 никакого действия на работу интерполятора не оказывают. в режиме круговой интерполяции в зависимости от четверти окружности и направления движения командой, поступииией на коммутатор 5 по цепи 4, устанавливается некоторая очередност прохождения сигналов переполнения с выходов 47, 48 через коммутатор 5. Пусть, например, подынтегральная функция ОДА 10 будет увеличиваться, а ЦЦА 11 уменьшаться. Тогда каждъхЯ импульс приращения с выхода 46, поступивший на коммутатор по цепи 48, постугшт в цепь 38 в виде последов 1тельности нулей .с единицей в младшем разряде, то есть 0000...01, а каждый импульс приращения из цепи 47 поступит в цепь 35 в виде единицы дополнительного кода, то есть 1111...11. Воздействие комбинации 000....01 на входы сумматора 22, 36 обеспечит поступление на вход сумматора 26 комбинации, эквивалентной той, которая возникла бы при попеременной работе интеграторов 10, 11, так как приращение, вознимиее в эт(Я4 цикле в интеграторе 11, учитывается благодаря работе сумматора 36, интегратором 10 так же, как если бы оно возникло в предшествующем цикле: интегрирования. Сумматор 22,как обычно обеспечивает коррекцию подынтегральной функции регистра 12 на + Очевидно, что воздействие комбинации 111.. .11 на сумматор 23 обеспечит коррекцию подынтегральной функции в сдвиговом регистре 13 на -I. Интерполяция, дуги, таким образом будет продолжаться до тех пор, пока нулевое состояние счетчиков 18, 19 по цепям 49, 50 на элемент И 51 не дает команду .останов на блок задания скорости 3. При интерполяции участка дуги в обратном направлении аналогично будет работать сумматор 37 и элемент ИЛИ 33, а элемент ИЛИ 32 и сумматор 36 отключаются. Таким образом, корректирующие поправки, вводимые сумматорами 36, 37, обеспечивают эффект поочередной работы интеграторов , тем cai«iM исключаются погрешности интегрирования без двойного увеличения объема электронного оборудования или двойного снижения быстродействия устройства. Формула изобретения Линейно-круговой интерполятор, содержащий коммутатор, первые входы которого соединены с выходами блока памяти координатных приращений, а второй вход - с первым выходом блока задания программы, подключенного вторым выходом к первому входу блока задания скорости, второй вход которого подсоединен к выходу элемента И, и координатные-интеграторы, каждый из KOTOfftix состоит из счетчика и-последовательно соединенных первого регистра, первого сумматора, второго сумматора и второго регистра, второй вход которого подключен к соответствующему выходу блока задания скорости и первому входу первого регистра, соединенного вторым входом с выходом первого сумматора, а третьим входом-, с соответствующим третьим выходом блока задания программы, соответствующий четвертый выход которого подключен к первому входу счетчика, соединенного выходом с соответствующим входом элемента И, а вторым входом - с выходом интерполятора и с соответствующим выходом блока памяти координатных приращений, подключенного одним из входов ко вторсаду выходу второго сумматора, отличающийся тем, что, с целью повыиения точности и быстродей-.. ствия интерполятора, каждый координатный интегратор содержит элемент ИЛИ и третий сумматор, выход которого подключен ко вторсялу входу второго сумматора, первый вход - к выходу второго регистра, а второй вход - к соответствующему первому выходу коммутатора и к перврму входу элемента ИЛИ, выход которого соединен со вторым входом первого сумматора, а второй вход - с соответствующим вторым выходом коммутатора. Источники информации, принятые во внимание при экспертизе 1.Воронов А. А. и др. Цифровые аналоги для систем автоматического управления. М.-Л., АН СССР, 1960, с. 114-121, рис. 59. 2.Техническое описание система программного управления НЗЗ-1М. Г63.035 117 ТО. Л., ЛЭМЗ, 1975, с. 45 (прототип.) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейно-круговой интерполятор | 1979 |

|

SU847279A1 |

| Интерполятор для систем программного управления | 1977 |

|

SU658528A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Линейно-круговой интерполятор | 1978 |

|

SU746431A1 |

| Цифровой интерполятор | 1981 |

|

SU1003022A1 |

| Линейный интерполятор | 1987 |

|

SU1439532A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

| Графический интерполятор | 1985 |

|

SU1401509A1 |

| Линейно-круговой интерполятор | 1986 |

|

SU1312530A1 |

| Многокоординатный цифровой линейный интерполятор | 1987 |

|

SU1522154A1 |

Авторы

Даты

1980-06-15—Публикация

1977-01-27—Подача