1

Изобретение относится к импульсной технике.

Известно устройство для контроля делителя частоты, содержащее генератор случайных сигналов, генератор тактовых импульсов, счетчики, декодирующие устройства, временные переключатели, логические схемы 1.

Такое устройство не позволяет получить достаточной точности контроля.

Наиболее близким по технической сущности к данному изобретению является устройство, содержащее хранитель времени, один выход которого соединен со входом контролируемого делителя частоты, второй выход подключен к первому входу логического элемента И, и входу сброса бинарного счетчика секунд, второй вход которого соединен с выходом контролируемого делителя частоты, третий и четвертый выход хранителя времени соединены соответственно со входами разрядов бинарных счетчиков секунд и минут и входами сброса бинарных счетчиков минут и часов, а пятый выход хранителя времени соединен с входами разрядов контролируемого делителя частоты и бинарного счетчика часов, регистры памяти, выходы которых подключены ко входам блока преобразования часов и минут в секунды, выходы которого подключены ко входам блока регистрации временного рассогласования.

Это устройство также не обеспечивает достаточной точности контроля.

Целью изобретения является повышение точности контроля.

Поставленная цель достигается тем, что в устройство для контроля делителя частоты, содержащее хранитель времени, один

выход которого соединен со входом контролируемого делителя частоты, второй выход подключен к входу сброса бинарного счетчика секунд и к первому входу логического элемента И, второй вход которого

соединен с выходом контролируемого делителя частоты, третий и четвертый выход хранителя времени соединены соответственно со входами разрядов бинарных счетчиков секунд и минут и входами сброса

бинарных счетчиков минут и часов, а пятый выход хранителя времени соединен с входами разрядов контролируемого делителя частоты и бинарного счетчика часов, регистры памяти, выходы которых подключены ко входам блока преобразования часов и минут в секунды, выходы которого подключены ко входам блока регистрации временного рассогласования, введены дополнительные двухвходовые логические

элементы И, включенные между выходами

разрядов бинарных счетчиков секунд, минут и часов и входами разрядов регистров памяти, причем вторые входы дополнительных двухвходовых логических элементов И подключены к выходу упомянутого логичеСКОРО элемента И, а блок преобразования часов и минут в секунды содержит параллельный шестиразрядный комбинационный сумматор, два параллельных четырехразрядных комбинационных сумматора, и нараллельный, нятнадцатиразрядный комбинационный сумматор, выходы которого являются выходами блока преобразования часов и минут в секунды, вход сброса соединен с выходом первого из упомянутых параллельных четырехразрядных комбинационных сумматоров, входы которого соединены с выходами второго параллельного четырехразрядного сумматора, входы которого и входы параллельных шестиразрядного и пятнадцатиразрядного комбинационных сумматоров являются входами блока преобразования часов и минут в секунды, а выход параллельного шестиразрядного комбинационного сумматора соединен со входом второго из упомянутых параллельных четырехразрядных комбинационных сумматоров.

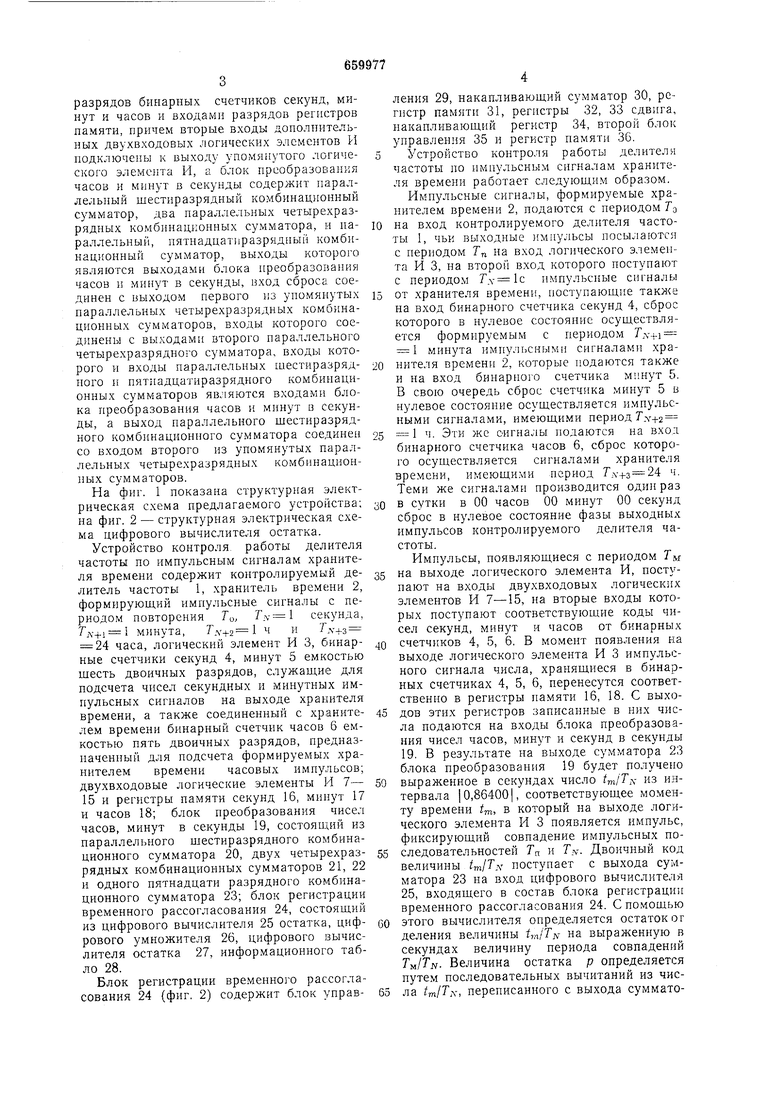

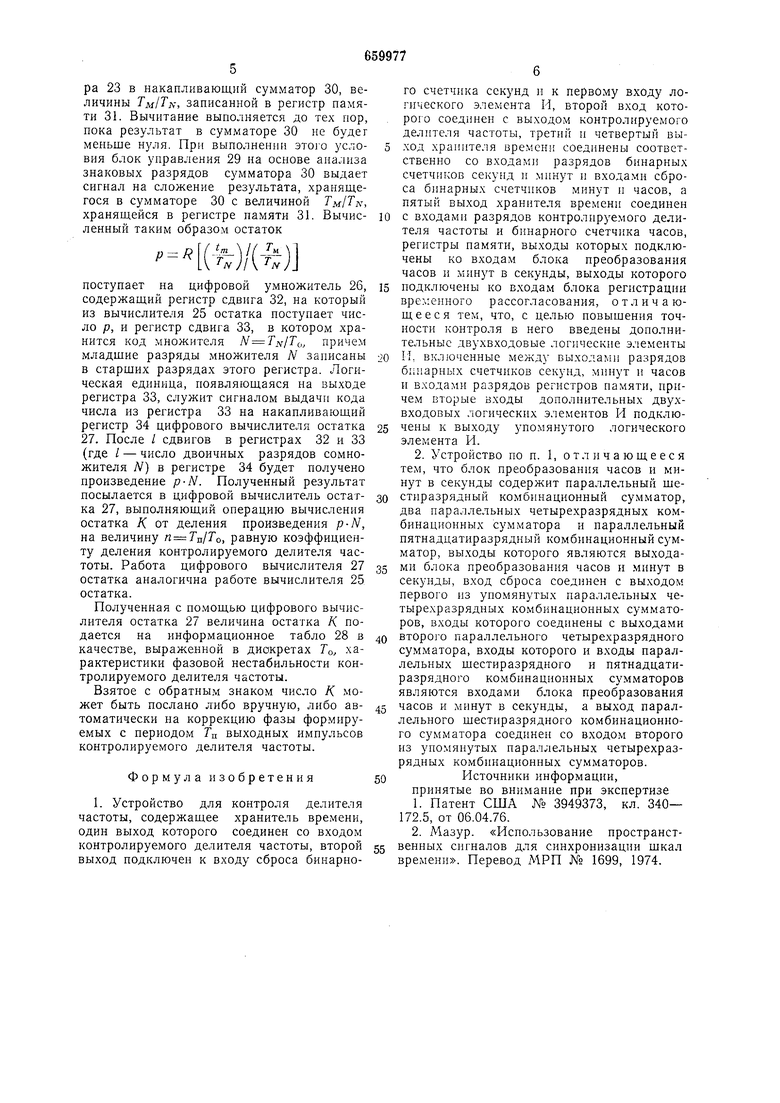

На фиг. 1 показана структурная электрическая схема предлагаемого устройства; на фиг. 2 - структурная электрическая схема цифрового вычислителя остатка.

Устройство контроля работы делителя частоты по импульсным сигналам хранителя времени содержит контролируемый делитель частоты 1, хранитель времени 2, формируюший импульсные сигналы с периодом повторения TQ, TN секунда, Гл-+1 1 минута, Гл-+2 1 ч и Гл-+з 24 часа, логический элемент И 3, бинарные счетчики секунд 4, минут 5 емкостью шесть двоичных разрядов, служаш,ие для подсчета чисел секундных и минутных импульсных сигналов на выходе хранителя времени, а также соединенный с хранителем времени бинарный счетчик часов 6 емкостью пять двоичных разрядов, предназначенный для подсчета формируемых хранителем времени часовых импульсов; двухвходовые логические элементы И 7- 15 и регистры памяти секунд 16, минут 17 и часов 18; блок преобразования чисел часов, минут в секунды 19, состояш,ий из параллельного шестиразрядного комбинационного сумматора 20, двух четырехразрядных комбинационных сумматоров 21, 22 и одного пятнадцати разрядного комбинационного сумматора 23; блок регистрации временного рассогласования 24, состояш,ий из цифрового вычислителя 25 остатка, цифрового умножителя 26, цифрового вычислителя остатка 27, информационного табло 28.

Блок регистрации временного рассогласования 24 (фиг. 2) содержит блок управления 29, накапливаюший сумматор 30, регистр памяти 31, регистры 32, 33 сдвига, накапливающий регистр 34, второй блок управления 35 и регистр памяти 36.

стройство контроля работы делителя частоты по импульсным сигналам хранителя времени работает следующим образом.

Импульсные сигналы, формируемые хранителем времени 2, подаются с периодом Го на вход контролируемого делителя частоты 1, чьи выходные импульсы посылаются С периодом 7„ на вход логического элемента И 3, на второй вход которого поступают с периодом импульсные сигналы от хранителя времени, поступающие также на вход бинарного счетчика секунд 4, сброс которого в нулевое состояние осуществляется формируемым с периодом Гл-+1 1 минута импульсными сигналами хранителя времени 2, которые подаются также и на вход бинарного счетчика минут 5. В свою очередь сброс счетчика минут 5 в нулевое состояние осуществляется импульсными сигналами, имеющими период 1 ч. Эти же сигналы подаются на вход бинарного счетчика часов 6, сброс которого осуществляется сигналами хранителя времени, имеющими период Гл-+з 24 ч. Теми же сигналами производится один раз в сутки в 00 часов 00 минут 00 секунд сброс в нулевое состояние фазы выходных импульсов контролируемого делителя частоты.

Импульсы, появляющиеся с периодом Тм на выходе логического элемента И, поступают на входы двухвходовых логических элементов И 7-15, на вторые входы которых поступают соответствующие коды чисел секунд, минут и часов от бинарных счетчиков 4, 5, 6. В момент появления на выходе логического элемента И 3 импульсного сигнала числа, хранящиеся в бинарных счетчиках 4, 5, 6, перенесутся соответственно в регистры памяти 16, 18. С выходов этих регистров записанные в них числа подаются на входы блока преобразования чисел часов, минут и секунд в секунды 19. В результате на выходе сумматора 23 блока преобразования 19 будет получено выраженное в секундах число tm/Tff из интервала 10,864001, соответствующее моменту времени tm, в который на выходе логического элемента И 3 появляется импульс, фиксирующий совпадение импульсных последовательностей Тп и TfT. Двоичный код величины tmlTff поступает с выхода сумматора 23 на вход цифрового вычислителя 25, входящего в состав блока регистрации временного рассогласования 24. С помощью этого вычислителя определяется остаток ог деления величины im/Tif на выраженную в секундах величину периода совпадений . Величина остатка р определяется путем последовательных вычитаний из числа tm/Тк, переписанного с выхода сумматоpa 23 в накапливающий сумматор 30, величины TM/TN, записанной в регистр памяти 31. Вычитание выполняется до тех пор, пока результат в сумматоре 30 не будет меньше нуля. При выполнении этого уелоВИЯ блок управления 29 на основе анализа знаковых разрядов сумматора 30 выдает сигнал на сложение результата, хранящегося в сумматоре 30 с величиной , хранящейся в регистре памяти 31. Вычисленный таким образом остаток ) поступает на цифровой умножитель 26, содержащий регистр сдвига 32, на который из вычислителя 25 остатка поступает число р, и регистр сдвига 33, в котором хранится код множителя N (,, причем младшие разряды множителя Л записаны в старших разрядах этого регистра. Логическая единица, появляющаяся на выходе регистра 33, служит сигналом выдачи кода числа из регистра 33 на накапливающий регистр 34 цифрового вычислителя остатка 27. После / сдвигов в регистрах 32 и 33 (где / - число двоичных разрядов сомножителя Л) в регистре 34 будет получено произведение p-N. Полученный результат посылается в цифровой вычислитель остатка 27, выполняющий операцию вычисления остатка К от деления произведения p-N, на величину п Тп/То, равную коэффициенту деления контролируемого делителя частоты. Работа цифрового вычислителя 27 остатка аналогична работе вычислителя 25 остатка. Полученная с помощью цифрового вычислителя остатка 27 величина остатка К. подается на информационное табло 28 в качестве, выраженной в дискретах То, характеристики фазовой нестабильности контролируемого делителя частоты. Взятое с обратным знаком число /С может быть послано либо вручную, либо автоматически на коррекцию фазы формируемых с периодом Гц выходных импульсов контролируемого делителя частоты. Формула изобретения 1. Устройство для контроля делителя частоты, содержащее хранитель времени, один выход которого соединен со входом контролируемого делителя частоты, второй выход подключен к входу сброса бинарного счетчика секунд и к первому входу логического элемента И, второй вход которого соединен с выходом контролируемого делителя частоты, третий и четвертый выход хранителя времени соединены соответственно со входами разрядов бинарных счетчиков секунд и минут и входами сброса бинарных счетчиков минут и часов, а пятый выход хранителя времени соединен с входами разрядов контролируемого делителя частоты и бинарного счетчика часов, регистры памяти, выходы которых подключены ко входам блока преобразования часов и минут в секунды, выходы которого подключены ко входам блока регистрации временного рассогласования, отличающееся тем, что, с целью повышения точности контроля в него введены дополнительные двухвходовые логические элементы И, включенные между выходами разрядов бшшрных счетчиков секунд, минут и часов и входами разрядов регистров памяти, причем вторые входы дополнительных двухвходовых логических элементов И подключены к выходу упомянутого логического элемента И. 2. Устройство по п. 1, отличающееся тем, что блок преобразования часов и минут в секунды содержит параллельный шестиразрядный комбинационный сумматор, два параллельных четырехразрядных комбинационных сумматора и параллельный пятнадцатиразрядный комбинационный сумматор, выходы которого являются выходами блока преобразования часов и минут в секунды, вход сброса соединен с выходом первого из упомянутых параллельных четырехразрядных комбинационных сумматоров, входы которого соединены с выходами второго параллельного четырехразрядного сумматора, входы которого и входы параллельных шестиразрядного и пятнадцатиразрядного комбинационных сумматоров являются входами блока преобразования часов и минут в секунды, а выход параллельного шестиразрядного комбинационного сумматора соединен со входом второго из упомянутых параллельных четырехразрядных комбинационных сумматоров. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3949373, кл. 340- 172.5, от 06.04.76. 2.Мазур. «Использование пространственных сигналов для синхронизации шкал времени. Перевод МРП № 1699, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь позиционного кода с одним основанием в позиционный код с другим основанием | 1977 |

|

SU734667A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Система отсчета точного времени | 1976 |

|

SU648936A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Устройство для распознавания контуров изображений | 1983 |

|

SU1156103A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ШКАЛЫ ВРЕМЕНИ | 1995 |

|

RU2082216C1 |

| Устройство для контроля времени работы объекта | 1987 |

|

SU1430976A1 |

| Устройство для сопряжения вычислительного комплекса накопителей на магнитной ленте | 1983 |

|

SU1142839A1 |

| Устройство для приема дискретной информации | 1989 |

|

SU1619326A1 |

| Устройство для контроля времени работы объекта | 1989 |

|

SU1667125A1 |

Авторы

Даты

1979-04-30—Публикация

1976-09-28—Подача